半导体器件芯片、其制造方法、半导体器件及电子设备与流程

- 国知局

- 2024-07-31 19:07:34

本发明涉及半导体工艺制造领域,具体涉及一种具有门极沟槽结构的半导体器件芯片、其制造方法及采用其的半导体器件及电子设备。

背景技术:

1、igct(integrated gate commutated thyristor,集成门极换流晶闸管)是一种新型高压高功率的电力电子器件,具有高压、大电流、低压降等优点,被广泛应用于电力电子领域。igct作为一种门极可控制关断的开关器件,兼具gto与igbt的优点,其关断特性如晶体管,而开通特性像晶闸管,具有阻断电压高、功率容量大、通态损耗低、无需关断吸收电路、易于串并联等特性。因集成低感门极驱动单元,用户只需配置相应的门驱电源、完成散热器压装及导电排连接、配备合适控制策略的控制器即能应用,可节约变流器的开发成本、缩短开发周期,方便应用和维护工作。

2、传统的igct器件门极结构在高压、高频率、大电流等工作条件下存在一些局限性,如开关速度慢、漏电流大、电流承受能力低等。

3、中国专利cn112599587b披露了一种具有缓冲层结构的半导体器件,包括依次设置的第一掺杂剂区域、第二掺杂剂区域、第三掺杂剂区域,还包括择一或多个组合设置的上掺杂剂区域、下掺杂剂区域、中部掺杂剂区域;所述上掺杂剂区域位于第一掺杂剂区域和第二掺杂剂区域之间;所述下掺杂剂区域位于第二掺杂剂区域和第三掺杂剂区域之间;所述中部掺杂剂区域位于第二掺杂剂区域中间,由此能够实现较小的漏电流,提高器件的耐压能力,以及可运行的最高结温,增大器件的通流能力。但是该工艺需要多次掺杂,制备成本高且工艺复杂,加工时间长。

4、中国专利申请cn108598150a披露了一种横向变掺杂-结终端延伸复合终端结构,以gct为例,终端区和有源区有共同的n-衬底及其下方的n型fs层、p+阳极区及阳极电极;在有源区主结的外侧,依次设置有一个电阻区、一个横向变掺杂区和一个结终端延伸区,且该横向变掺杂区与结终端延伸区相互交叠,终端区表面覆盖有两层钝化膜;该电阻区将主结和该复合终端区连接为一体。该申请的复合终端结构,可获得约91%的耐压效率,高温漏电流小、终端稳定性高,而且制作工艺与有源区完全兼容。但是该工艺主要解决漏电流和耐压的问题,并未涉及开关速度的问题。

5、对于现有技术的现状,本发明人经过深入研究,创新性地提出了一种半导体器件芯片及其制造方法。

技术实现思路

1、有鉴于此,本发明的主要目的在于提供一种半导体器件芯片、其制造方法及采用其的半导体器件及电子设备,以期至少部分地解决上述技术问题。

2、为了实现上述目的,作为本发明的第一个方面,提出了一种半导体器件芯片,所述半导体器件芯片包括门极,所述门极上具有沟槽结构;

3、其中,所述半导体器件芯片是晶闸管,或电子和空穴均以扩散原理导通的双极半导体器件的芯片。

4、作为本发明的第二个方面,还提出了一种半导体器件芯片的制造方法,包括如下步骤:

5、在形成门极之后,在所述门极上进一步通过图形化工艺在所述门极上制备出所需的沟槽结构;

6、其中,所述半导体器件芯片是晶闸管,或者电子和空穴均以扩散原理导通的双极半导体器件的芯片。

7、作为本发明的第三个方面,还提出了一种基于如上所述的半导体器件芯片的制造方法制备得到的半导体器件芯片。

8、作为本发明的第四个方面,还提出了一种包括如上所述的半导体器件芯片的半导体器件。

9、作为本发明的第五个方面,还提出了一种包括如上所述的半导体器件的电子设备。

10、基于上述技术方案可知,本发明的半导体器件芯片及其制造方法,相对于现有技术,主要区别在于门极沟槽结构,根据仿真计算,本发明提出的现有芯片在开关速率、大电流关断、门极寄生参数优化、门极均流等至少一个方面有显著的提升效果:

11、(1)经过仿真计算,门极关断时间可减小10%到50%,本发明的门极沟槽结构,将门极关断时间减小了1.3μs,减小20%;本发明可有效提升器件的开关速率,提高了器件的灵活性和工作频率;

12、(2)门极下方在电流关断时的电场集中效应也得到显著改善,电场峰值下降了15%,说明对于雪崩效应有所改善,并且可降低热损耗;

13、(3)由于沟槽门极结构的存在,其门极互连金属的厚度相比传统gct器件得到增加,甚至达到数倍,因此门极汇流过程中的寄生电感的参数也将明显降低,汇流能力也明显增大,甚至达到数倍,提高了器件的安全工作区,提升了安全可靠性;

14、(4)由于沟槽结构的引入,导致门极电极在深度和互连厚度方面的增加,使得器件在均流能力方面也得到显著改善,并可更加快速的导出p-n-结界面载流子复合过程所产生的热积累,因此也可提升器件的工作结温。

技术特征:1.一种半导体器件芯片,其特征在于,所述半导体器件芯片包括门极,所述门极上具有沟槽结构;

2.根据权利要求1所述的半导体器件芯片,其特征在于,所述半导体器件芯片是gct、igct、gto、gtr、mct或mto型半导体器件的芯片;和/或

3.根据权利要求1所述的半导体器件芯片,其特征在于,所述沟槽结构的横截面形状为由若干条直线或曲线组成的图形;和/或

4.根据权利要求3所述的半导体器件芯片,其特征在于,所述沟槽结构是横截面是规则排列的矩形、圆形、六边形或十字形的阵列。

5.根据权利要求1所述的半导体器件芯片,其特征在于,所述半导体器件芯片包括若干元胞,每一个元胞中包括一组门极,每一组门极只包含一组门极沟槽结构。

6.根据权利要求5所述的半导体器件芯片,其特征在于,所述一组门极沟槽结构包括单个沟槽结构或组成一个阵列的多个沟槽结构,其中组成阵列的多个沟槽结构之间彼此不连通。

7.根据权利要求1所述的半导体器件芯片,其特征在于,

8.根据权利要求7所述的半导体器件芯片,其特征在于,当进行了金属掺杂或填充操作时,所使用的掺杂或填充的金属选自金、银、铜、钛、镍、铝、铝硅铜、钛镍银;和/或

9.根据权利要求1所述的半导体器件芯片,其特征在于,所述半导体器件芯片还包括n-漂移区和形成在n-漂移区双面的p-区和p+区,其中p+区形成在p-区背对n-漂移区的一面上;所述半导体器件芯片还包括阴极和阳极,其中,门极形成在一面的p+区上,阴极形成在同面p+区上形成的高台结构上,阳极形成在n-漂移区另一面的p+区上。

10.根据权利要求9所述的半导体器件芯片,其特征在于,

11.根据权利要求10所述的半导体器件芯片,其特征在于,双面的p-区的掺杂浓度纵向缓变,深度范围为5-200μm;和/或

12.根据权利要求9所述的半导体器件芯片,其特征在于,

13.根据权利要求9所述的半导体器件芯片,其特征在于,在门极和阴极之间还包括一钝化介质层,即门阴极介质层;制备所述门阴极介质层的材料选自二氧化硅、氮化硅、磷硅玻璃、硼硅玻璃、硼磷硅玻璃。

14.根据权利要求13所述的半导体器件芯片,其特征在于,所述门阴极介质层的厚度大于0.1μm,厚度不均匀性≤5%。

15.根据权利要求9所述的半导体器件芯片,其特征在于,

16.根据权利要求15所述的半导体器件芯片,其特征在于,金属电极层的厚度为0.5-60μm,厚度不均匀性≤10%。

17.根据权利要求9所述的半导体器件芯片,其特征在于,所述半导体器件芯片还包括有源区的pi胶钝化层,用于覆盖除阴极的高台结构上的金属电极层以外的所有区域。

18.根据权利要求17所述的半导体器件芯片,其特征在于,所述pi胶钝化层通过光敏型或非光敏型pi胶来制备;

19.根据权利要求9所述的半导体器件芯片,其特征在于,所述半导体器件芯片还包括终端结构。

20.根据权利要求19所述的半导体器件芯片,其特征在于,所述终端结构包括斜角结构,所述斜角结构具有单斜角、双斜角或多斜角。

21.根据权利要求20所述的半导体器件芯片,其特征在于,所述斜角覆盖并穿过双面的p-n-界面,斜角角度及造型根据半导体器件的电压阻断需求及终端结构尺寸确定。

22.根据权利要求19所述的半导体器件芯片,其特征在于,所述终端结构还包括表面钝化层,制备所述表面钝化层的材料选自pi胶、类金刚石碳、氧化硅、氮化硅。

23.一种半导体器件芯片的制造方法,其特征在于,包括如下步骤:

24.根据权利要求23所述的制造方法,其特征在于,所述半导体器件芯片是gct、igct、gto、gtr、mct或mto型半导体器件的芯片。

25.根据权利要求23所述的制造方法,其特征在于,

26.根据权利要求25所述的制造方法,其特征在于,金属掺杂或填充所使用的金属选自金、银、铜、钛、镍、铝、铝硅铜、钛镍银;和/或

27.一种半导体器件芯片,其特征在于,所述半导体器件芯片是通过如权利要求23-26任一项所述的半导体器件芯片的制造方法来制备。

28.一种半导体器件,其特征在于,所述半导体器件包括如权利要求1-22、27任一项所述的半导体器件芯片。

29.一种电子设备,其特征在于,所述电子设备包括如权利要求28所述的半导体器件。

30.根据权利要求29所述的电子设备,其特征在于,所述电子设备为整流器、换流器、逆变器、功率开关或切换电路设备。

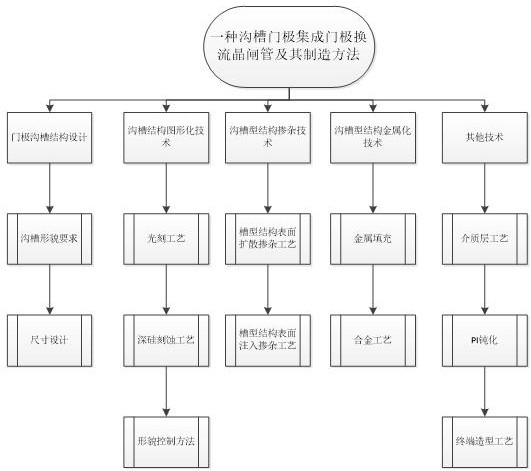

技术总结一种半导体器件芯片、其制造方法、半导体器件及电子设备,属于功率半导体器件制造领域。所述半导体器件芯片包括门极,所述门极上具有不同于沟槽栅和隔离沟槽的沟槽结构;所述半导体器件芯片为电子和空穴均以扩散原理导通的双极半导体器件芯片,或者晶闸管芯片。本发明的具有门极沟槽结构的半导体器件可以解决如开关速度慢、漏电流大、电流承受能力低等至少一个技术问题,在开关速率、大电流关断、门极寄生参数优化、门极均流等至少一个方面有显著的提升效果,门极关断时间可减小10%到50%,电场峰值下降了15%,门极汇流过程中的寄生电感的参数也明显降低,汇流能力明显增大。技术研发人员:吴沛飞,魏晓光,李玲,刘瑞,王耀华,焦倩倩,张语,姬世宇,孙宁飞受保护的技术使用者:北京怀柔实验室技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181701.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表