编程电压产生电路的制作方法

- 国知局

- 2024-07-31 19:14:53

本发明涉及一种半导体集成电路,特别是涉及一种编程电压产生电路。

背景技术:

1、如图1所示,是现有闪存的存储单元101的电路结构示意图;如图2所示,是现有闪存的存储单元101的剖面结构示意图;现有闪存包括多个存储单元101,由多个所述存储单元101排列形成闪存的阵列结构。

2、各所述存储单元101都采用分离栅浮栅器件。

3、如图2所示,所述分离栅浮栅器件包括:对称的第一源漏区205a和第二源漏区206,位于所述第一源漏区205a和所述第二源漏区205b之间的多个分离的具有浮栅104的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构103;所述第一栅极结构中具有位于所述浮栅104顶部的控制栅105。

4、所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个,分别用标记102a和102b表示。

5、所述分离栅浮栅器件为n型器件,所述第一源漏区205a和所述第二源漏区205b都由n+区组成。

6、p型掺杂的沟道区位于所述第一源漏区205a和所述第二源漏区205b之间且被各所述第一栅极结构和所述第二栅极结构103所覆盖。所述第一源漏区205a和所述第二源漏区205b都形成于p型半导体衬底201且和对应的两个所述第一栅极结构的外侧面自对准,所述沟道区之间由所述第一源漏区205a和所述第二源漏区205b之间的所述p型半导体衬底201组成或者进一步在所述p型半导体衬底201上进行掺杂形成。

7、所述存储单元101的所述第二源漏区205b连接到第二源漏电极,第二源漏电极会连接到位线bl1。

8、所述存储单元101的所述第一源漏区205a连接第一源漏电极,第一源漏电极会连接到位线bl0。

9、所述第一源漏电极和所述第二源漏电极为完全对称的结构,所述存储单元101的源极为所述第一源漏电极和所述第二源漏电极中的一个,漏极为所述第一源漏电极和所述第二源漏电极中的另一个,具体根据实际使用过程中所加电位来确定。

10、各所述第一栅极结构由隧穿介质层202、所述浮栅104、控制栅介质层203和所述控制栅105叠加而成。

11、各所述第二栅极结构103由字线栅介质层204和字线栅106叠加而成。

12、所述控制栅105连接到对应的控制栅线,所述字线栅106连接到字线wl。图1中,所述存储单元101包括两个所述第一栅极结构,故所述控制栅线也包括两根,分别用cg0和cg1表示,第一栅极结构102a的所述控制栅105连接到控制栅线cg0,第一栅极结构102b的所述控制栅105连接到控制栅线cg1。

13、对所述存储单元101的选定存储位进行编程(program)时,以对图2中所述第一栅极结构102a中的浮栅104对应的存储位即存储位‘a’为选定存储位为例,所加电压如表一所示,包括:

14、所述控制栅线cg1接5v,用于将第一栅极结构102b所控制的沟道区的区域段打开即导通;

15、所述字线wl接1.4v,用于将所述第二栅极结构103所控制的沟道区的区域段打开;

16、位线bl1接编程电流idp。此时所述位线bl1所对应的所述第二源漏电极作为源极,而所述位线bl0所对应的所述第一源漏电极则作为漏极。

17、控制栅线cg0接9v的高压,位线bl0接4v的高压,这样,编程电流经过所述第一栅极结构102b和所述第二栅极结构103所控制的沟道区的区域段到达所述第一栅极结构102a的底部之后,由于控制栅线cg0和所述位线bl1都是高压,故能实现源端热电子注入编程。

18、表一

19、

20、如图3所示,是现有存储器的编程电压产生电路的电路图;现有存储器的编程电压产生电路是用于提高所述字线栅wl的编程电压vwlp,现有存储器的编程电压产生电路包括:

21、比较器301,+输入端连接参考电压vref,-输入端连接反馈电压,输出端输出编程电压vwlp。反馈电压由分压电阻串302对编程电压vwlp进行分压得到。

22、由图3所示可知,编程电压vwlp会钳位在参考电压vref上,为一固定电压。

23、但是,存储器即闪存中,所述字线栅106所覆盖区域的沟道区的第一阈值电压即vtwl实际上会有较大漂移,也即第一阈值电压的实际值实际上在设计值的基础上产生偏差,这是由存储器的制造工艺或应用环境如温度决定的,不可避免。而且由于所述存储器上包括多个存储单元,各存储单元的第一阈值电压的漂移大小也会不同,在同一所述存储器上,所述存储单元的第一阈值电压的漂移范围可达0.7v~1.5v。而编程电压vwlp固定时,当第一阈值电压的漂移到较大值时,则会编程失败,例如vwlp为1.4v,而vtwl确为1.5v时,则无法所述字线栅106所控制的沟道区无法导通,从无法实现编程。

技术实现思路

1、本发明所要解决的技术问题是提供一种编程电压产生电路,能使编程电压根据各存储单元的实际的字线栅的第一阈值电压变化,使得存储器中的各存储单元的字线栅的第一阈值电压即使发生较大的漂移,也能保证编程电压比漂移后的第一阈值电压大,从而能极大的提高编程窗口。

2、为此解决上述技术问题,本发明提供的编程电压产生电路中,编程电压用于在编程时提供给存储器的存储单元的字线栅;编程电压产生电路包括:

3、第一电压产生单元,输入端连接参考电压,输出端输出所述编程电压,所述参考电压的大小可调,所述编程电压的大小根据所述参考电压的大小设置。

4、检测电路,用于检测所述编程电压和所述存储单元的字线栅的第一阈值电压的第一差值并根据所述第一差值的大小输出一个检测信号。

5、控制电路,用于根据所述检测信号调节并选定所述编程电压的大小,使所述第一阈值电压产生漂移时,选定的最终编程电压也同步变化并满足所述存储单元的编程要求。

6、进一步的改进是,所述控制电路通过调节所述参考电压的大小并从而调节所述编程电压的大小;所述控制电路对所述编程电压进行从小到大的调节,在调节过程中,如果所述检测信号不符合要求,则继续增加所述编程电压;如果所述检测信号符合要求,则将对应的所述编程电压作为所述存储单元的最终编程电压。

7、进一步的改进是,所述检测电路中,当所述第一差值大于等于所述第一要求值时,所述检测信号具有第一电平值,所述检测信号符合要求;当所述第一差值小于所述第一要求值时,所述检测信号具有第二电平值,所述检测信号不符合要求。

8、进一步的改进是,所述第一电平值为高电平,所述第二电平值为低电平。

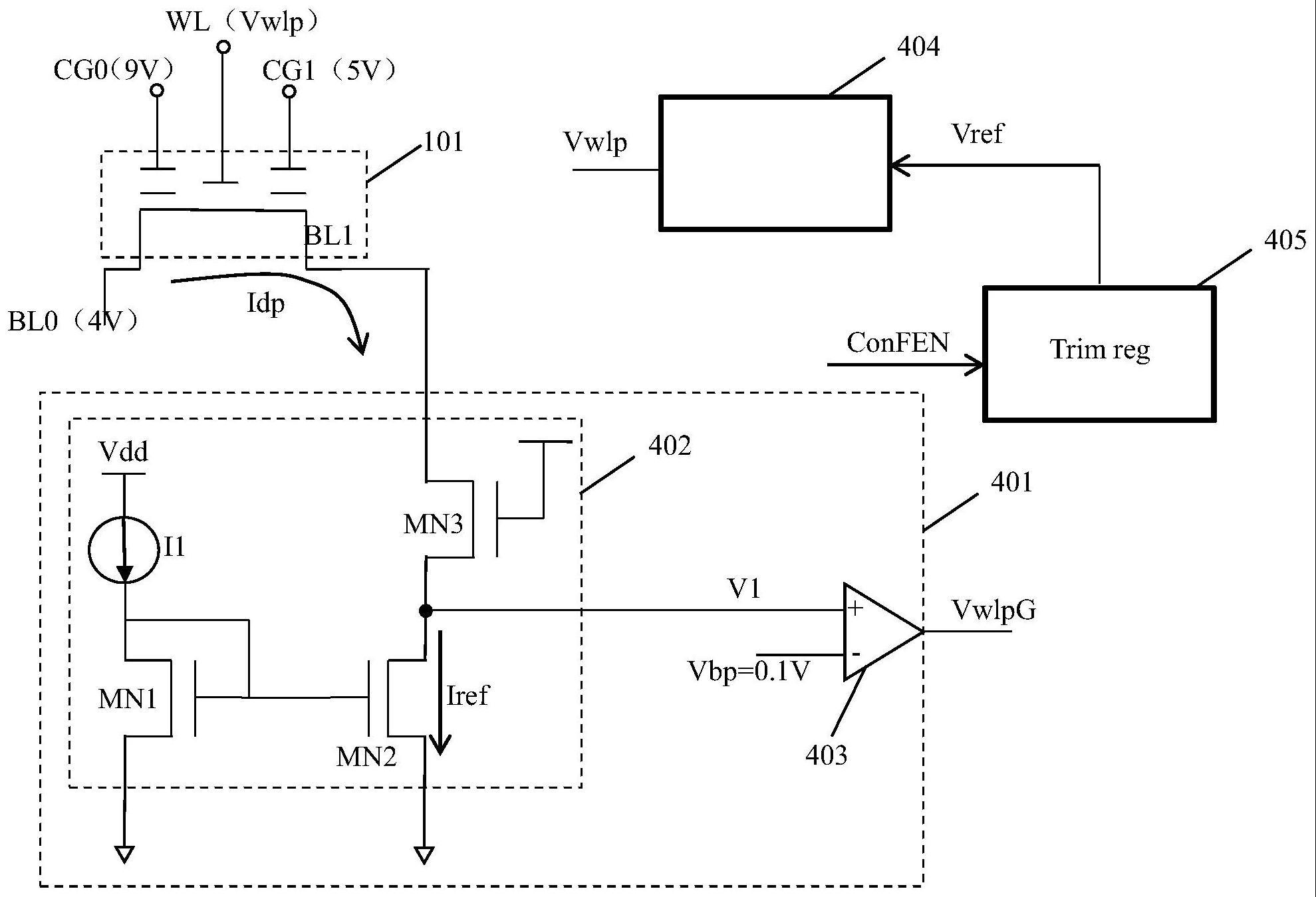

9、进一步的改进是,所述检测电路包括第一电流比较器和第一电压比较器。

10、所述第一电流比较器用于对所述存储单元的编程电流和第一参考电流进行比较并形成第一电压信号;所述存储单元按照编程过程的要求加电压,在所述编程过程中,所述字线栅加所述编程电压,所述存储单元的漏极接第二编程电压,所述存储单元的源极输出所述编程电流;所述编程电流的大小由所述第一差值确定并使所述第一电压大小由所述第一差值确定。

11、所述第一电压比较器的第一输入端连接所述第一电压信号以及第二输入端连接第二要求值,所述第二比较器的输出端输出所述检测信号。

12、进一步的改进是,所述第一电压信号等于所述第一差值,所述第二要求值等于所述第一要求值。

13、进一步的改进是,所述第一参考电流由第一电流镜像电路提供,所述第一电流镜像电路包括:第一nmos管、第二nmos管和第一电流源。

14、所述第一nmos管的源极和所述第二nmos管的源极都接地。

15、所述第一nmos管的栅极和源极以及所述第二nmos管的栅极连接在一起。

16、所述第一电流源连接在电源电压和所述第一nmos管的漏极之间。

17、所述第二nmos管的漏极输出所述第一参考电流。

18、进一步的改进是,所述第一电流比较器还包括第三nmos管。

19、所述第三nmos管的栅极接偏置电压。

20、所述第三nmos管的漏极连接所述存储单元的源极。

21、所述第三nmos管的源极连接所述第二nmos管的漏极。

22、进一步的改进是,所述参考电压具有多个第一档位值,所述控制电路通过调节所述第一档位值调节所述参考电压的大小。

23、进一步的改进是,所述参考电压的各所述第一档位值存储在修整寄存器(trimreg)中,通过第一数字信号选择所述第一档位值。

24、进一步的改进是,所述第一电压产生单元包括第二电压比较器和分压电路。

25、所述第二电压比较器的第一输入端连接所述参考电压、第二输入端连接反馈电压以及输出端输出所述编程电压。

26、所述分压电路连接在所述编程电压和地之间,所述反馈电压为由所述分压电路提供的所述编程电压的分压。

27、进一步的改进是,所述分压电路为一电阻串。

28、进一步的改进是,所述存储器上包括多个所述存储单元,各所述存储单元的所述第一阈值电压相对于设计值有漂移。

29、进一步的改进是,所述存储器上的所有所述存储单元的所述第一阈值电压的漂移范围为0.7v~1.5v。

30、进一步的改进是,所述存储单元采用分离栅浮栅器件。

31、所述分离栅浮栅器件包括:第一源漏区和第二源漏区,位于所述第一源漏区和所述第二源漏区之间的多个分离的具有浮栅的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构;所述第一栅极结构中具有位于所述浮栅顶部的控制栅。

32、所述第二栅极结构作为所述字线栅,所述第一栅极结构作为存储栅。

33、所述第二源漏区连接到由金属层组成的所述第二源漏电极。

34、所述第一源漏区连接到由金属层组成的所述第一源漏电极。

35、进一步的改进是,所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个。

36、进一步的改进是,所述分离栅浮栅器件为n型器件,所述第一源漏区和所述第二源漏区都由n+区组成。

37、p型掺杂的沟道区位于所述第一源漏区和所述第二源漏区之间且被各所述第一栅极结构和所述第二栅极结构所覆盖。

38、本发明通过设置检测电路能对编程电压和存储单元的字线栅的第一阈值电压的第一差值进行检测并根据检测信号来调整并选定编程电压的大小,最后使得选定的最终编程电压会大于第一阈值电压,从而能保证对存储单元实现良好编程,这样,即使存储单元的第一阈值电压的实际值会相对设定值有偏移,而由于最终编程电压是根据存储单元的第一阈值电压的实际值的比较来得到的,所以能保证最终编程电压符合存储单元的编程要求,所以,本发明能使编程电压根据各存储单元的实际的字线栅的第一阈值电压变化,使得存储器中的各存储单元的字线栅的第一阈值电压即使发生较大的漂移,也能保证编程电压比漂移后的第一阈值电压大,从而能极大的提高编程窗口。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182018.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种线性忆阻器的等效电路

下一篇

返回列表