负压放电电路的制作方法

- 国知局

- 2024-07-31 19:16:02

本发明涉及一种半导体集成电路,特别是涉及一种负压放电电路。

背景技术:

1、存储器如闪存(flash)包括多种操作,如编程(program)、擦除(erase)和读取操作,在存储器的操作中需要采用高于电源电压的正电压或者采用0v以下的负电压即负压,正电压也简称正压,负电压也简称负压。正压和负压都需要采用电荷泵提供。

2、如图1所示,是现有闪存同时采用正压和负压的结构示意图;正压电荷泵102提供正压vep到闪存的存储器阵列101,负压电荷泵103提供负压vneg到闪存的存储器阵列101。

3、正压vep或负压vneg仅是在操作过程中需要采用时提供,当操作完成后,正压vep对应的信号线需要放电到一个目标电压如0v,负压vneg对应的信号线也需要放电到一个目标电压如0v。正压vep和负压vneg的放电分别需要正压放电电路和负压放电电路实现。

4、如图2a所示,是现有正压放电电路图;正压放电电路104包括放电路径105和106,其中,放电路径105的放电电流由电流源109a控制,电流源109a的控制端则连接控制信号rmpdn,控制信号rmpdn是在闪存的操作结束后产生。这样,放电开始时,放电路径105会导通,从而形成放电电流并放电。

5、电流源109a的第一端和正压vep对应的信号线之间连接有二极管连接的nmos管n102c和102d;电流源109a的第二端接地。

6、放电路径106则包括由nmos管n101形成的开关,nmos管n101的源极接地,栅极连接控制信号hvlow,漏极和负压vneg的信号线之间连接有二极管连接的nmos管n102a和102b。

7、控制信号hvlow和正压vep的信号线的放电过程相关,当正压vep的信号线的电压从正压vep放电到一个设定电压时,控制信号hvlow有效并使放电路径106导通,从而开始采用放电路径106放电。

8、故控制信号hvlow需要对正压vep的信号线的电压进行取样并进行比较得到,图2中,取样电路107采用电阻串形成,电阻串的输出端输出正压vep的信号线的电压的分压。比较电路采用比较器108形成,电阻串输出的分压输入到比较器108的正相输入端,比较器108的反相输入端会和参考电压连接,比较器108的输出端输出控制信号hvlow。

9、图3a中显示了控制信号rmpdn和hvlow的波形图。

10、图3b中显示了正压vep的波形曲线也即正压vep对应的信号线的电压波形曲线,正压vep对应的信号线在操作之前为0v,在操作过程中上升为正压vep,之后,从正压vep开始下降,从正压vep开始下降的过程即为放电过程,放电过程包括由控制信号rmpdn控制的第一下降阶段,以及由控制信号hvlow控制的第二下降阶段,两个下降阶段用虚线分开,可以看出,两个下降阶段的放电速率会有不同。

11、如图2b所示,是现有负压放电电路图;负压放电电路110包括放电路径111和112,其中,放电路径111的放电电流由电流源109b控制,电流源109b的控制端则连接控制信号rmpdn。由放电路径111和图2a中现有正压放电电路104的放电路径105的控制信号都为信号rmpdn,故放电路径111也会在放电开始时导通。

12、电流源109b的第一端和负压vneg的信号线之间连接由二极管连接的nmos管n102e和102f。

13、电流源109b的第二端接地。

14、放电路径112包括由nmos管n105组成的开关管,nmos管n105的栅极也连接控制信号hvlow。nmos管n105的源极连接负压vneg的信号线,nmos管n105的漏极和nmos管n104的漏极以及nmos管n103的栅极和漏极连接。

15、nmos管n104的栅极连接固定的偏置电压如0v或者vdd,图2b中,采用0/vdd表示,nmos管n104的源极接地。nmos管n104的沟道会保持为导通状态。当控制信号hvlow使nmos管n105导通后,负压vneg的信号线会通过nmos管n105和104放电。

16、nmos管n103的源极连接接地。当放电过程中产生过冲时,负压vneg的信号线的电压会高于0v,由于nmos管n103的栅极和漏极会连接到负压vneg的信号线,故nmos管n103的栅极和漏极也会升高,这样,nmos管n103会导通,并从而使负压vneg的信号线降低,从而使过冲电压降低。

17、现有技术中,图2b所示的现有负压放电电路的两个控制信号即控制信号rmpdn和hvlow和图2a所示的现有正压放电电路的两个控制信号,这样使得,现有负压放电电路的放电过程也包括两个阶段,图3b中也显示了负压vneg的波形曲线也即负压vneg对应的信号线的电压波形曲线,负压vneg对应的信号线在操作之前为0v,在操作过程中下降为负压vneg,之后,从负压vneg开始上升,从负压vneg开始上升的过程即为放电过程,放电过程包括由控制信号rmpdn控制的第一上升阶段,以及由控制信号hvlow控制的第二上升阶段。

18、在第一上升阶段,放电路径111导通,

19、在第二上升阶段,放电路径112导通,如果不发生过冲,nmos管n103不会导通。但是,在第二上升阶段,负压vneg对应的信号线的电压基本上还是为负压,这样容易使得nmos管n103的n+掺杂的漏区和p型掺杂的衬底之间的pn结为正偏导通,这样容易产生闩锁效应。

技术实现思路

1、本发明所要解决的技术问题是提供一种负压放电电路,能防止产生闩锁效应。

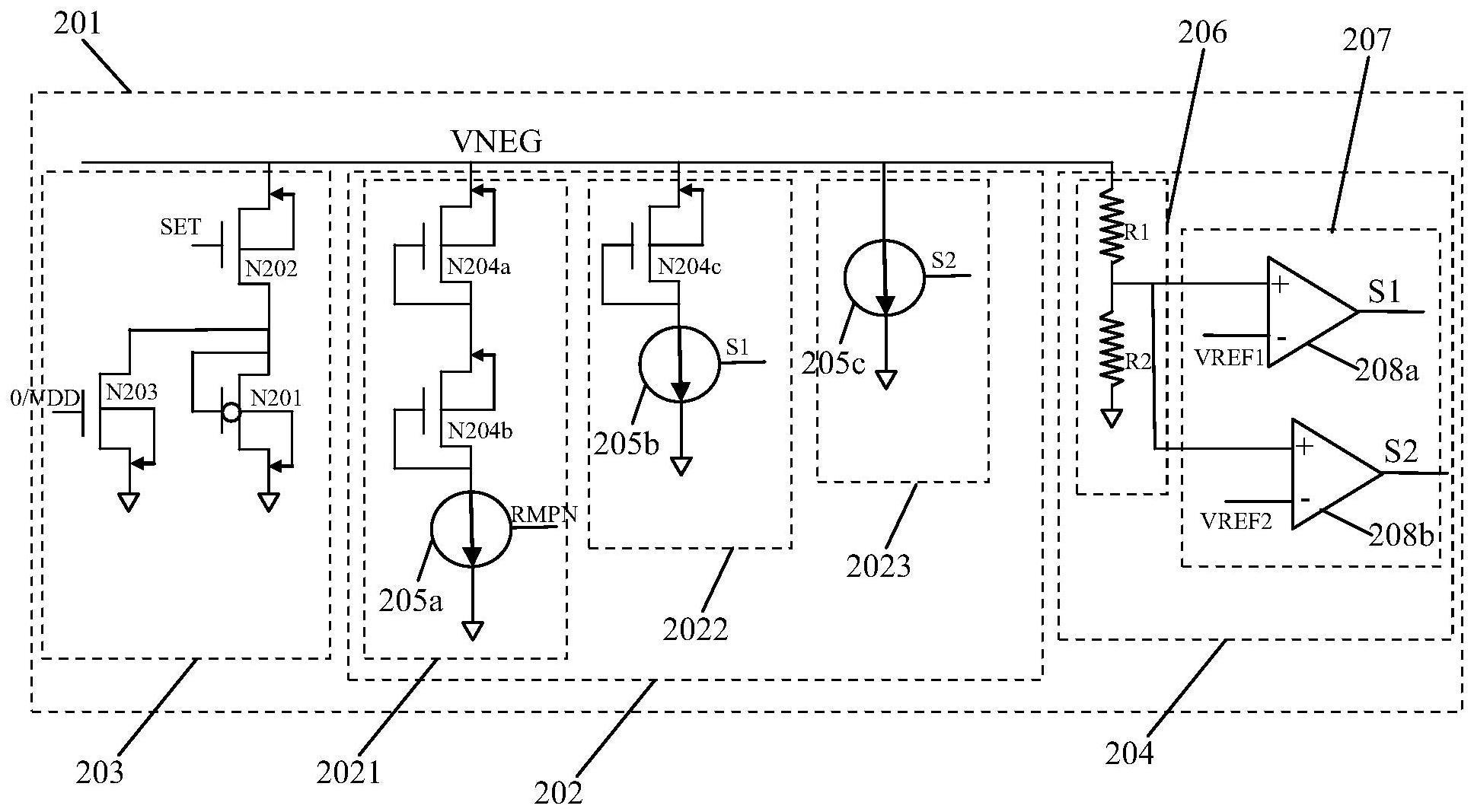

2、为解决上述技术问题,本发明提供的负压放电电路包括:分步放电模块和钳位放电路径。

3、所述分步放电模块连接在第一信号线和第二信号线之间。

4、在放电之前,所述第一信号线的电压为初始负压。

5、所述第二信号线具有目标电压,所述目标电压大于所述初始负压。

6、在放电过程中,所述分步放电模块形成所述第一信号线和所述第二信号线之间的放电电流,所述放电电流被分步控制并使所述第一信号线的电压从所述初始负压开始逐渐升高到小于所述目标电压的第一电压。

7、所述钳位放电路径用于在所述第一信号线的电压到达所述第一电压后将所述第一信号线的电压继续放电到所述目标电压并防止所述第一信号线的电压产生过冲。

8、所述钳位放电路径包括第一开关、第二开关以及第一nmos管。

9、所述第一开关的第一端连接所述第一信号线,所述第一开关的第二端连接所述第二开关的第一端,所述第二开关的第二端连接所述第二信号线。

10、所述第一开关的控制端连接第一控制信号,所述第一控制信号控制所述钳位放电路径的导通和关闭且在所述第一信号线上升到所述第一电压之后使所述钳位放电路径开启。

11、所述第二开关的控制端连接第一偏置电压,所述第一偏置电压使所述第二开关保持导通。

12、所述第一nmos管的栅极和漏极都连接到所述第一开关的第二端,所述第一nmos管的源极连接所述第二信号线;所述第一nmos管的漏区和p型衬底之间具有pn结。

13、在所述钳位放电路径开启放电过程中,当所述第一信号线的电压产生过冲时,所述第一nmos管导通使所述第一信号线的电压回到所述目标电压;所述第一电压设置为小于所述pn结的正偏开启电压,以防止所述pn结正偏导通并从而防止所述第一nmos管产生闩锁效应。

14、进一步的改进是,所述分步放电模块包括多条放电路径。

15、在放电过程中,所述分步放电模块的各所述放电路径根据所述第一信号线的电压大小分步开启从而实现对所述放电电流的分步控制。

16、进一步的改进是,所述分步放电模块的各所述放电路径包括电流源,各所述放电路径的电流源的第二端连接所述第二信号线以及第一端和所述第一信号线之间串联有多个二极管连接的mos晶体管,前一步开启的所述放电路径的所述mos晶体管的数量多余后一步开启的所述mos晶体管的数量。

17、进一步的改进是,最后一步开启的所述放电路径的电流源的第一端直接连接所述第一信号线。

18、进一步的改进是,所述初始负压为闪存的一个操作电压。

19、进一步的改进是,所述初始负压为在擦除操作中加在所述闪存的控制栅线上的擦除电压,所述第一信号线为所述控制栅线。

20、进一步的改进是,所述目标电压为0v,所述第二信号线为接地线。

21、进一步的改进是,所述分步放电模块包括3条放电路径。

22、第一条放电路径的电流源为第一电流源,所述第一电流源的第一端和所述第一信号线之间串联有两个所述mos晶体管。

23、第二条放电路径的电流源为第二电流源,所述第二电流源的第一端和所述第一信号线之间串联有一个所述mos晶体管。

24、第三条放电路径的电流源为第三电流源,所述第三电流源的第一端和所述第一信号线连接。

25、所述第一电流源的控制端连接第二控制信号,所述第二电流源的控制端连接第三控制信号,所述第三电流源的控制端连接第四控制信号。

26、按照时间先后顺序,所述第一条放电路径、所述第二条放电路径和所述第三条放电路径分步开启。

27、进一步的改进是,按照时间先后顺序,所述第一条放电路径、所述第二条放电路径和所述第三条放电路径的放电速率依次变缓。

28、进一步的改进是,负压放电电路还包括形成所述第三控制信号和所述第四控制信号的信号生成电路。

29、进一步的改进是,所述信号生成电路包括取样电路以及比较电路。

30、所述取样电路用于对所述第一信号线的电压进行取样并形成取样电压。

31、所述比较电路用于对所述取样电压和选定的参考电压进行比较并根据比较结果形成所述第三控制信号和所述第四控制信号。

32、当所述第一信号线的电压大于等于第二电压以及小于第三电压时,所述第三控制信号有效并使所述第二电流源导通。

33、当所述第一信号线的电压大于等于所述第三电压以及小于所述第一电压时,所述第四控制信号有效并使所述第三电流源导通。

34、进一步的改进是,所述第二控制信号在放电开始时到所述第一信号线的电压上升到所述第二电压之前有效。

35、进一步的改进是,所述取样电路由连接在所述第一信号线和接地线之间的电阻串组成,所述电阻串的电阻连接处形成输出端并输出所述取样电压。

36、进一步的改进是,所述比较电路包括第一比较器和第二比较器,所述第一比较器的第一输入端连接所述取样电压、第二输入端连接第一参考电压以及输出端输出所述第三控制信号;

37、所述第二比较器的第一输入端连接所述取样电压、第二输入端连接第二参考电压以及输出端输出所述第四控制信号。

38、进一步的改进是,所述第三控制信号的有效电平为高电平,所述第一比较器的第一输入端为正相输入端以及第二输入端为反相输入端。

39、所述第四控制信号的有效电平为高电平,所述第二比较器的第一输入端为正相输入端以及第二输入端为反相输入端。

40、进一步的改进是,各所述放电路径中设置的所述mos晶体管都采用nmos管。

41、进一步的改进是,所述第一开关采用nmos管。

42、所述第二开关采用nmos管,所述第一偏置电压为0v或电源电压。

43、所述第一nmos管采用原生(native)nmos管,原生nmos管的阈值电压接近0v。

44、本发明在负压放电电路中设置有分步放电模块,分步放电模块能将第一信号线的初始负压逐渐增加到接近目标电压的第一电压,之后再采用钳位放电路径进行放电,由于钳位放电路径中具有防过冲的第一nmos管,如果第一电压过低,则容易使第一nmos管的漏区和p型衬底之间形成的pn结正偏导通,从而会产生闩锁效应,但是本发明通过分步放电模块能对第一电压进行很好的控制,从而能防止第一nmos的pn结正偏导通,从而也就能防止产生闩锁效应。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182081.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表