薄膜铁电晶体管的三维NOR存储器串阵列的制作方法

- 国知局

- 2024-07-31 19:50:55

本发明关于高密度存储器结构。特别地,本发明关于由互连薄膜储存元件(例如,薄膜储存晶体管的三维阵列)形成的高密度、低读取潜时存储器结构,包括经组织为nor型存储器串(「nor存储器串」)的存储器结构。

背景技术:

1、nor型存储器串包括储存晶体管,这些储存晶体管共用一共同源极区及一共同汲极区,同时允许各储存晶体管经个别地定址及存取。2018年11月6日发布的题为「capacitive-coupled non-volatile thin-film transistor nor strings in three-dimensional arrays」的美国专利10,121,553(‘553专利)揭示经组织为形成于半导体基板的平坦表面上方的nor存储器串的三维阵列的储存晶体管或存储器晶体管。‘553专利出于所有目的以全文引用的方式并入本文中。在‘553专利中,nor存储器串包括共用一共同位元线及一共同源极线的大量薄膜储存晶体管。特别地,‘553专利揭示nor存储器串,其包括(i)共同源极区及共同汲极区,此两者均沿着水平方向纵向地延伸;以及(ii)用于储存晶体管的闸极电极,其各自沿着竖直方向延伸。在本说明书中,术语「竖直」是指垂直于半导体基板的表面的方向,且术语「水平」是指平行于该半导体基板的表面的任何方向。在三维阵列中,nor存储器串设置于半导体基板上方的多个平面(例如,8或16个平面)上,其中nor存储器串在各平面上配置成列。对于电荷捕获型储存晶体管,数据储存在各储存晶体管中的电荷储存膜中。举例而言,电荷储存膜包括以此次序配置且被称为ono层的穿隧介电层、电荷捕获层及阻挡层,其可实施为包括氧化硅、氮化硅及氧化硅的多层。跨越电荷储存膜的所施加电场添加电荷或自电荷捕获层中的电荷阱去除电荷,由此更改储存晶体管的临限电压以将给定逻辑状态编码至储存晶体管。

2、可电极化材料(「铁电材料」),尤其是用于半导体制造制程中的可电极化材料的进步表明了铁电存储器电路中的新的潜在应用。举例而言,等人在2011国际电子装置会议(2011international electron devices meeting;iedm)公开的论文「ferroelectricity in hafnium oxide:cmos compatible ferroelectric field effecttransistors」(第24.5.1至24.5.4页)揭示了使用氧化铪作为闸极介电材料的铁电场效晶体管(「fefet」)。借由控制铁电闸极介电层中的极化方向,fefet可经程序化以具有两个临限电压中的任一者。fefet的各临限电压构成表示指定逻辑值的一状态,例如「程序化」状态或「抹除」状态。此fefet在高密度存储器电路中具有应用。举例而言,d.v.nirmalramaswamy等人在2013年5月17日申请的题为「apparatuses having a ferroelectricfield-effect transistor memory array and related method」的美国专利申请案第13/897,037号且现为美国专利9,281,044揭示了fefet的三维阵列。

3、然而,先前技术的fefet具有低耐久性。举例而言,k.florent等人在2018ieee国际电子装置会议(2018ieee international electron devices meeting;iedm)公开的论文「vertical ferroelectric hfo2 fet based on 3-d nand architecture:towards denselow-power memory」(第2.5.1至2.5.4页)揭示了仅104个循环的耐久性。此低耐久性使存储器电路实际上不适合用于许多存储器应用。

技术实现思路

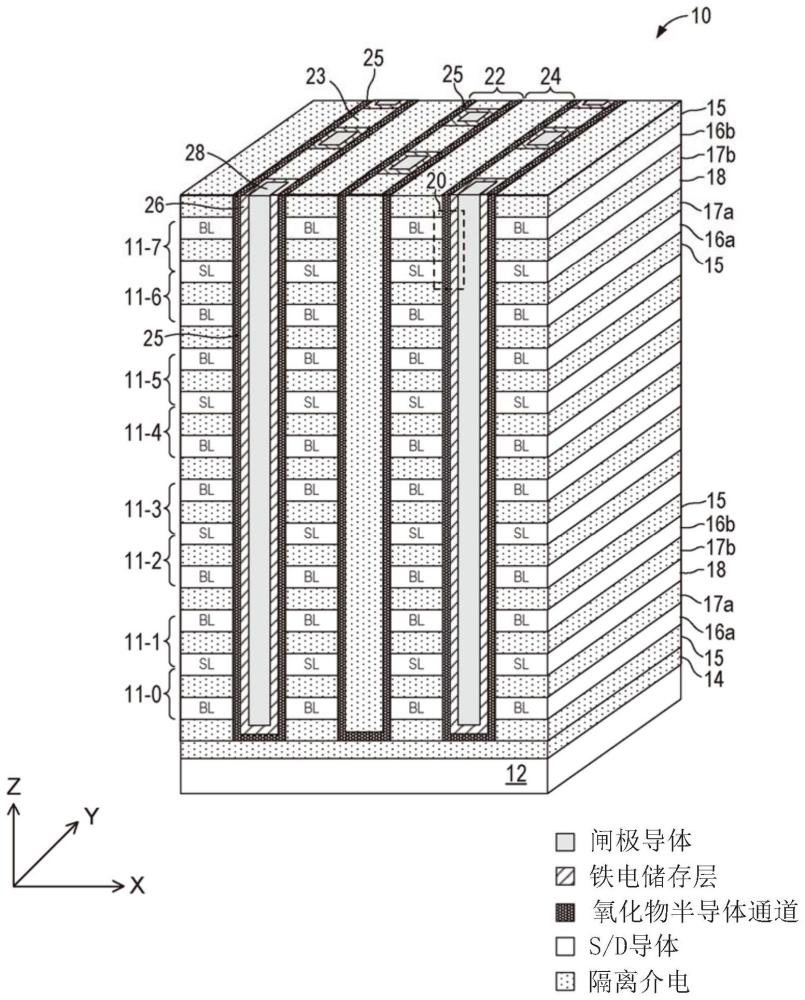

1、在本发明的具体实例中,一种形成于一半导体基板的一平坦表面上方的三维存储器结构包括经组织为沿着实质上平行于该半导体基板的该平坦表面的一第一方向延伸的nor存储器串的多个堆叠的薄膜铁电场效晶体管(fefet)的多个堆叠。各堆叠的nor存储器串沿着实质上垂直于该平坦表面的一第二方向而设置成彼此叠加。各nor存储器串内的这些fefet共用一共同源极层及一共同汲极层,其中各层沿着该第一方向延伸。

2、在一些具体实例中,nor存储器串的各堆叠包括沿着该第二方向而配置成彼此叠加的多个存储器串对,各存储器串对是借由一第一隔离层与其他存储器串对隔离。此外,各存储器串对包含一第一共同汲极层、一第一共同源极层以及一第二共同汲极层,各层是借由一第二隔离层在该第二方向上彼此间隔开配置。此外,各存储器串对包括由该第一共同汲极层及该第一共同源极层形成的一第一nor存储器串,以及由该第二共同汲极层及该第一共同源极层形成的一第二nor存储器串。

3、该存储器结构进一步包括设置成邻近于nor存储器串的各堆叠且与各别堆叠中的这些共同源极层及这些共同汲极层接触的一半导体层。在该第二方向上设置于邻近共同源极层与共同汲极层之间的该半导体层形成用于各别nor存储器串的这些fefet的一通道区。该存储器结构进一步包括设置成邻近于该半导体层且沿着该第二方向延伸的一铁电闸极介电层。最后,该存储器结构进一步包括设置于nor存储器串的邻近堆叠之间且沿着该第二方向延伸的多个导体,各导体充当用于这些邻近堆叠的这些nor存储器串中的各别fefet的一共同闸极电极。在一些具体实例中,该存储器结构可进一步包括在该铁电闸极介电层与形成该通道的该半导体层之间的一介面层。

4、在一些具体实例中,该铁电闸极介电层包括在该第二方向上邻近于各导体而设置为一连续层的一铁电极化层。

5、在另外其他具体实例中,该半导体层沿着nor存储器串的各个各别堆叠的侧壁设置为一连续层。

6、在一些具体实例中,该铁电闸极介电层由一掺杂氧化铪材料形成,且形成该通道区的该半导体层是由一非晶形氧化物半导体材料形成的一氧化物半导体层。

7、在一些具体实例中,该第一共同汲极层及该第二共同汲极层以及该第一共同源极层部分地或实质上由一金属导体材料制成。

8、将自以下描述及图式更充分地理解本发明的此等及其他优势、态样及新颖特征以及其所绘示的具体实例的细节。

技术特征:1.一种三维存储器结构,其形成于半导体基板的平坦表面上方,该存储器结构包含:

2.如权利要求1的存储器结构,其中该铁电闸极介电层包含在该第二方向上邻近于各导体而设置为连续层的铁电极化层。

3.如权利要求1的存储器结构,其中该半导体层包含掺杂n型多晶硅层,且这些铁电场效晶体管各自包含空乏模晶体管,其中该存储器结构进一步包含设置于该n型多晶硅层与该铁电闸极介电层之间的介面介电层。

4.如权利要求3的存储器结构,其中该介面介电层包含氮化硅层及一氧化铝层中的一或多者。

5.如权利要求1的存储器结构,其中该半导体层包含氧化物半导体层。

6.如权利要求5的存储器结构,其中该氧化物半导体层包含氧化铟锌(izo)层及氧化铟镓锌(igzo)层中的一者。

7.如权利要求5的存储器结构,其中该铁电闸极介电层直接接触该氧化物半导体层,其间实质上无介面介电层。

8.如权利要求1的存储器结构,其中该半导体层沿着所述nor存储器串的各个各别堆叠的侧壁设置为连续层。

9.如权利要求8的存储器结构,其中该半导体层包含形成于所述nor存储器串的相邻的堆叠的相对侧壁上的连续层。

10.如权利要求9的存储器结构,其中与所数nor存储器串的一对相邻的堆叠相关联的该半导体层是自与所述nor存储器串的其他对相邻的堆叠相关联的该半导体层隔离。

11.如权利要求1的存储器结构,其中该半导体层及该铁电闸极介电层形成为邻近于在相邻的堆叠之间的各别导体,且该半导体层是在该第一方向上自与设置于相同相邻的堆叠之间的其他导体相关联的该半导体层隔离。

12.如权利要求1的存储器结构,其中该第一隔离层包含气隙空腔。

13.如权利要求12的存储器结构,其中这些气隙空腔延伸至所述nor存储器串的一堆叠中的这些铁电场效晶体管的该铁电闸极介电层,该半导体层设置成仅邻近于该堆叠中的各存储器串对且借由相邻的存储器串对之间的这些气隙空腔划分。

14.如权利要求13的存储器结构,其中这些气隙空腔延伸至形成nor存储器串的一堆叠中的这些铁电场效晶体管的该共同闸极电极的该导体,该半导体层及该铁电闸极介电层设置成仅邻近于该堆叠中的各存储器串对且借由邻近存储器串对之间的这些气隙空腔划分。

15.如权利要求12的存储器结构,其中该第二隔离层包含气隙空腔。

16.如权利要求12的存储器结构,其中该第一隔离层在该第二方向上具有第一尺寸且该第二隔离层在该第二方向上具有第二尺寸,该第二尺寸是该铁电场效晶体管的通道长度。

17.如权利要求16的存储器结构,其中该第一隔离层的该第一尺寸小于该第二隔离层的该第二尺寸。

18.如权利要求16的存储器结构,其中该第一隔离层的该第一尺寸是30nm,且该第二隔离层的该第二尺寸具有30nm至80nm之间的值。

19.如权利要求1的存储器结构,其中该共同源极层及该共同汲极层各自包含金属层。

20.如权利要求19的存储器结构,其中与各nor存储器串中的这些铁电场效晶体管相关联的该半导体层接触形成该共同源极层及该共同汲极层的这些金属层以提供用于各铁电场效晶体管的无接合通道区。

21.如权利要求19的存储器结构,其中该金属层包含金属,该金属包含以下中的一或多者:钼、钛、钨、镧、钽、钌、任何其硅化物、任何其氮化物及任何其组合。

22.如权利要求1的存储器结构,其中各nor存储器串的该共同汲极层充当用于各nor存储器串的共同位元线。

23.如权利要求1的存储器结构,其中该多个导体各自包含氮化钛层。

24.如权利要求23的存储器结构,其中该多个导体各自包含形成为邻近于该铁电闸极介电层的该氮化钛层以及形成为邻近于该氮化钛层的钨层。

25.如权利要求1的存储器结构,其中该铁电闸极介电层包含掺杂氧化铪层。

26.如权利要求25的存储器结构,其中该掺杂氧化铪层包含以下中的一或多者:掺锆氧化铪(hzo)、掺硅氧化铪(hso)、掺铝锆氧化铪(hfzralo)、掺铝氧化铪(hfo2:al)、掺镧氧化铪(hfo2:la)、氮氧化铪锆(hfzron)、氧化铪锆铝(hfzralo)以及包括锆杂质的任何氧化铪。

27.如权利要求1的存储器结构,其中各铁电场效晶体管是借由将第一电压施加至该共同源极层及该共同汲极层两者且将第二电压施加至相关联共同闸极电极而以电性方式置于第一极化状态中;并且各铁电场效晶体管是借由将第三电压施加至该共同汲极层、将第四电压施加至该共同源极层且将第五电压施加至该相关联共同闸极电极而以电性方式置于第二极化状态中,该第三电压不同于该第四电压。

28.如权利要求1的存储器结构,其中各铁电场效晶体管是借由将第一电压施加至该共同源极层及该共同汲极层两者且将至少一第二电压施加至相关联共同闸极电极而以电性方式置于第一极化状态中;并且各铁电场效晶体管是借由将电压施加至该共同汲极层、该共同源极层及该相关联共同闸极电极而以电性方式置于多于两个极化状态中,这些电压针对该多于两个极化状态中的各者而具有不同电压范围。

29.如权利要求28的存储器结构,其中该多于两个极化状态包含模拟状态的连续区。

30.如权利要求27的存储器结构,其中在所述nor存储器串的各别堆叠中在该第二方向上形成于一行中的铁电场效晶体管经分组以形成一页存储器胞元,该页存储器胞元是借由将该第一电压施加至各别共同源极层及该共同汲极层且将该第二电压施加至各别共同闸极电极而一起置于该第一极化状态中。

31.如权利要求27的存储器结构,其中这些nor存储器串的这些共同源极层以电性方式浮置,且各别共同源极层在预充电阶段期间经偏压至给定电压且随后保持浮置。

32.如权利要求1的存储器结构,其中所述nor存储器串的各堆叠包含形成于该堆叠的两侧上的侧壁上的铁电场效晶体管。

33.如权利要求1的存储器结构,其中用于支援存储器操作的电路系统形成于多个铁电场效晶体管堆叠下面的该半导体基板的该平坦表面处。

34.如权利要求33的存储器结构,其中用于支援存储器操作的该电路系统包括模拟及数字电路两者。

35.如权利要求33的存储器结构,其中用于支援存储器操作的该电路系统回应于提供至该存储器结构的抹除、程序化及读取命令而针对该多个铁电场效晶体管堆叠实施抹除、程序化及读取操作。

36.如权利要求33的存储器结构,其进一步包含形成于这些nor存储器串上方且与这些nor存储器串电连接的互连导体层以及用于支援存储器操作的该电路系统,该互连导体层经设置以用于在这些nor存储器串及用于支援存储器操作的该电路系统当中路由控制及数据信号。

37.如权利要求36的存储器结构,其中用于支援存储器操作的该电路系统包含以下中的两者或更多者:字线驱动器电路、位元线驱动器电路、输入/输出驱动器电路、地址解码器、感测放大器、用于产生用于该存储器操作的操作电压的电压源、锁存器、暂存器或其他存储器元件以及用于管理这些nor存储器串的这些铁电场效晶体管处的这些存储器操作的状态机。

38.如权利要求37的存储器结构,其中用于支援存储器操作的该电路系统耦接至形成于个别半导体基板上的存储器控制器以自该存储器控制器接收命令及数据信号。

39.如权利要求1的存储器结构,其中各铁电场效晶体管具有长于1小时的数据留存时间以及大于108个程序化/抹除循环的程序化/抹除循环耐久性。

40.一种三维存储器结构,其形成于半导体基板的平坦表面上方,该存储器结构包含:

41.如权利要求40的存储器结构,其中该铁电闸极介电层包含在该第二方向上邻近于各导体而设置为连续层的铁电极化层。

42.如权利要求40的存储器结构,其中该氧化物半导体层沿着所述nor存储器串的各个各别堆叠的侧壁设置为连续层。

43.如权利要求40的存储器结构,其中各nor存储器串内的这些铁电场效晶体管的该共同源极层及该共同汲极层是借由第二隔离层在该第二方向上间隔开配置。

44.如权利要求40的存储器结构,其中该氧化物半导体层包含氧化铟锌(izo)层及氧化铟镓锌(igzo)层中的一者。

45.如权利要求40的存储器结构,其中该氧化物半导体层及该铁电闸极介电层形成为邻近于在相邻的堆叠之间的各别导体,且该氧化物半导体层是在该第一方向上自与设置于相同相邻的堆叠之间的其他导体相关联的该氧化物半导体层隔离。

46.如权利要求40的存储器结构,其中该第一隔离层包含气隙空腔。

47.如权利要求46的存储器结构,其中这些气隙空腔延伸至所述nor存储器串的一堆叠中的这些铁电场效晶体管的该铁电闸极介电层,该氧化物半导体层设置成仅邻近于该堆叠中的各存储器串对且借由相邻的存储器串对之间的这些气隙空腔划分。

48.如权利要求46的存储器结构,其中这些气隙空腔延伸至形成所述nor存储器串的一堆叠中的这些铁电场效晶体管的该共同闸极电极的该导体,该氧化物半导体层及该铁电闸极介电层设置成仅邻近于该堆叠中的各存储器串对且借由相邻的存储器串对之间的这些气隙空腔划分。

49.如权利要求40的存储器结构,其中该共同源极层及该共同汲极层各自包含金属层;并且其中与各nor存储器串中的这些铁电场效晶体管相关联的该氧化物半导体层接触形成该共同源极层及该共同汲极层的这些金属层以提供用于各铁电场效晶体管的无接合通道区。

50.如权利要求40的存储器结构,其中该铁电闸极介电层包含掺杂氧化铪层。

51.如权利要求40的存储器结构,其中各铁电场效晶体管是借由将第一电压施加至该共同源极层及该共同汲极层两者且将第二电压施加至相关联共同闸极电极而以电性方式置于第一极化状态中;并且各铁电场效晶体管是借由将第三电压施加至该共同汲极层、将第四电压施加至该共同源极层且将第五电压施加至该相关联共同闸极电极而以电性方式置于第二极化状态中,该第三电压不同于该第四电压。

52.如权利要求51的存储器结构,其中这些nor存储器串的这些共同源极层以电性方式浮置,且各别共同源极层在预充电阶段期间经偏压至给定电压且随后保持浮置。

53.一种三维存储器结构,其形成于半导体基板的平坦表面上方,该存储器结构包含:

54.如权利要求53的存储器结构,其中该氧化物半导体层及该铁电闸极介电层两者是借由各平面处的这些气隙空腔分离,以将该氧化物半导体层及该铁电闸极介电层与所述nor存储器串的该各别堆叠中的各nor存储器串隔离。

55.如权利要求53的存储器结构,其中该铁电闸极介电层包含在该第二方向上邻近于各导体而设置为连续层的铁电极化层。

56.如权利要求53的存储器结构,其中各nor存储器串内的这些铁电场效晶体管的该共同源极层及该共同汲极层是借由第一隔离层在该第二方向上间隔开配置。

57.如权利要求56的存储器结构,其中该第一隔离层包含介电层。

58.如权利要求53的存储器结构,其中该氧化物半导体层包含氧化铟锌(izo)层及氧化铟镓锌(igzo)层中的一者。

59.如权利要求53的存储器结构,其中该氧化物半导体层及该铁电闸极介电层形成为邻近于在相邻的堆叠之间的各别导体,且该氧化物半导体层是在该第一方向上自与设置于相同相邻的堆叠之间的其他导体相关联的该氧化物半导体层隔离。

60.如权利要求53的存储器结构,其中这些气隙空腔延伸至所述nor存储器串的一堆叠中的这些铁电场效晶体管的该铁电闸极介电层,该氧化物半导体层设置成仅邻近于该堆叠中的各存储器串且借由相邻的存储器串之间的这些气隙空腔划分。

61.如权利要求53的存储器结构,其中这些气隙空腔延伸至形成所述nor存储器串的一堆叠中的这些铁电场效晶体管的该共同闸极电极的该导体,该氧化物半导体层及该铁电闸极介电层设置成仅邻近于该堆叠中的各存储器串且借由相邻的存储器串之间的这些气隙空腔划分。

62.如权利要求53的存储器结构,其中该共同源极层及该共同汲极层各自包含金属层;并且其中与各nor存储器串中的这些铁电场效晶体管相关联的该氧化物半导体层接触形成该共同源极层及该共同汲极层的这些金属层以提供用于各铁电场效晶体管的无接合通道区。

63.如权利要求53的存储器结构,其中该铁电闸极介电层包含掺杂氧化铪层。

64.如权利要求63的存储器结构,其中该掺杂氧化铪层包含以下中的一或多者:掺锆氧化铪(hzo)、掺硅氧化铪(hso)、掺铝锆氧化铪(hfzralo)、掺铝氧化铪(hfo2:al)、掺镧氧化铪(hfo2:la)、氮氧化铪锆(hfzron)、氧化铪锆铝(hfzralo)以及包括锆杂质的任何氧化铪。

65.如权利要求53的存储器结构,其中这些nor存储器串的这些共同源极层以电性方式浮置,且各别共同源极层在预充电阶段期间经偏压至给定电压且随后保持浮置。

66.如权利要求53的存储器结构,其中nor存储器串的各堆叠包含形成于该堆叠的两侧上的侧壁上的铁电场效晶体管。

67.如权利要求53的存储器结构,其中用于支援存储器操作的电路系统形成于多个铁电场效晶体管堆叠下方的该半导体基板的该平坦表面处。

技术总结一种存储器结构包括经组织为水平NOR存储器串的储存晶体管,其中这些储存晶体管是具有形成为邻近于半导体通道的铁电闸极介电层的薄膜铁电场效晶体管(FeFET)。在一些具体实例中,该半导体通道由氧化物半导体材料形成,且这些铁电储存晶体管是其中该通道中无p/n接面的无接合晶体管。在一些具体实例中,各NOR存储器串中的这些铁电储存晶体管共用作为共同源极线的第一导电层以及作为共同位元线的第二导电层,该第一导电层及该第二导电层与该半导体通道电接触。大量NOR存储器串中的这些铁电储存晶体管经配置以形成半自主三维存储器阵列(图案块),其中各图案块协同存储器控制器来借由各图案块下面的半导体基板中的电路系统而经个别地定址及控制。技术研发人员:克里斯托弗·J·佩蒂,叶利·哈拉里受保护的技术使用者:日升存储公司技术研发日:技术公布日:2024/4/22本文地址:https://www.jishuxx.com/zhuanli/20240731/184330.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表