复位冗余电路及抗单粒子翻转的复位冗余寄存器的制作方法

- 国知局

- 2024-07-31 19:58:25

本发明主要涉及到电路设计,尤其是一种复位冗余电路及抗单粒子翻转的复位冗余寄存器。

背景技术:

1、宇宙空间环境中存在着大量高能粒子,如质子、电子、重离子等。宇航器的电子系统和设备中采用的半导体器件,在轨运行时受到这些高能粒子轰击后,可造成宇航器发生单粒子效应,使得其组合电路发生单粒子瞬态,或使得其时序电路发生单粒子翻转,如此将严重影响宇航器相关设备的可靠性,降低宇航器的使用寿命甚至损毁航天器,造成不可挽回的损失。因此必须对宇航器进行抗辐照加固设计,以提升其在宇宙空间环境下的可靠性。

2、寄存器作为存储数据的关键单元,对其加固设计,能有效提升宇航级芯片的可靠性。寄存器常采用dice(双互锁存储结构)进行加固设计,在dice加固后的寄存器中增加复位信号端,可以使得其输出强制复位为低电平。然而,处于组合逻辑电路中的复位信号端被高能粒子轰击造成的瞬态脉冲可能会传播到时序存储单元中,导致电路输出异常翻转。

3、因此,设计一种抗单粒子翻转的复位冗余寄存器是本领域技术人员亟需解决的一个技术问题。

技术实现思路

1、针对现有技术存在的技术问题,本发明提供一种复位冗余电路及抗单粒子翻转的复位冗余寄存器,通过复位冗余电路对寄存器的复位信号进行空间冗余加固设计,可有效提高寄存器的抗辐照性能。

2、为了实现上述目的,本发明是通过以下技术方案实现的:

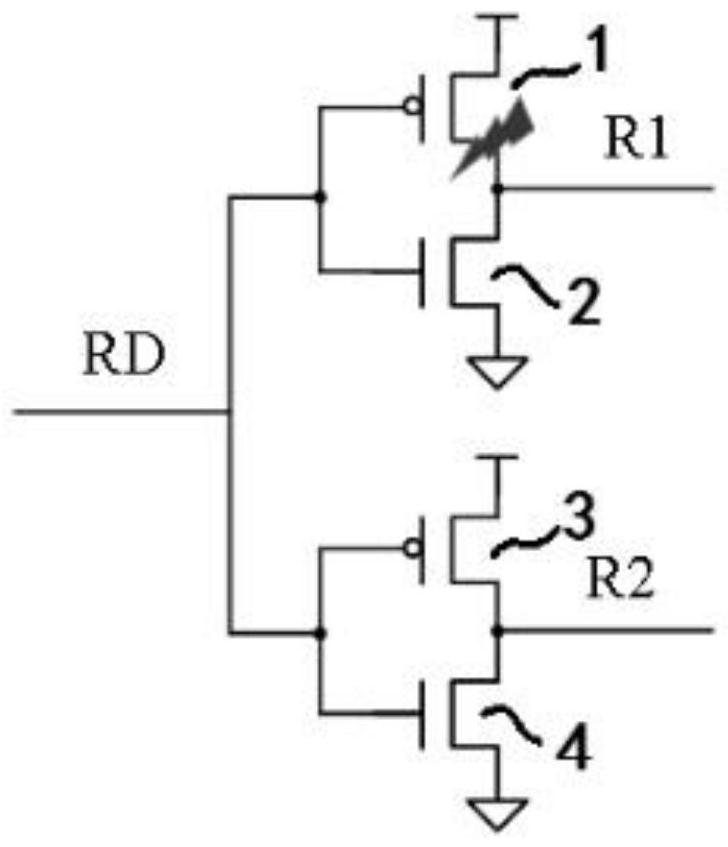

3、一方面,提供一种复位冗余电路,包括4个晶体管,分别为第一晶体管、第二晶体管、第三晶体管和第四晶体管,第一晶体管和第三晶体管为p型晶体管,第二晶体管和第四晶体管为n型晶体管;第一晶体管的栅极、第二晶体管的栅极、第三晶体管的栅极和第四晶体管的栅极连接在一起,作为复位信号rd的输入端;所述第一晶体管的源极接电源,第一晶体管和第二晶体管的漏极连接在一起,作为信号r1的输出端,输出信号r1;第二晶体管的源极接地;第三晶体管的源极接电源,第三晶体管的漏极和第四晶体管的漏极连接在一起,作为信号r2的输出端,输出信号r2;第四晶体管的源极接地。

4、一方面,提供一种抗单粒子翻转的复位冗余寄存器,包括时钟信号ck控制的反相器电路、时钟门控的dice结构电路以及复位冗余电路;数据输入端d连接时钟门控的dice结构电路,时钟门控的dice结构电路与时钟信号ck控制的反相器电路连接,时钟信号ck控制的反相器电路为时钟门控的dice结构电路提供时钟信号,时钟门控的dice结构电路与复位冗余电路连接,复位冗余电路为时钟门控的dice结构电路提供复位信号。

5、进一步地,时钟门控的dice结构电路包括时钟门控的主级dice结构电路和时钟门控的从级dice结构电路,数据输入端d连接时钟门控的主级dice结构电路,时钟门控的主级dice结构串接时钟门控的从级dice结构电路。

6、一方面,提供一种宇航级芯片,包括抗单粒子翻转的复位冗余寄存器。

7、本发明的有益技术效果是:

8、本发明公开了一种复位冗余电路及抗单粒子翻转的复位冗余寄存器,复位冗余电路将复位信号rd备份成两路冗余信号,实现复位冗余加固,显著提升了寄存器的抗单粒子翻转性,可满足实际工程应用。较以往仅利用dice单元进行加固设计的寄存器,本发明寄存器的抗辐照性较高,可应用于航空、航天等领域。

技术特征:1.复位冗余电路,其特征在于:包括4个晶体管,分别为第一晶体管(1)、第二晶体管(2)、第三晶体管(3)和第四晶体管(4),第一晶体管(1)和第三晶体管(3)为p型晶体管,第二晶体管(2)和第四晶体管(4)为n型晶体管;第一晶体管(1)的栅极、第二晶体管(2)的栅极、第三晶体管(3)的栅极和第四晶体管(4)的栅极连接在一起,作为复位信号rd的输入端;所述第一晶体管(1)的源极接电源,第一晶体管(1)和第二晶体管(2)的漏极连接在一起,作为信号r1的输出端,输出信号r1;第二晶体管(2)的源极接地;第三晶体管(3)的源极接电源,第三晶体管(3)的漏极和第四晶体管(4)的漏极连接在一起,作为信号r2的输出端,输出信号r2;第四晶体管(4)的源极接地。

2.抗单粒子翻转的复位冗余寄存器,其特征在于,包括时钟信号ck控制的反相器电路、时钟门控的dice结构电路以及如权利要求1所述的复位冗余电路;数据输入端d连接时钟门控的dice结构电路,时钟门控的dice结构电路与时钟信号ck控制的反相器电路连接,时钟信号ck控制的反相器电路为时钟门控的dice结构电路提供时钟信号,时钟门控的dice结构电路与复位冗余电路连接,复位冗余电路为时钟门控的dice结构电路提供复位信号。

3.根据权利要求2所述的抗单粒子翻转的复位冗余寄存器,其特征在于,时钟门控的dice结构电路包括时钟门控的主级dice结构电路和时钟门控的从级dice结构电路,数据输入端d连接时钟门控的主级dice结构电路,时钟门控的主级dice结构串接时钟门控的从级dice结构电路。

4.根据权利要求3所述的抗单粒子翻转的复位冗余寄存器,其特征在于,所述时钟信号ck控制的反相器电路包括4个晶体管,分别为第五晶体管(5)、第六晶体管(6)、第七晶体管(7)和第八晶体管(8),其中第五晶体管(5)和第七晶体管(7)为p型晶体管,第六晶体管(6)和第八晶体管(8)为n型晶体管;第五晶体管(5)的栅极与第六晶体管(6)的栅极连接在一起,作为时钟信号ck的输入端;第五晶体管(5)的源极接电源,第五晶体管(5)的漏极和第六晶体管(6)的漏极连接在一起,同时作为信号nclk的输出端,输出信号nclk;第六晶体管(6)的源极接地;第七晶体管(7)栅极、第八晶体管(8)的栅极、第五晶体管(5)的漏极和第六晶体管(6)的漏极连接在一起;第七晶体管(7)的栅极接电源,第七晶体管(7)的漏极和第八晶体管(8)的漏极连接在一起,作为信号bclk的输出端,输出信号bclk;第八晶体管(8)的源极接地。

5.根据权利要求4所述的抗单粒子翻转的复位冗余寄存器,其特征在于,所述时钟门控的主级dice结构电路包括24个晶体管,分别为第九晶体管(9)、第十晶体管(10)、第十一晶体管(11)、第十二晶体管(12)、第十三晶体管(13)、第十四晶体管(14)、第十五晶体管(15)、第十六晶体管(16)、第十七晶体管(17)、第十八晶体管(18)、第十九晶体管(19)、第二十晶体管(20)、第二十一晶体管(21)、第二十二晶体管(22)、第二十三晶体管(23)、第二十四晶体管(24)、第二十五晶体管(25)、第二十六晶体管(26)、第二十七晶体管(27)、第二十八晶体管(28)、第二十九晶体管(29)、第三十晶体管(30)、第三十一晶体管(31)、第三十二晶体管(32);

6.根据权利要求5所述的抗单粒子翻转的复位冗余寄存器,其特征在于,所述时钟门控的从级dice结构电路,包括28个晶体管,分别是第三十三晶体管(33)、第三十四晶体管(34)、第三十五晶体管(35)、第三十六晶体管(36)、第三十七晶体管(37)、第三十八晶体管(38)、第三十九晶体管(39)、第四十晶体管(40)、第四十一晶体管(41)、第四十二晶体管(42)、第四十三晶体管(43)、第四十四晶体管(44)、第四十五晶体管(45)、第四十六晶体管(46)、第四十七晶体管(47)、第四十八晶体管(48)、第四十九晶体管(49)、第五十晶体管(50)、第五十一晶体管(51)、第五十二晶体管(52)、第五十三晶体管(53)、第五十四晶体管(54)、第五十五晶体管(55)、第五十六晶体管(56)、第五十七晶体管(57)、第五十八晶体管(58)、第五十九晶体管(59)、第六十晶体管(60);

7.一种宇航级芯片,其特征在于,包括如权利要求2所述的抗单粒子翻转的复位冗余寄存器。

技术总结本发明提供一种复位冗余电路及抗单粒子翻转的复位冗余寄存器,所述复位冗余电路将复位电路备份成两路冗余信号。将所述复位冗余电路应用于复位冗余寄存器中,能够使得寄存器输出不被异常复位为低电平状态,提高了可复位寄存器的抗单粒子翻转能力。较以往仅利用DICE单元进行加固设计的寄存器,本发明寄存器的抗辐照性较高,可应用于航空、航天等领域。技术研发人员:房盼攀,刘祥远,刘晔,祁勇,赖善坤受保护的技术使用者:湖南融创微电子有限公司技术研发日:技术公布日:2024/5/29本文地址:https://www.jishuxx.com/zhuanli/20240731/184833.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表