集成电路、半导体装置及用于管理数据传送的方法与流程

- 国知局

- 2024-07-31 20:01:01

本公开关于半导体装置,尤其涉及一种集成电路、半导体装置及用于管理数据传送的方法。

背景技术:

1、半导体装置(例如,存储器装置)变得较小及更快。对半导体装置的数据传送速度的一个限制起因于由半导体装置中的元件共用的金属线所引起的较大寄生电容,此可显著地减小数据传送速度且延长传送时间。

技术实现思路

1、本公开描述用于管理半导体装置中的数据传送的方法、系统、装置、电路以及技术。

2、本公开的第一个方面提供一种集成电路,包括:第一电路;数据总线,耦接至第一电路;以及预充电电路,耦接至数据总线。预充电电路经配置为在经由数据总线传送数据之前对数据总线预充电以具有预定电压。第一电路通过将控制电压施加至第一电路导电地耦接至数据总线,控制电压基于预定电压而判定。

3、在一些实施例中,预定电压为固定电压,且控制电压进一步通过追踪第一电路中的晶体管的阈值电压的变化(或阈值电压变化)而判定。

4、在一些实施例中,集成电路还包括耦接至数据总线的第二电路。预充电电路经配置为在经由数据总线在第一电路与第二电路之间传送数据之前对数据总线预充电以具有预定电压。

5、在一些实施例中,第一电路包括经配置为接收第一控制信号的第一控制晶体管,且第二电路包括经配置为接收第二控制信号的第二控制晶体管。第一控制信号经配置为用第一控制电压接通第一控制晶体管以使得第一电路导电地耦接至数据总线,且第二控制信号经配置为用第二控制电压接通第二控制晶体管以使得第二电路导电地耦接至数据总线。第一控制电压及第二控制电压中的各一个基于预定电压而判定。

6、在一些实施例中,第一控制晶体管具有耦接至数据总线的第一端子、耦接至第一电路中的第一节点的第二端子以及经配置为接收第一控制信号的第一栅极端子,且第二控制晶体管具有耦接至数据总线的第一端子、耦接至第二电路中的第二节点的第二端子以及经配置为接收第二控制信号的第二栅极端子。

7、在一些实施例中,第一控制电压及第二控制电压中的各一个通过追踪参考晶体管的阈值电压的变化而判定,且第一控制晶体管及第二控制晶体管中的各一个的阈值电压的变化与参考晶体管的阈值电压的变化实质上相同。

8、在一些实施例中,集成电路还包括电压产生器,电压产生器包括参考晶体管,且电压产生器经配置为基于参考晶体管的阈值电压而产生第一控制电压及第二控制电压。

9、在一些实施例中,参考晶体管包括耦接至电流源的第一端子、耦接至电阻器的第二端子以及耦接至第一端子的栅极端子,预定电压对应于第二端子处的基于电阻器的电阻及自电流源至电阻器的电流的电压,栅极端子处的参考电压为第二端子处的电压与参考晶体管的阈值电压的总和,以及第一控制电压及第二控制电压中的各一个基于参考电压。

10、在一些实施例中,自电流源至电阻器的电流为恒定电流。在一些实施例中,预充电电路经配置为在恒定电流下对数据总线预充电。

11、在一些实施例中,电压产生器还包括耦接至参考晶体管的栅极端子的运算放大器。运算放大器可经配置为基于参考电压而输出追踪电压。第一控制电压及第二控制电压中的各一个可基于追踪电压。

12、在一些实施例中,运算放大器包括电压随耦器(voltage follower)或单元增益放大器(unity gain amplifier)。在一些实施例中,集成电路还包括:第一逻辑栅极,具有耦接至运算放大器的输出的第一逻辑输入及耦接至第一控制晶体管的第一栅极端子的第一逻辑输出;以及第二逻辑栅极,具有耦接至运算放大器的输出的第二逻辑输入及耦接至第二控制晶体管的第二栅极端子的第二逻辑输出,其中第一控制电压及第二控制电压中的各一个与追踪电压实质上相同。

13、在一些实施例中,电阻器的电阻为可调整的,且其中预定电压基于调整电阻器的电阻的结果而判定。在一些实施例中,预定电压通过比较电阻器的不同电阻下经由数据总线的第一电路与第二电路之间的数据传送的响应时间而判定。

14、在一些实施例中,数据传送的响应时间基于预定电压及与数据总线相关联的寄生电容而判定。

15、在一些实施例中,集成电路经配置为通过使用耦接至第二电路中的第二控制晶体管的第二节点处的电压将数据自第一电路传送至第二电路,所述电压表示与耦接至第一电路中的第一控制晶体管的第一节点处的电压相同的值。

16、在一些实施例中,在传送数据之前,第二电路经配置为经重设以使得第二电路中的第二节点处的电压表示位值「1」。第二电路可包括单向三态锁存器(unidirectionaltri-state latch)。

17、在一些实施例中,在数据总线由预充电电路充电以具有预定电压之后,第一控制晶体管由具有第一控制电压的第一控制信号接通。若第一节点处的电压表示位值「0」,则数据总线上的预定电压可放电,或若第一节点处的电压表示位值「1」,则数据总线上的预定电压可保持不变。

18、在一些实施例中,在第一节点的电压稳定之后,第二控制晶体管由具有第二控制电压的第二控制信号接通。若数据总线具有对应于第一节点的表示位值「0」的电压的放电电压,则第二电路中的第二节点处的电压可放电至表示位值「0」的电压,或若数据总线保持在对应于第一节点的表示位值「1」的电压的预定电压,则第二节点处的电压可保持不变。

19、在一些实施例中,第二电路经配置为:通过将第二节点导电地连接至供电电压来维持第二节点处的表示位值「1」的电压,且在接通第二控制晶体管之前,将第二节点与供电电压导电地隔离以使得第二节点以表示位值「1」的电压浮动。

20、在一些实施例中,集成电路包括页面缓冲器电路,且页面缓冲器电路包括作为第一锁存器的第一电路、作为第二锁存器的第二电路以及数据总线。第一电路及第二电路可在同一页面缓冲器中。

21、在一些实施例中,集成电路包括:页面缓冲器电路,包括作为第一锁存器的第一电路;以及快取电路,包括作为第二锁存器的第二电路。在一些实施例中,第一锁存器及第二锁存器中的各一个为单向三态锁存器。

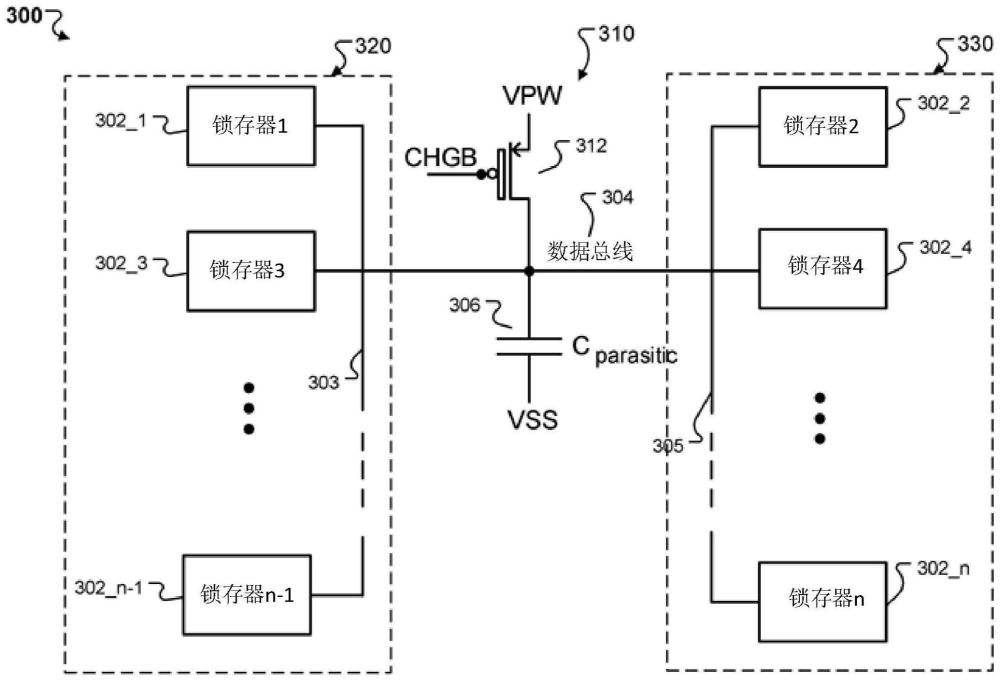

22、本公开的第二个方面提供一种半导体装置,包括:多个锁存器;数据总线,耦接至多个锁存器中的各一个;以及预充电电路,耦接至数据总线。预充电电路经配置为在将数据自多个锁存器当中的第一锁存器传送至第二锁存器之前对数据总线预充电以具有预定电压,且第一锁存器及第二锁存器中的至少一个通过将控制电压施加至第一锁存器及第二锁存器中的至少一个导电地耦接至数据总线,控制电压基于预定电压而判定。

23、在一些实施例中,预定电压为固定电压,且控制电压进一步通过追踪第一锁存器及第二锁存器中的至少一个中的晶体管的阈值电压的变化而判定。

24、在一些实施例中,第一锁存器包括第一控制晶体管,所述第一控制晶体管耦接至数据总线且经配置为接收具有第一控制电压的第一控制信号以接通第一控制晶体管。第二锁存器可包括第二控制晶体管,所述第二控制晶体管耦接至数据总线且经配置为接收具有第二控制电压的第二控制信号以接通第二控制晶体管。第一控制电压及第二控制电压中的各一个可基于预定电压及通过追踪参考晶体管的阈值电压的变化而判定,且第一控制晶体管及第二控制晶体管中的各一个的阈值电压的变化与参考晶体管的阈值电压的变化可实质上相同。

25、在一些实施例中,半导体装置还包括电压产生器,电压产生器包括参考晶体管。参考晶体管包括耦接至电流源的第一端子、耦接至电阻器的第二端子以及耦接至第一端子的栅极端子,且预定电压对应于第二端子处的基于电阻器的电阻及自电流源至电阻器的电流的电压。栅极端子处的参考电压为第二端子处的电压与参考晶体管的阈值电压的总和,且第一控制电压及第二控制电压中的各一个可基于参考电压来判定。

26、在一些实施例中,电压产生器还包括运算放大器,所述运算放大器耦接至参考晶体管的栅极端子且经配置为基于参考电压而输出追踪电压。半导体装置可还包括:第一逻辑栅极,具有耦接至运算放大器的输出的第一逻辑输入及耦接至第一控制晶体管的第一逻辑输出;以及第二逻辑栅极,具有耦接至运算放大器的输出的第二逻辑输入及耦接至第二控制晶体管的第二逻辑输出。第一控制电压及第二控制电压中的各一个与追踪电压可实质上相同。

27、在一些实施例中,半导体装置包括页面缓冲器电路,所述页面缓冲器电路包括多个锁存器及数据总线。在一些实施例中,半导体装置包括:页面缓冲器电路,包括第一锁存器,以及快取电路,包括第二锁存器。快取电路可经由数据总线耦接至页面缓冲器电路。

28、在一些实施例中,半导体装置还包括用于将数据储存于存储器单元中的存储器单元阵列,且页面缓冲器电路耦接至存储器单元阵列。

29、本公开的第三个方面提供一种用于管理半导体装置中的数据传送的方法,包括:对数据总线预充电以在数据总线上具有预定电压;通过将第一控制电压施加至第一电路将第一电路导电地连接至数据总线以使得数据总线上的电压对应于第一电路中的第一节点处的电压,数据总线上的电压与数据总线上的预定电压相关联;以及通过将第二控制电压施加至第二电路将第二电路导电地连接至数据总线以使得第二电路中的第二节点处的电压对应于数据总线上的电压。第一控制电压及第二控制电压中的各一个可基于预定电压而判定。

30、以上技术的实施包括方法、系统、电路、计算机程序产品以及计算机可读介质。在一个实例中,方法可在非易失性存储器中执行,且方法可包括上文所描述的动作,例如用于管理数据传送的动作。在另一实例中,一种此类计算机程序产品适合实施于非瞬时机器可读介质中,所述非瞬时机器可读介质储存可由一个或多个处理器执行的指令。指令经配置为使得一个或多个处理器执行上文所描述的动作。一个此类计算机可读介质储存指令,所述指令在由一个或多个处理器执行时经配置为使得一个或多个处理器执行上文所描述的动作。

31、所述技术可实施于需要电路或装置中的元件之间的数据传送且具有数据传送速度问题及/或功率消耗问题的任何类型的电路或装置中。技术可优化数据传送速度且减少功率消耗。技术可通过任何类型的存储器晶体管(或存储器单元)、任何类型的金属氧化硅(metal-oxide-silicon,mos)晶体管(例如,n通道及/或p通道晶体管)、任何类型的双极结晶体管(bipolar junction transistor,bjt)以及任何类型的运算放大器来实施。技术可应用于不同类型的存储器系统,例如二维(two-dimensional,2d)存储器系统或三维(three-dimensional,3d)存储器系统。技术可应用于各种存储器单元类型类型,诸如单级单元(single-level cell,slc),或多级单元(multi-level cell,mlc),如二级单元、三级单元(triple-level cell,tlc)、四级单元(quad-level cell,tlc)或五级单元(penta-level cell,plc)。技术可应用于各种类型的易失性存储器装置或非易失性存储器装置,诸如静态随机存取存储器(static random access memory,sram)、动态随机存取存储器(dynamic random access memory,dram)、诸如nor闪存及/或nand闪存的闪存、电阻性随机存取存储器(resistive random-access memory,rram)、磁阻性随机存取存储器(magnetoresistive random-access memory,mram)、相变随机存取存储器(phase-changerandom-access memory,pcram)等等。另外或替代地,技术可应用于各种类型的装置及系统,诸如安全数字(secure digital,sd)卡、嵌入型多介质卡(embedded multimedia card,emmc)或固态硬盘(solid-state drive,ssd)、嵌入型系统等等。

32、在本公开中,「a与b实质上相同」指示:1)a为恰好相同于b;或2)a与b之间的差小于预定阈值值,例如a或b的值的1%或0.1%,或任何合适的阈值值。类似地,「a与b实质上相同」指示:1)a与b相同;或2)a与b之间的差小于预定阈值值,例如a或b的值的1%或0.1%,或任何合适的阈值值。举例而言,若电压a与电压b实质上相同,则其指示电压a与电压b相同,或电压a与电压b之间的差小于阈值值,例如电压a的0.1%、1毫伏、1微伏或任何合适的阈值值。

33、在随附附图及以下描述中阐述一个或多个所公开实施的细节。其他特征、方面以及优点将自描述、附图以及权利要求范围变得显而易见。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185044.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表