半导体结构及其制备方法与流程

- 国知局

- 2024-08-02 15:57:30

本公开涉及半导体,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、动态随机存取存储器(dynamic random access memory,简称dram)中的存储单元多为存储电容。目前在制备存储电容的过程中,通常会于阵列区先形成模具叠层结构,以图形化模具叠层结构并去除模具叠层结构中的模具层而形成网格图案,然后再于该网格图案内形成存储电容。

2、然而,在形成存储电容之后,因存储电容顶面与周边区的衬底表面之间容易具有较大的台阶,因此,需要采用大量的氧化物回填周边区并覆盖存储电容,然后再通过化学机械研磨的方式来消除氧化物在阵列区和周边区之间的台阶差。如此,容易导致存储电容具有较大的倾倒风险,且需要研磨较多氧化物材料以消除氧化物在阵列区和周边区之间的台阶差。因此,如何改善存储电容的制备工艺以提高dram的工艺可靠性已成为目前亟待解决的技术问题之一。

技术实现思路

1、基于此,本公开实施例提供了一种半导体结构及其制备方法,可以优化电容器的制备工艺以提高半导体结构的工艺可靠性。

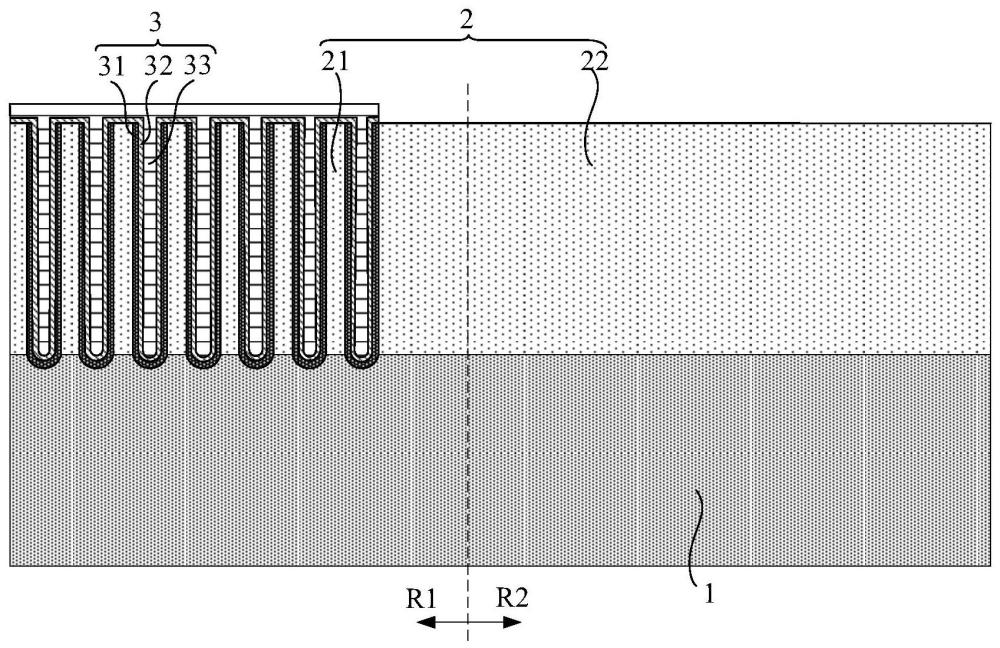

2、一方面,本公开根据一些实施例提供了一种半导体结构。该半导体结构包括:衬底、第一介质层以及多个电容器。衬底具有阵列区以及设置于阵列区至少一侧的周边区。第一介质层设置于衬底上,具有位于阵列区内的多个电容槽。第一介质层位于阵列区的部分构成第一隔离结构,第一介质层位于周边区的部分构成第二隔离结构。多个电容器分别位于对应的电容槽内。

3、根据一些实施例,电容器包括:层叠设置且填充电容槽的第一电极、介电层和第二电极;其中,多个电容器的介电层相连为一体结构;多个电容器的第二电极相连为一体结构。

4、根据一些实施例,所述半导体结构还包括:位于电容器及第二隔离结构上的第三隔离结构。

5、根据一些实施例,衬底包括:分别位于阵列区的多个第一导电结构。电容槽暴露出对应的第一导电结构;第一电极与第一导电结构对应连接。

6、根据一些实施例,所述半导体结构还包括:设置于第二电极和第三隔离结构之间的接触层。

7、根据一些实施例,所述半导体结构还包括:一个或多个第一连接结构以及一个或多个第二连接结构。第一连接结构贯穿第三隔离结构位于阵列区的部分,与接触层相连接。第二连接结构贯穿第三隔离结构位于周边区的部分以及第二隔离结构。

8、根据另一些实施例,所述半导体结构还包括:第四隔离结构、一个或多个第一连接结构以及一个或多个第二连接结构。第四隔离结构覆盖第三隔离结构。第一连接结构贯穿第四隔离结构和第三隔离结构位于阵列区的部分,与接触层相连接。第二连接结构贯穿第四隔离结构和第三隔离结构位于周边区的部分以及第二隔离结构。

9、根据一些实施例,衬底还包括:设置于周边区的一个或多个第二导电结构。其中,第二隔离结构覆盖第二导电结构。第二连接结构与第二导电结构对应连接。

10、另一方面,本公开根据一些实施例提供了一种半导体结构的制备方法,用于制备上述一些实施例中的半导体结构。所述半导体结构的制备方法包括如下步骤。

11、提供衬底,衬底具有阵列区以及设置于阵列区至少一侧的周边区。

12、于衬底上形成第一介质材料层。

13、图案化第一介质材料层位于阵列区的部分,形成多个电容槽,得到第一介质层。第一介质层位于阵列区的部分构成第一隔离结构。第一介质层位于周边区的部分构成第二隔离结构。

14、于电容槽内形成电容器。

15、根据一些实施例,所述半导体结构的制备方法还包括如下步骤。

16、于电容器及第二隔离结构上形成第二介质层。

17、研磨第二介质层,获得第三隔离结构。

18、根据一些实施例,于电容槽内形成电容器之后,所述制备方法还包括:于电容器上形成接触层。相应地,于电容器及第二隔离结构上形成第二介质层,还包括:于接触层及第二隔离结构上形成第二介质层。

19、根据一些实施例,第二介质层的厚度大于接触层的厚度,且第二介质层与接触层的厚度之差小于或等于目标阈值。

20、根据一些实施例,所述半导体结构的制备方法还包括如下步骤。

21、形成覆盖第三隔离结构的第四隔离结构。

22、图案化第四隔离结构和第三隔离结构位于阵列区的部分,形成贯穿第四隔离结构和第三隔离结构的一个或多个第一连接孔。

23、于第一连接孔内形成第一连接结构,第一连接结构与接触层相连接。

24、图案化第四隔离结构和第三隔离结构位于周边区的部分以及第二隔离结构,形成贯穿第四隔离结构、第三隔离结构和第二隔离结构的一个或多个第二连接孔。

25、于第二连接孔内形成第二连接结构。

26、根据另一些实施例,所述半导体结构的制备方法还包括如下步骤。

27、图案化第三隔离结构位于阵列区的部分,形成多个第一连接孔;第一连接孔暴露出对应的电容器。

28、于第一连接孔内形成第一连接结构,第一连接结构与电容器相连接。

29、图案化第三隔离结构位于周边区的部分及第二隔离结构,形成贯穿第三隔离结构和第二隔离结构的一个或多个第二连接孔。

30、于第二连接孔内形成第二连接结构。

31、根据一些实施例,所述于电容槽内形成电容器,包括如下步骤。

32、形成随形覆盖第一隔离结构顶面及各电容槽槽壁的第一电极材料层。

33、图案化第一电极材料层,形成分别位于各电容槽内的第一电极。

34、形成随形覆盖第一隔离结构顶面及各第一电极的介电材料层。

35、形成覆盖介电材料层并填充各电容槽的第二电极材料层。

36、根据一些实施例,第一电极材料层还覆盖第二隔离结构。所述图案化第一电极材料层还包括:去除第一电极材料层覆盖第二隔离结构的部分,以暴露出第二隔离结构。

37、根据一些实施例,所述于电容槽内形成电容器,还包括:研磨第二电极材料层,形成第二电极中间结构。

38、根据一些实施例,介电材料层还覆盖第二隔离结构。所述于电容槽内形成电容器还包括:去除第二电极中间结构及介电材料层位于周边区的部分,以分别形成第二电极及介电层,并暴露出第二隔离结构。其中,任一电容槽内的第一电极以及介电层和第二电极位于该电容槽内的部分共同构成电容器。

39、根据一些实施例,所述研磨第二电极材料层,形成第二电极中间结构之后,所述制备方法还包括:形成覆盖第二电极中间结构的接触材料层。

40、相应地,所述去除第二电极中间结构及介电材料层位于周边区的部分之前,所述制备方法还包括:去除接触材料层位于周边区的部分,形成接触层。

41、根据一些实施例,所述于衬底上形成第一介质材料层之前,所述制备方法还包括:于衬底内形成多个导电结构;多个导电结构包括位于阵列区的多个第一导电结构和位于周边区的多个第二导电结构。其中,第一介质材料层覆盖第一导电结构和第二导电结构。电容槽暴露出对应的第一导电结构,第一电极与第一导电结构对应连接。

42、在本公开实施例提供的半导体结构及其制备方法中,于衬底上设置第一介质层,并使第一介质层位于阵列区的部分具有电容槽且构成第一隔离结构,使第一介质层位于周边区的部分构成第二隔离结构。如此,在电容槽内制备电容器时,可以利用第一隔离结构对电容器的支撑作用及第二隔离结构对第一隔离结构的支撑作用,确保电容器不存在倾倒风险。并且,本公开实施例中,由第一介质层位于阵列区和周边区的不同部分分别构成第一隔离结构和第二隔离结构,可以确保第一隔离结构顶面和第二隔离结构顶面之间无台阶差或仅具有较小台阶差。从而无需采用大量氧化物进行回填,也利于确保后续于第一介质层上形成的第二介质层表面仅具有较小台阶,进而能够有效降低第二介质层研磨工艺的实施难度及不必要的材料浪费,以有效提高半导体结构的工艺可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248621.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表