半导体器件的制作方法

- 国知局

- 2024-08-02 15:56:03

本公开涉及一种半导体器件,更具体地,涉及一种包括栅极结构的半导体器件及其制造方法。

背景技术:

1、半导体器件由于其小尺寸、多功能特性和/或低制造成本而被广泛地用在电子工业中。半导体器件可以被分类为用于存储逻辑数据的半导体存储器件、用于处理逻辑数据的半导体逻辑器件、以及具有半导体存储器件的功能和半导体逻辑器件的功能两者的混合半导体器件。

2、由于一直要求高速和/或低功率电子装置,因此也一直要求在其中使用的高速和/或低电压半导体器件,从而一直需要高度集成的半导体器件来满足这些需求。然而,随着半导体器件集成密度增大,半导体器件的电特性和生产率可能劣化或降低。因此,已经不同地研究了用于改进半导体器件的电特性和生产率的技术。

技术实现思路

1、发明构思的实施例可以提供一种具有改进的电特性和可靠性的半导体器件及其制造方法。

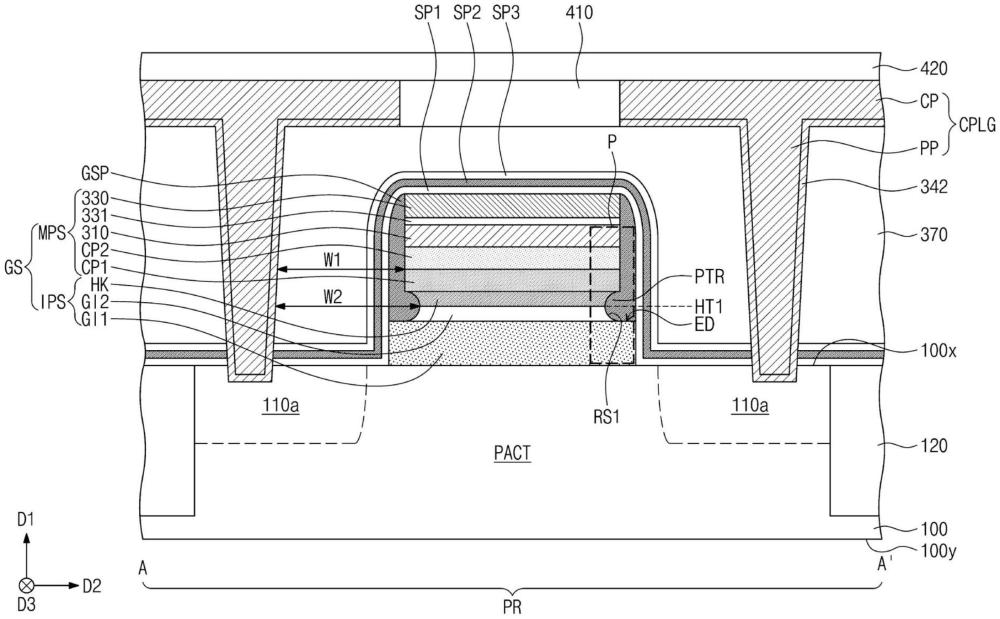

2、在一个方面中,一种半导体器件可以包括:衬底,所述衬底包括由器件隔离层限定的外围有源图案;栅极结构,所述栅极结构位于所述外围有源图案上;以及栅极间隔物,所述栅极间隔物覆盖所述栅极结构的侧表面的至少一部分。所述栅极结构可以包括绝缘图案结构和位于所述绝缘图案结构上的金属图案结构。所述绝缘图案结构可以包括在离所述衬底的顶表面第一高度在与所述衬底的所述顶表面平行的第一方向上具有最大深度的凹陷。所述绝缘图案结构可以包括依次堆叠在所述衬底的顶表面上的第一栅极绝缘图案和高k电介质层。所述栅极间隔物可以包括插入在所述凹陷中的突起。

3、在一个方面中,一种半导体器件可以包括:衬底,所述衬底包括由器件隔离层限定的外围有源图案;栅极结构,所述栅极结构位于所述外围有源图案上;栅极间隔物,所述栅极间隔物覆盖所述栅极结构的侧表面的至少一部分;下绝缘图案,所述下绝缘图案设置在所述衬底上并且覆盖所述栅极结构和所述栅极间隔物;以及接触插塞,所述接触插塞与所述栅极结构横向地间隔开并且穿透所述下绝缘图案以便连接到所述衬底。所述栅极结构可以包括绝缘图案结构和位于所述绝缘图案结构上的金属图案结构。所述绝缘图案结构可以包括在离所述衬底的顶表面第一高度在与所述衬底的所述顶表面平行的第一方向上具有最大深度的凹陷。从所述接触插塞的侧表面到所述金属图案结构的侧表面的距离可以是第一距离,而从所述接触插塞的所述侧表面到所述凹陷的底表面的距离可以是第二距离。所述第二距离可以大于所述第一距离。

4、在一个方面中,一种半导体器件可以包括:衬底,所述衬底包括单元有源图案和外围有源图案,所述单元有源图案位于单元区域上,所述外围有源图案位于所述单元区域周围的外围区域上;字线,所述字线设置所述在衬底中并且与所述单元有源图案相交;位线,所述位线设置在所述衬底上并且与所述字线相交;位线接触,所述位线接触设置在每一个所述单元有源图案的中央部分上并且连接到所述位线中的对应位线;存储节点接触,所述存储节点接触位于每一个所述单元有源图案的两个端部中的每一个端部上;着陆焊盘,所述着陆焊盘位于所述存储节点接触上;电容器,所述电容器位于所述着陆焊盘上;栅极结构,所述栅极结构位于所述外围有源图案上;以及栅极间隔物,所述栅极间隔物覆盖所述栅极结构的侧表面的至少一部分。所述栅极结构可以包括绝缘图案结构和位于所述绝缘图案结构上的金属图案结构。所述绝缘图案结构可以包括在离所述衬底的顶表面第一高度在与所述衬底的所述顶表面平行的第一方向上具有最大深度的凹陷。所述栅极间隔物可以包括插入在所述凹陷中的突起。

技术特征:1.一种半导体器件,所述半导体器件包括:

2.根据权利要求1所述的半导体器件,其中,所述绝缘图案结构还包括第二栅极绝缘图案,所述第二栅极绝缘图案位于所述第一栅极绝缘图案与所述高k电介质层之间,

3.根据权利要求2所述的半导体器件,所述半导体器件还包括:

4.根据权利要求2所述的半导体器件,其中,所述第一栅极绝缘图案在所述第一方向上延伸,并且

5.根据权利要求2所述的半导体器件,其中,所述第一栅极绝缘图案包括氮氧化硅,

6.根据权利要求1所述的半导体器件,其中,所述金属图案结构包括依次堆叠的第一导电图案、栅极图案、阻挡图案和含金属图案,并且

7.根据权利要求6所述的半导体器件,其中,所述金属图案结构还包括第二导电图案,所述第二导电图案设置在所述第一导电图案与所述栅极图案之间,

8.根据权利要求1所述的半导体器件,其中,所述绝缘图案结构还包括第二栅极绝缘图案,所述第二栅极绝缘图案位于所述第一栅极绝缘图案与所述高k电介质层之间,并且

9.根据权利要求8所述的半导体器件,其中,所述金属图案结构包括依次堆叠的第一导电图案、第二导电图案、栅极图案、阻挡图案和含金属图案,并且

10.根据权利要求1所述的半导体器件,其中,所述绝缘图案结构还包括第二栅极绝缘图案,所述第二栅极绝缘图案设置在所述第一栅极绝缘图案与所述高k电介质层之间,

11.根据权利要求1所述的半导体器件,其中,所述凹陷位于所述第一栅极绝缘图案的底表面与所述高k电介质层的底表面之间。

12.根据权利要求1所述的半导体器件,其中,所述绝缘图案结构还包括第二栅极绝缘图案,所述第二栅极绝缘图案设置在所述第一栅极绝缘图案与所述高k电介质层之间,

13.一种半导体器件,所述半导体器件包括:

14.根据权利要求13所述的半导体器件,其中,所述第二距离在大约30nm至大约100nm的范围内。

15.根据权利要求13所述的半导体器件,其中,所述绝缘图案结构包括第一栅极绝缘图案和位于所述第一栅极绝缘图案上的高k电介质层,以及

16.根据权利要求13所述的半导体器件,所述半导体器件还包括:

17.根据权利要求13所述的半导体器件,所述半导体器件还包括:

18.根据权利要求13所述的半导体器件,其中,所述绝缘图案结构包括依次堆叠的第一栅极绝缘图案、第二栅极绝缘图案和高k电介质层,

19.一种半导体器件,所述半导体器件包括:

20.根据权利要求19所述的半导体器件,其中,所述栅极间隔物与所述衬底间隔开。

技术总结一种半导体器件包括:衬底,所述衬底包括由器件隔离层限定的外围有源图案;栅极结构,所述栅极结构位于所述外围有源图案上;以及栅极间隔物,所述栅极间隔物覆盖所述栅极结构的侧表面的至少一部分。所述栅极结构包括绝缘图案结构和位于所述绝缘图案结构上的金属图案结构。所述绝缘图案结构包括在第一高度在与所述衬底的顶表面平行的第一方向上具有最大深度的凹陷。所述绝缘图案结构包括依次堆叠在所述衬底的所述顶表面上的第一栅极绝缘图案和高k电介质层。所述栅极间隔物包括插入在所述凹陷中的突起。技术研发人员:高相圭,郑爀采,韩相逸,朴正振,金秀炫,李哲,张成豪,张馨元受保护的技术使用者:三星电子株式会社技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240801/248538.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表