一种P沟道器件及其集成电路

- 国知局

- 2024-09-05 14:43:47

本发明涉及半导体器件,尤其是一种p沟道器件及其集成电路。

背景技术:

1、基于半导体材料技术在信息通讯、电力传输、光电器件等领域的广泛应用促进了交通、能源、制造、通讯等领域的革命性发展。在电力能源领域中,诸如高压输电、电动汽车充电桩、雷达等多种应用场景需要能够耐高压的大功率电力电子器件,传统的硅基器件在功率器件领域逼近其材料理论极限,很难进一步大幅度优化。因此,研发基于新一代宽禁带半导体材料的功率器件的必要性逐渐突显。

2、氮化镓(gan)材料由于具有禁带宽度大和关键电场高的特性,gan基功率器件具有击穿电压高的优势,并且可以在高温和辐照等恶劣环境下工作。基于gan材料的高电子迁移率晶体管(high electron mobility transistor,hemt)利用异质结界面由自发和压电极化产生的高密度和高迁移率的二维电子气来传导电流,因此gan基hemt器件具有导通电阻低以及开关速度快的优势,是开发下一代高频高压电力电子器件以及功率集成电路的极具潜力的技术方案之一。目前,利用硅基器件作为外围电路的gan异质集成电路的性能被硅器件限制,不能发挥gan基器件的全部潜力。原因是硅基外围电路需要通过金属导线与gan器件互连,由此引入的寄生电感会严重影响电路的稳定性。此外,由于硅器件本身的工作温度区间较窄且抗辐照性能弱,这也严重限制了gan异质集成电路的应用场景。在同一外延平台上实现全gan集成电路是摆脱硅基外围电路限制和释放gan功率器件和电源系统潜力的关键。基于当前的n沟道gan器件实现gan外围电路的方案主要有电阻-晶体管逻辑电路和直接耦合晶体管逻辑电路,然而上述两种方案的有较大的静态功耗损失。通过引入增强型的p沟道器件与n沟道器件构成互补型逻辑电路可以消除静态功耗损失以及拓展功率器件平台功能。

3、然而,当前商用硅衬底gan基hemt平台上的常关型p沟道器件的电流密度很小,难以与n沟道器件相匹配。通过改变外延结构来引入二维空穴气,利用二维空穴气作为导电沟道可以在一定程度上提高p沟道器件的电流密度,然而上述外延结构与现有的硅衬底gan基hemt器件不兼容,使得gan互补型逻辑电路的难以实现,严重阻碍了gan单片集成电路的广泛应用。

技术实现思路

1、为解决上述问题,本发明的目的在于提供一种p沟道器件及其集成电路,通过在基础层上设置第一n型材料层、p型沟道层和第二n型材料层并构成p沟道器件,便于p沟道器件获得并维持p型工作逻辑,有效提高p沟道器件的电流密度,简化p沟道器件结构的同时也降低了p沟道器件的制备难度,降低集成电路的生产成本。

2、本发明解决其问题所采用的技术方案是:

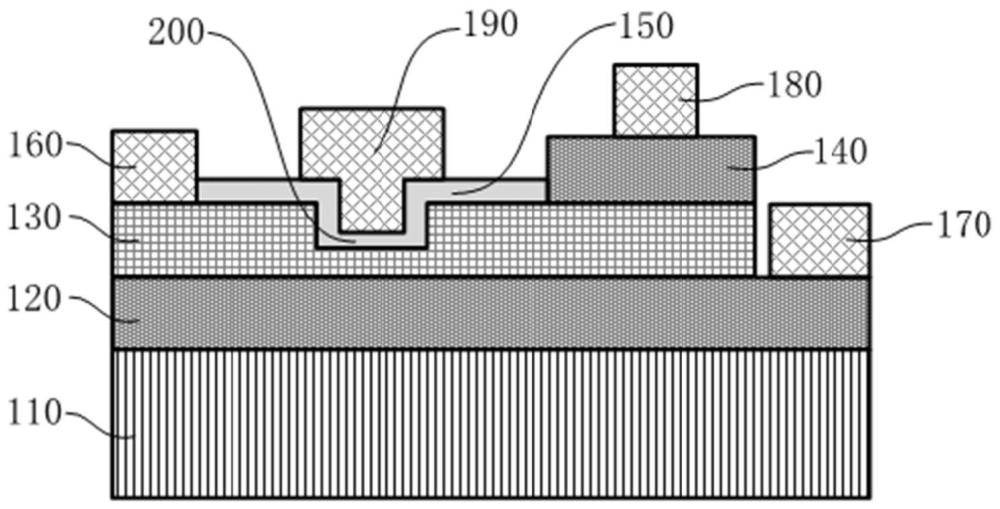

3、第一方面,本技术实施例提供一种p沟道器件,包括:栅介质层、第一源极、第二源极、第一漏极和第一栅极;

4、所述p沟道器件由下至上依次设置有:

5、第一n型材料层,所述第二源极设置在所述第一n型材料层上;

6、p型沟道层,所述p型沟道层设置在所述第一n型材料层上;所述p型沟道层上设有凹槽和所述第一源极,所述栅介质层位于所述凹槽的上方,所述第一栅极设置在所述栅介质层上;

7、第二n型材料层,所述第二n型材料层位于所述p型沟道层上,所述第一漏极设置在所述第二n型材料层上。

8、本技术实施例提供一种p沟道器件,所述第一n型材料层、所述p型沟道层和所述第二n型材料层为多层结构;不同层次的所述第一n型材料层、所述p型沟道层和所述第二n型材料层由不同的主体材料和掺杂元素构成,且不同层次的所述第一n型材料层、所述p型沟道层和所述第二n型材料层具有不同的掺杂浓度。

9、本技术实施例提供一种p沟道器件,所述第一n型材料层的掺杂浓度为0-1022cm-3,所述p型沟道层的掺杂浓度为1012-1022cm-3,所述第二n型材料层的掺杂浓度为1012-1022cm-3。

10、本技术实施例提供一种p沟道器件,所述第一n型材料层、p型沟道层、和所述第二n型材料层的主体材料至少包括氮化镓、氮化铝镓、氮化铟镓、氮化铝铟镓、氮化铝、氧化锌、氧化铟、氧化亚锡、氧化锡、氧化铜以及氧化镍中的一种;所述第一n型材料层、所述p型沟道层、和所述第二n型材料层的掺杂元素至少包括硅、镁、锗、铁、碳以及氧中的一种。

11、本技术实施例提供一种p沟道器件,所述第一n型材料层的下方还设有基础层,所述基础层至少包括衬底、应力缓冲层、沟道层、势垒层和p型材料层中的一种。

12、本技术实施例提供一种p沟道器件,所述基础层的主体材料包括但不限于氮化镓、氮化铝镓、氮化铟镓、氮化铝铟镓、氮化铝、硅、碳化硅、金刚石、氧化铝和氧化镓。

13、本技术实施例提供一种p沟道器件,所述p型沟道层上还设有第一连接电极,第二连接电极和导线;所述第一连接电极和所述第二连接电极分别与所述p型沟道层接触,所述第一连接电极和所述第二连接电极通过所述导线相连。

14、本技术实施例提供一种p沟道器件,所述栅介质层的主体材料至少包括氧化铝、氮化铝、氮氧化铝、氧化硅、氮化硅、氮氧化硅、氧化锆、氮化镓、氮化铝镓、氮化铟镓、氮化铝铟镓、氮化铝中的一种。

15、本技术实施例提供一种p沟道器件,第一n型材料层120的区域由三层第一n型材料层组成,以厚度为50nm以及掺杂浓度为1×1017cm-3的si掺杂gan作为第一层第一n型材料层;以厚度为150nm以及掺杂浓度为3×1018cm-3的si掺杂gan作为第二层第一n型材料层;以厚度为100nm以及掺杂浓度为1×1017cm-3的si掺杂gan作为第三层第一n型材料层;以厚度为100nm以及掺杂浓度为1×1019cm-3的mg掺杂gan作为p型沟道层;以厚度为60nm以及掺杂浓度为1×1019cm-3的si掺杂gan作为第二n型材料层。由ni/au制成第一源极,由ti/al/ti/au制成第二源极,由ni/au制成第一栅极,由ti/al/ti/au制成第一漏极,由氧化铝制成栅介质层,第一源极的材料与p型沟道层的材料形成欧姆接触,第二源极的材料与第一n型材料层的材料形成欧姆接触,第一栅极的材料与第二n型材料层的材料形成欧姆接触。

16、第二方面,本技术实施例提供一种集成电路,包括如上所述的p沟道器件。

17、本技术实施例提供一种集成电路,还包括n沟道器件和基础层,所述基础层位于所述第一n型材料层的下方;所述n沟道器件设有第三源极、第二漏极和第二栅极;所述第三源极、所述第二漏极和所述第二栅极均与所述基础层接触。

18、本技术实施例提供一种集成电路,所述基础层包括沟道层和势垒层;所述沟道层和所述势垒层之间还设有二维电子气。

19、本技术实施例提供一种集成电路,第一n型材料层120的区域由三层第一n型材料层组成,以厚度为50nm以及掺杂浓度为1×1017cm-3的si掺杂gan作为第一层第一n型材料层;以厚度为150nm以及掺杂浓度为3×1018cm-3的si掺杂gan作为第二层第一n型材料层;以厚度为100nm以及掺杂浓度为1×1017cm-3的si掺杂gan作为第三层第一n型材料层;以厚度为100nm以及掺杂浓度为1×1019cm-3的mg掺杂gan作为p型沟道层;以厚度为60nm以及掺杂浓度为1×1019cm-3的si掺杂gan作为第二n型材料层。由ni/au制成第一源极,由ti/al/ti/au制成第二源极,由ni/au制成第一栅极,由ti/al/ti/au制成第一漏极,由氧化铝制成栅介质层,由ti/al/ti/au制成第三源极,由ni/au制成第二栅极,由ti/al/ti/au制成第二漏极,第一源极的材料与p型沟道层的材料形成欧姆接触,第二源极的材料与第一n型材料层的材料形成欧姆接触,第一漏极的材料与第二n型材料层的材料形成欧姆接触,第三源极的材料与二维电子气形成欧姆接触,第二漏极与二维电子气形成欧姆接触,第二栅极与p型材料层形成肖特基接触。

20、本技术实施例,通过设置第一n型材料层、p型沟道层和第二n型材料层并构成p沟道器件,便于p沟道器件获得并维持p型工作逻辑,有效提高p沟道器件的电流密度,简化p沟道器件结构的同时也降低了p沟道器件的制备难度,降低集成电路的生产成本。

21、本技术的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

本文地址:https://www.jishuxx.com/zhuanli/20240905/287882.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表