半导体结构的制作方法

- 国知局

- 2024-09-23 14:26:18

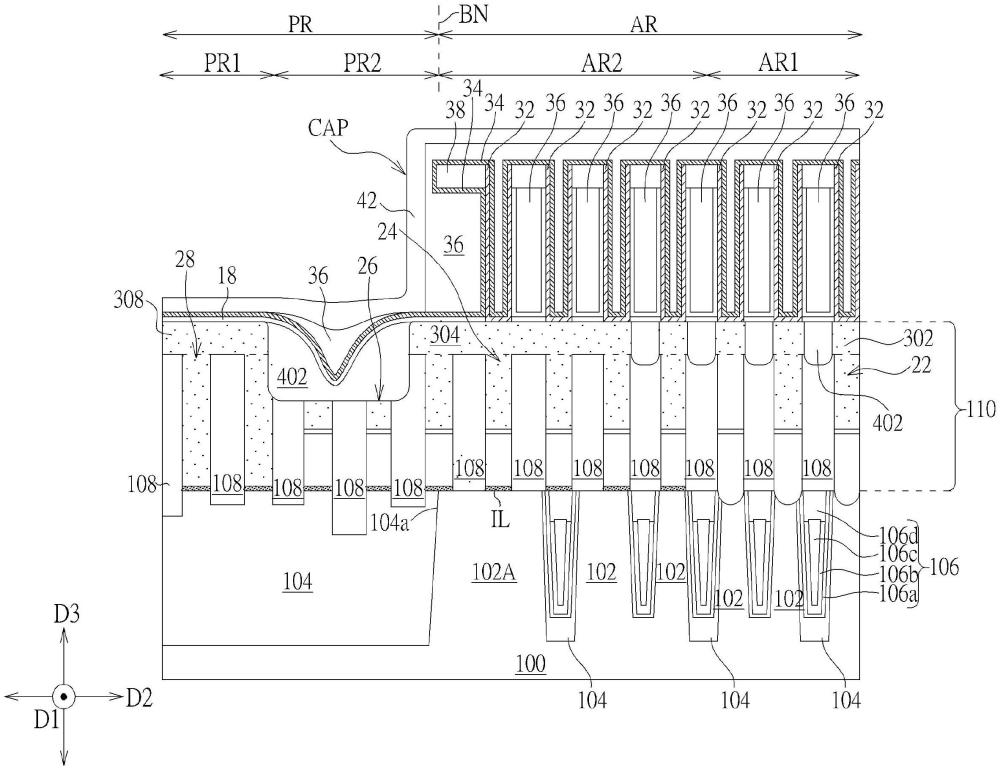

本技术涉及一种半导体结构,特别涉及一种包括分别设置在隔离结构上以及设置在有源区上的插塞结构的半导体结构。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)属于一种挥发性存储器,包括由多个存储单元(memory cell)构成的阵列区(array region)以及由控制电路构成的周边区(peripheral area)。各个存储单元是由一个晶体管(transistor)以及与所述晶体管电性连接的一个电容(capacitor)构成,由所述晶体管控制所述电容中的电荷的存储或释放,来达到存储资料的目的。控制电路通过横跨阵列区并且与各个存储单元电性连接的字线(word line,wl)与位线(bit line,bl),可定址至各个存储单元来控制各个存储单元的资料的存取。

2、为了获得更高集密度的芯片,存储单元的结构已朝向三维(three-dimensional)发展,例如采用埋入式字线连接(buried wordline)以及堆叠式电容(stacked capacitor)技术。堆叠式电容技术是指将存储单元的电容设置在衬底上方,并通过插塞结构及连接垫结构来实现与衬底中的晶体管在垂直方向上的电性连接,藉此节省电容所占用的衬底面积,还可方便地通过增加电容的电极板的高度来获得更大的电容量。然而,目前仍存在一些技术问题须进一步改善,例如周边区应力导致的结构缺陷问题。

技术实现思路

1、本实用新型目的在于提供一种半导体结构,其单元区和周边区上都设有插塞结构,并且在部分插塞结构之间的绝缘结构中设置凹陷,藉此可调节单元区和周边区之间的应力,改善由于应力变化所导致的结构缺陷。另外,与位线接点电连接的周边区互连结构的端部同时与位线接点和设置在位线接点附近的插塞结构一体成型,利用插塞结构埋设在间隔物之间来加强稳固互连结构的端部,减少互连结构的端部发生剥离(peeling)的缺陷。

2、根据本实用新型一实施,半导体结构包括衬底,其包括单元区和周边区,所述周边区包括隔离结构。多个插塞结构设置在所述单元区和所述周边区上,其中所述插塞结构包括至少一个设置在所述周边区的所述隔离结构上的孤立插塞结构。绝缘结构介于所述插塞结构之间,其中所述绝缘结构位于所述孤立插塞结构上的部分包括凹陷。填充材料层位于所述凹陷中。电容结构设置在所述单元区的所述插塞结构上,其中部分所述填充材料层和所述电容结构包括相同的材料。

3、根据本实用新型另一实施,半导体结构包括衬底,其包括隔离结构以及由所述隔离结构定义的有源区。多个插塞结构设置在所述衬底上,包括设置在所述有源区上并且与有源区直接接触的第一插塞结构,以及设置在所述隔离结构上的第二插塞结构,其中所述第二插塞结构的顶面低于所述第一插塞结构的顶面。绝缘层,位于所述隔离结构与第二插塞结构之间。电容结构,设置在所述第一插塞结构上。绝缘结构,介于所述插塞结构之间,其中所述绝缘结构位于所述第二插塞结构上的部分包括凹陷。填充材料层,位于所述凹陷中,其中部分所述填充材料层和所述电容结构包括相同的材料。

技术特征:1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述插塞结构的其中至少一个位于所述隔离结构的边缘上。

3.如权利要求1所述的半导体结构,其特征在于,所述绝缘结构位于所述隔离结构上的部分的底部延伸至所述隔离结构中的不同深度处。

4.如权利要求1所述的半导体结构,其特征在于,还包括:

5.如权利要求4所述的半导体结构,其特征在于,所述位线接点的顶面位于第一高度,所述孤立插塞结构的顶面位于第二高度,所述位线接点的底面位于第三高度,所述第二高度介于所述第一高度和所述第三高度之间。

6.如权利要求4所述的半导体结构,其特征在于,沿着所述位线结构的延伸方向,所述插塞结构至所述单元区的最远距离大于所述位线结构的所述端部至所述单元区的距离。

7.如权利要求1所述的半导体结构,其特征在于,所述电容结构包括:

8.如权利要求7所述的半导体结构,其特征在于,部分所述填充材料层与所述电容介质层包括相同材料。

9.如权利要求7所述的半导体结构,其特征在于,部分所述填充材料层与所述顶电极层包括相同材料。

10.如权利要求7所述的半导体结构,其特征在于,所述填充材料层包括多层结构。

11.如权利要求1所述的半导体结构,其特征在于,所述凹陷的底面高于所述孤立插塞结构的顶表面。

12.如权利要求1所述的半导体结构,其特征在于,还包括多个连接垫,分别位于所述单元区的所述插塞结构上,其中所述绝缘结构包括位于所述插塞结构之间的间隔物,以及位于所述连接垫之间的间隔垫,所述填充材料层的最底部低于所述间隔垫的底面。

13.一种半导体结构,其特征在于,包括:

14.如权利要求13所述的半导体结构,其特征在于,所述电容结构包括:

15.如权利要求14所述的半导体结构,其特征在于,部分所述填充材料层与所述电容介质层包括相同材料。

16.如权利要求14所述的半导体结构,其特征在于,部分所述填充材料层与所述顶电极层包括相同材料。

17.如权利要求14所述的半导体结构,其特征在于,所述填充材料层包括多层结构。

18.如权利要求13所述的半导体结构,其特征在于,所述凹陷的底面高于所述第二插塞结构的顶表面。

19.如权利要求13所述的半导体结构,其特征在于,还包括多个连接垫,分别位于所述第一插塞结构上,其中所述绝缘结构包括位于所述第一插塞结构之间的间隔物,以及位于所述连接垫之间的间隔垫,所述填充材料层的最底部低于所述间隔垫的底面。

技术总结一种半导体结构,包括衬底,衬底包括单元区和周边区。周边区包括隔离结构。多个插塞结构设置在单元区和周边区上。绝缘结构介于插塞结构之间。电容结构设置在单元区的插塞结构上。插塞结构包括至少一个设置在周边区的隔离结构上的孤立插塞结构,其中绝缘结构位于孤立插塞结构上的部分包括凹陷。填充材料层位于凹陷中。部分填充材料层和电容结构包括相同的材料。技术研发人员:吴道初,傅昭伦受保护的技术使用者:福建省晋华集成电路有限公司技术研发日:20240109技术公布日:2024/9/19本文地址:https://www.jishuxx.com/zhuanli/20240923/302856.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表