一种基于图案化起伏二硫化钼沟道的场效应晶体管及其制备方法

- 国知局

- 2024-11-19 09:47:43

本发明属于半导体材料及器件,更具体地,涉及一种基于图案化起伏二硫化钼沟道的场效应晶体管及其制备方法。

背景技术:

1、随着集成电路的快速发展,根据摩尔定律的预测,作为其中最基本电子器件之一的场效应晶体管(fet)的密度将不断提高,其沟道长度将相应地不断缩小。然而,当fet的沟道长度缩减到纳米尺度后将出现短沟道效应,从而降低了fet的性能。短沟道效应出现的特征长度与半导体材料的厚度正相关,但对于硅材料,随着材料厚度的减薄,受介质散射效应影响,其迁移率急剧下降。

2、相比之下,二维材料由于其原子级薄的尺寸,可有效抑制短沟道效应,从而提高器件密度。其中,二硫化钼(mos2)具有优异的物理性质,如单层为直接带隙(1.85ev)、良好的稳定性、出色的受应变调控性能和很高的机械强度,被认为是下一代电子和光电子器件的潜在材料。然而,受限于其强烈声子散射导致的迁移率较低,基于二硫化钼的电子器件的性能还有巨大的提升空间。根据此前的文献报道(nature electronics,2022,5(8):489-496),通过使用起伏的衬底将晶格畸变引入二维二硫化钼,可以减少二维材料中的电子-声子散射,从而提高载流子的迁移率。目前,对于这种起伏衬底上的二硫化钼主要是通过干法或湿法转移技术得到,其步骤繁多,而且不可避免地会引入杂质和缺陷,影响获得结构的晶体质量。例如,现有技术中的转移方式往往是采用机械剥离,得到的单晶晶域小,往往只有10~20μm,转移至图案化起伏的目标衬底上时,只会覆盖起伏的突起处,凹陷处则无法被二硫化钼所覆盖,容易形成空隙、空气腔,产生气泡,影响器件性能。

3、因此,仍亟需探索在起伏衬底上直接大规模制备二硫化钼,并加工制备场效应晶体管器件的有效方法。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本发明的目的在于提供一种基于图案化起伏二硫化钼沟道的场效应晶体管及其制备方法,是通过在图案化起伏的衬底上保形生长单晶二硫化钼薄膜,并经微纳加工制备得到场效应晶体管。本发明利用原位生长在图案化衬底上得到了保形生长的单晶二硫化钼,二硫化钼单晶晶域与图案化衬底之间为紧密接触,没有空隙及气泡,性能优于传统转移方式得到的图案化衬底上二硫化钼薄膜。此外,本发明场效应晶体管制备方法,简便可控、成本低廉、易于大规模制备,且获得的场效应晶体管具有出色的电学性能,因此在实际应用中具备较大的潜能。

2、为实现上述目的,按照本发明的一个方面,提供了一种基于图案化起伏二硫化钼沟道的场效应晶体管,其特征在于,包括二硫化钼层、金属源电极、金属漏电极、绝缘介质层、金属栅电极和图案化起伏的衬底,其中:

3、所述二硫化钼层为单分子层厚度的二硫化钼单晶晶域,该二硫化钼单晶晶域与所述图案化起伏的衬底直接接触,衬底起伏的突起处和凹陷处均被该二硫化钼单晶晶域紧密覆盖;

4、所述金属源电极与所述金属漏电极设置在所述二硫化钼层上,并位于所述二硫化钼层的两端,从而分别形成源极和漏极;

5、所述金属栅电极位于所述二硫化钼层的上方,并通过所述绝缘介质层与所述二硫化钼层相连,从而形成栅极。

6、作为本发明的进一步优选,所述二硫化钼单晶晶域的尺寸为50μm~300μm。

7、作为本发明的进一步优选,所述金属源电极与所述金属漏电极独立的选自铬/金叠层电极、钛/金叠层电极,其中,所述铬/金叠层电极中的铬层用于与所述二硫化钼层直接接触,所述钛/金叠层电极中的钛层用于与所述二硫化钼层直接接触;

8、所述金属栅电极为金、银、铂、钛、铝中的任意一种或多种。

9、作为本发明的进一步优选,所述绝缘介质层为氧化硅层、氧化铝层、氧化铪层或氮化硼层。

10、作为本发明的进一步优选,所述图案化起伏的衬底,具体为图案化起伏的蓝宝石衬底、图案化起伏的二氧化硅衬底或图案化起伏的硅衬底。

11、按照本发明的另一方面,本发明提供了上述基于图案化起伏二硫化钼沟道的场效应晶体管的制备方法,其特征在于,包括以下步骤:

12、s1:图案化衬底上的二硫化钼薄膜的制备,包括以下子步骤:

13、(1)准备图案化起伏的衬底;

14、(2)将钼酸盐分散于水中,配制得到钼源溶液;

15、(3)对洁净的图案化起伏的衬底进行氧等离子体预处理,然后采用旋涂工艺将子步骤(2)得到的钼源溶液涂覆在预处理后衬底的图案化起伏的表面上,接着干燥,从而得到带有钼源层的衬底;

16、(4)以硫粉为硫源,利用化学气相沉积工艺在衬底表面原位生长二硫化钼薄膜,即可得到图案化衬底上的二硫化钼薄膜;所述化学气相沉积工艺具体是采用三温区加热炉,是在通入载气气流的条件下进行化学气相沉的;所述三温区加热炉包括沿气流方向依次分布的第一温区、第二温区和第三温区,带有钼源层的衬底位于第三温区中央,并且钼源层所在的表面能够与载气气流直接接触;硫粉位于第一温区中央,第一温区温度设置为150~250℃,第二温区温度设置为300~450℃,第三温区温度设置为850℃;

17、s2:在步骤s1得到的图案化衬底上的二硫化钼薄膜上,选取某个单分子层厚度的二硫化钼单晶晶域,采用微纳加工工艺分别制备金属源电极、金属漏电极、绝缘介质层和金属栅电极形成源极、漏极和栅极,即可得到基于图案化起伏二硫化钼沟道的场效应晶体管。

18、作为本发明的进一步优选,子步骤(2)中还使用有碱,具体是将钼酸盐和碱按摩尔比大于等于1:1配比然后同时分散于水中,从而配制得到钼源溶液的;

19、所述碱为碱金属氢氧化物。

20、作为本发明的进一步优选,子步骤(2)中,所述钼酸盐选自钼酸钠、钼酸铵;

21、子步骤(3)中,所述洁净的图案化起伏的衬底,具体是将图案化起伏的衬底依次在丙酮、异丙醇、去离子水中超声清洗5min以上,然后用氮气吹干得到的;

22、所述氧等离子体预处理具体是用氧等离子体处理1min以上;

23、所述旋涂工艺所使用的旋涂转速大于1000rpm,旋涂时间大于30s;

24、子步骤(4)中,载气的气流量大于200sccm,化学气相沉的时间为3分钟以上。

25、作为本发明的进一步优选,步骤s2,是先光刻形成源极和漏极的图案,显影后蒸镀金属源电极材料和金属漏电极材料,从而形成源极和漏极;

26、接着,再光刻形成栅极的图案,显影后,先利用介质镀膜工艺形成绝缘介质层,然后再蒸镀金属栅电极材料,从而形成栅极;

27、其中,所述光刻是采用紫外光刻、激光直写或电子束曝光;所述蒸镀是采用热蒸发或电子束蒸发;所述介质镀膜工艺是采用等离子体化学气相沉积、分子束外延或原子层沉积。

28、通过本发明所构思的以上技术方案,与现有技术相比,能够取得以下

29、有益效果:

30、(1)本发明基于图案化起伏的二硫化钼沟道的场效应晶体管及其制备方法,是通过在图案化起伏的衬底上保形生长二硫化钼薄膜,并经微纳加工制备得到场效应晶体管。

31、(2)并且,本发明图案化衬底上二硫化钼薄膜,是通过在图案化起伏的衬底上原位生长单分子层的二硫化钼单晶晶域得到的,具有保形覆盖的特点(即,任意一个二硫化钼单晶晶域下方的衬底区域,衬底起伏的突起处和凹陷处均被该二硫化钼单晶晶域紧密覆盖,没有空隙及气泡),明显区别于传统转移方式得到的图案化衬底上二硫化钼薄膜,有效避免通过繁琐的干法或湿法转移过程中引入的污染和缺陷,性能也更优于传统转移方式得到的图案化衬底上二硫化钼薄膜。

32、同时,本发明得到的单层二硫化钼具有大尺寸、高覆盖率、高质量的特点,尺寸尤其可达50μm~300μm,最大可超过300μm,远大于传统转移方式得到的尺寸为10~20μm的晶域。本发明是首次在图案化衬底上得到了保形生长的大尺寸单晶二硫化钼。基于本发明,可在各种图案化衬底上获得尺寸超过300μm的大尺寸高质量单层二硫化钼。

33、此外,本发明得到的图案化衬底上二硫化钼薄膜,也继承了衬底工程实现对于材料应力的调控。例如,本发明利用图案化起伏的衬底,同样可以对其上的单层二硫化钼施加周期性应力,使得二硫化钼层中产生晶格畸变,有利于减少二维二硫化钼中的电子-声子散射,从而提高载流子的迁移率。

34、(3)本发明所采用的微纳加工工艺与当前集成电路中所使用的工艺兼容,适合于大规模阵列化器件制备与应用。本发明场效应晶体管制备方法,简便可控、成本低廉、易于大规模制备,且获得的场效应晶体管具有出色的电学性能,因此在实际应用中具备较大的潜能。

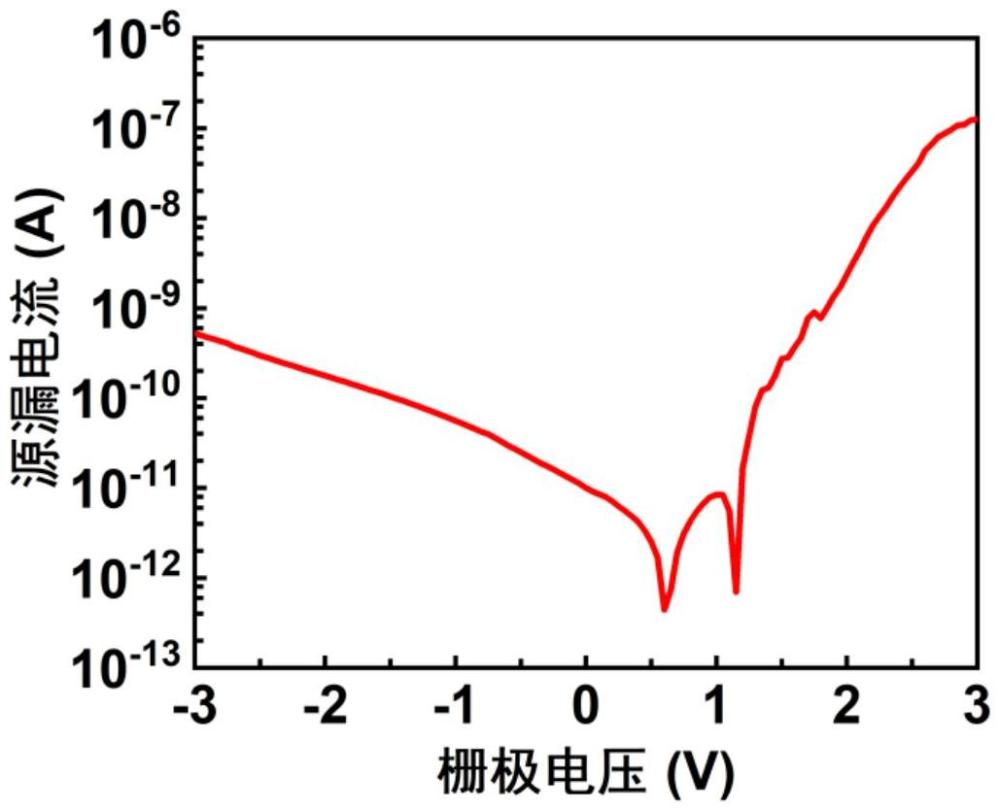

35、(4)本发明得到的基于图案化起伏二硫化钼沟道的场效应晶体管,得益于材料中更少的硫空位缺陷,不同于当前文献中获得的二硫化钼晶体管n型特性(如后文图9所示,复制自acs appl.mater.interfaces 2024,16,18,23771-23779,该文献中场效应晶体管的二硫化钼为在平坦衬底上生长获得),而是表现出双极性特征(如后文图8所示)。

本文地址:https://www.jishuxx.com/zhuanli/20241118/330267.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。