半导体膜镀覆周边制图与补偿的制作方法

- 国知局

- 2024-07-27 11:08:49

本公开内容大致描述监测及调整用于半导体晶片的镀覆处理。更具体地,本公开内容描述了对围绕晶片周缘的晶片密封件或开口图案的状态进行制图,并且任选地在镀覆操作期间响应地调节电流汲取(current stealing)以产生均匀的膜厚度。

背景技术:

1、微电子器件,例如半导体器件,被制造在晶片或工件上和/或中。典型的晶片镀覆处理涉及经由气相沉积将金属种晶层沉积到晶片的表面上。可以沉积和图案化光刻胶以暴露种晶层。然后将晶片移动到电镀处理器的容器中,在容器中电流通过电解液传导到晶片,从而将金属或其他导电材料的覆盖层或图案化层施加到种晶层上。导电材料的示例包括坡莫合金、金、银、铜、钴、锡以及这些金属的合金。后续处理步骤在晶片上形成部件、触点和/或导线。

2、在许多或大多数应用中,镀覆的膜或金属层在整个晶片或工件上具有均匀的厚度是重要的。一些电镀处理器使用窃流器(current thief),窃流器是极性与晶片相同的电极。窃流器通过从晶片的边缘抽取电流来操作。这有助于保持晶片边缘处的镀层厚度与晶片其余部分上的镀层厚度更均匀。窃流器可以是靠近晶片边缘的物理电极。或者,窃流器可以是虚拟窃流器,其中物理电极远离晶片。在这种设计中,来自远距离物理电极的电流通过电解液传导到晶片附近的位置。

3、晶片级封装和其它应用中的电镀处理是相异的,在工艺和晶片图案上有很多不同。经常沿晶片图案的边缘出现显著的镀覆不均匀性。不均匀性可能是由于图案变化引起的电场不规则性或晶片边缘附近的质量传递不均匀性引起的。因此,在设计电镀处理器方面仍然存在工程挑战。

技术实现思路

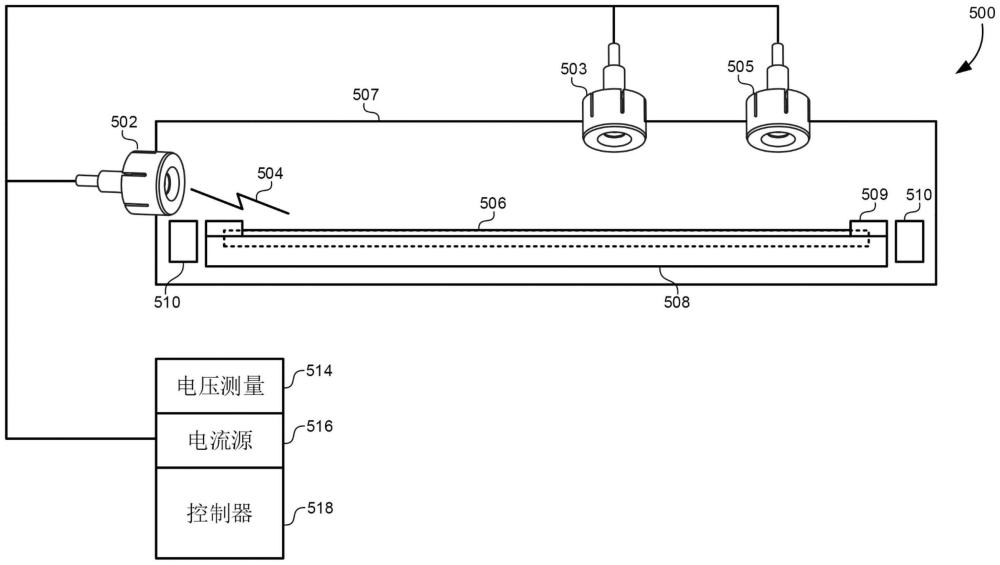

1、在一些实施方式中,一种半导体镀覆系统可包括:容器组件,用于保持电解质和在电解质中的晶片;以及在容器组件中的堰窃流电极(weir thief electrode)组件。堰窃流电极组件可以包括被配置为在镀覆处理期间汲取电流的多个窃流电极。所述系统还可包括:电极,所述电极位于所述容器组件中以在镀覆处理期间浸没在所述电解质中;以及控制器,所述控制器被编程为使电流从所述电极流到所述晶片,并记录电流从所述电极流到晶片上的导电层时测量的与电流相关联的电特性。

2、在一些实施方式中,一种在镀覆处理期间表征晶片周围的密封件的方法可包括使晶片在镀覆室中旋转。所述晶片可被围封于载体中,所述载体形成围绕晶片周缘的密封件,且所述密封件可通过所述密封件内部的电触点电性耦接到晶片上的导电层。所述方法还可包括当晶片旋转时,使电流从镀覆室中的电极流到晶片上的导电层。然后,电流可以通过导电层流到密封件内部的电触点。所述方法可额外地包括使得在电流从电极流到导电层时测量与电流相关联的电特性;以及基于所述电特性生成所述密封件在晶片周缘周围电性耦接到晶片上的导电层的良好程度的表征。

3、在一些实施方式中,一种在镀覆处理期间表征晶片的方法可包括使晶片在镀覆室中旋转。晶片可包括在顶层中的开口,所述开口暴露顶层下方的导电层的区域。所述方法还可包括当晶片旋转时,使电流从镀覆室中的电极流到晶片上的导电层;在电流从电极流到导电层时测量与电流相关联的电特性;以及基于所述电特性生成顶层中的开口的表征。

4、在任意实施方式中,可以以任意组合且不受限制地实施以下特征中的任意和全部特征。所述电极不需要是堰窃流电极组件的一部分,并且在镀覆处理期间所述电极不需要从晶片汲取电流。所述电极可以安装在容器组件的壳体中。所述控制器可进一步编程为在镀覆处理期间调整由所述多个窃流电极汲取的电流量。在镀覆处理期间,电极和晶片可以浸没在电解质中,使得电流通过电解质从电极流到晶片。所述系统还可以包括位于容器组件中且位于晶片的内半径上方的第二电极。所述控制器可进一步编程为使第二电流从所述第二电极流到所述晶片,且记录所述第二电流从第二电极流到导电层时测量的与所述第二电流相关联的第二电特性。镀覆处理可以包括在晶片的一部分上添加导电材料的电镀处理。所述电流可以包括来自电流源的恒定电流。与电流相关联的电特性可以包括当晶片旋转时驱动恒定电流所需的电压。所述方法/操作还可包括生成与晶片周缘周围的位置相对应的电压图,其中较高电压可表示所述密封件未通过所述密封件内部的电触点充分电性耦接到导电层的区域。晶片上的导电层可以包括在密封件下方延伸的均匀种晶层,并且均匀种晶层可以是晶片上的最顶层,在均匀种晶层的顶部上没有掩模层。所述电流可以包括来自电流源的恒定电流,并且与电流相关联的电特性包括当晶片旋转时驱动恒定电流所需的电压。所述方法还可包括生成与晶片周缘周围的位置相对应的电压图,其中较高电压可表示顶层中的开口最稀疏的位置。该方法/操作还可以包括基于顶层中的开口的表征来调整由一个或多个窃流电极汲取的电流量。一个或多个窃流电极可在晶片上顶层中的开口最稀疏的位置处汲取较多电流。一个或多个窃流电极可以在晶片上顶层中的开口最密集的位置处汲取较少电流。所述方法/操作还可包括组合所述密封件电性耦接到第二晶片上的导电层的良好程度的表征和顶层中的开口的表征以生成晶片的制图。

技术特征:1.一种半导体镀覆系统,包括:

2.如权利要求1所述的半导体镀覆系统,其中所述电极不是所述堰窃流电极组件的一部分,并且所述电极在所述镀覆处理期间不从所述晶片汲取电流。

3.如权利要求1所述的半导体镀覆系统,其中所述电极安装在所述容器组件的壳体中。

4.如权利要求1所述的半导体镀覆系统,其中所述控制器进一步编程为在所述镀覆处理期间调整由所述多个窃流电极汲取的电流量。

5.如权利要求1所述的半导体镀覆系统,其中在所述镀覆处理期间,所述电极和所述晶片浸没在电解质中,使得所述电流从所述电极通过所述电解质流到所述晶片。

6.如权利要求1所述的半导体镀覆系统,其中所述半导体镀覆系统还包括:

7.如权利要求1所述的半导体镀覆系统,其中所述镀覆处理包括将导电材料添加到所述晶片的一部分的电镀处理。

8.一种在镀覆处理期间表征晶片周围的密封件的方法,所述方法包括:

9.如权利要求8所述的方法,其中所述电流包括来自电流源的恒定电流。

10.如权利要求9所述的方法,其中与所述电流相关联的所述电特性包括当所述晶片旋转时驱动所述恒定电流所需的电压。

11.如权利要求10所述的方法,还包括生成与所述晶片的周缘周围的位置相对应的电压图,其中较高的电压表示所述密封件未通过所述密封件内的所述电触点充分电性耦接到所述导电层的区域。

12.如权利要求8所述的方法,其中所述晶片上的所述导电层包括在所述密封件下方延伸的均匀种晶层,并且所述均匀种晶层是所述晶片上的最顶层,在所述均匀种晶层的顶部上没有掩模层。

13.一种在镀覆处理期间表征晶片的方法,所述方法包括:

14.如权利要求13所述的方法,其中所述电流包括来自电流源的恒定电流,并且与所述电流相关联的所述电特性包括当所述晶片旋转时驱动所述恒定电流所需的电压。

15.如权利要求14所述的方法,进一步包括生成与所述晶片的周缘周围的位置相对应的电压图,其中较高的电压表示所述顶层中的开口最稀疏的位置。

16.如权利要求13所述的方法,进一步包括基于所述顶层中的开口的所述表征来调整由一个或多个窃流电极汲取的电流量。

17.如权利要求16所述的方法,其中所述一个或多个窃流电极在所述晶片上所述顶层中的开口最稀疏的位置处汲取更多电流。

18.如权利要求16所述的方法,其中所述一个或多个窃流电极在所述晶片上所述顶层中的开口最密集的位置处汲取较少的电流。

19.如权利要求13所述的方法,进一步包括:

20.如权利要求19所述的方法,进一步包括:

技术总结晶片周边处的状态可被表征并可用于调节在镀覆处理期间由堰窃流电极汲取的电流,以产生更均匀的膜厚度。当晶片旋转时,电极可位于镀覆室中且在晶片周缘附近。为了表征密封件上的电触点,可以将具有种晶层的晶片装载到镀覆室中,并且可驱动恒定电流通过电极到晶片上的导电层。随着该电流的电特性,例如驱动恒定电流所需的电压,变化,可生成表征密封件质量或掩模层中的开口的制图。技术研发人员:凯尔·M·汉森受保护的技术使用者:应用材料公司技术研发日:技术公布日:2024/4/29本文地址:https://www.jishuxx.com/zhuanli/20240726/117633.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

水电解系统的制作方法

下一篇

返回列表