用于存储系统接口电路的信号处理方法和装置与流程

- 国知局

- 2024-07-31 19:13:03

本申请涉及一种信号处理技术,具体而言,涉及一种用于存储系统接口电路的信号处理方法和装置。

背景技术:

1、随着计算机系统对存储数据的性能要求越来越高,存储系统的信号链路上的数据读写频率也越来越高。目前的双倍速率(ddr)存储系统通常采用单端信号并行传输,因而难以避免大量的信号串扰影响信号传输。这些信号串扰例如是线与线之间的串扰、或者过孔等垂直结构之间的串扰,等等。另一方面,系统的多点(multi-drop)传输会导致阻抗不匹配,这会引起串扰信号的严重反射,串扰引起的码间干扰也比较大。因此,对于存储系统信号链路中的命令地址信号和数据信号,它们的远端串扰都显著缩小了接收端眼图的裕量。

2、常规连续时间串扰消除(continuous time crosstalk cancellation,ctxc)技术和自适应连续时间串扰消除技术通过电路实现串扰源(aggressor)信号对受干扰(victim)信号的微分补偿,可以消除串扰对时序裕量的影响。但是,微分补偿电路的调节需要额外的模拟电路硬件开销和功耗开销。此外,对于串扰反射严重、拖尾较长的ddr存储系统而言,ctxc电路的效果也是有限的。

3、目前的ddr存储系统开始考虑在cpu封装上优化串扰,以及在印刷电路板上利用一种特殊的tabbed routing技术来减小串扰,但是在接收端并未针对信号串扰做特别地处理。

4、有鉴于此,需要一种改进的用于存储系统的信号处理方法及机制。

技术实现思路

1、本申请的一个目的是提供一种用于存储系统接口电路的信号处理方法,用于改善信号完整性。

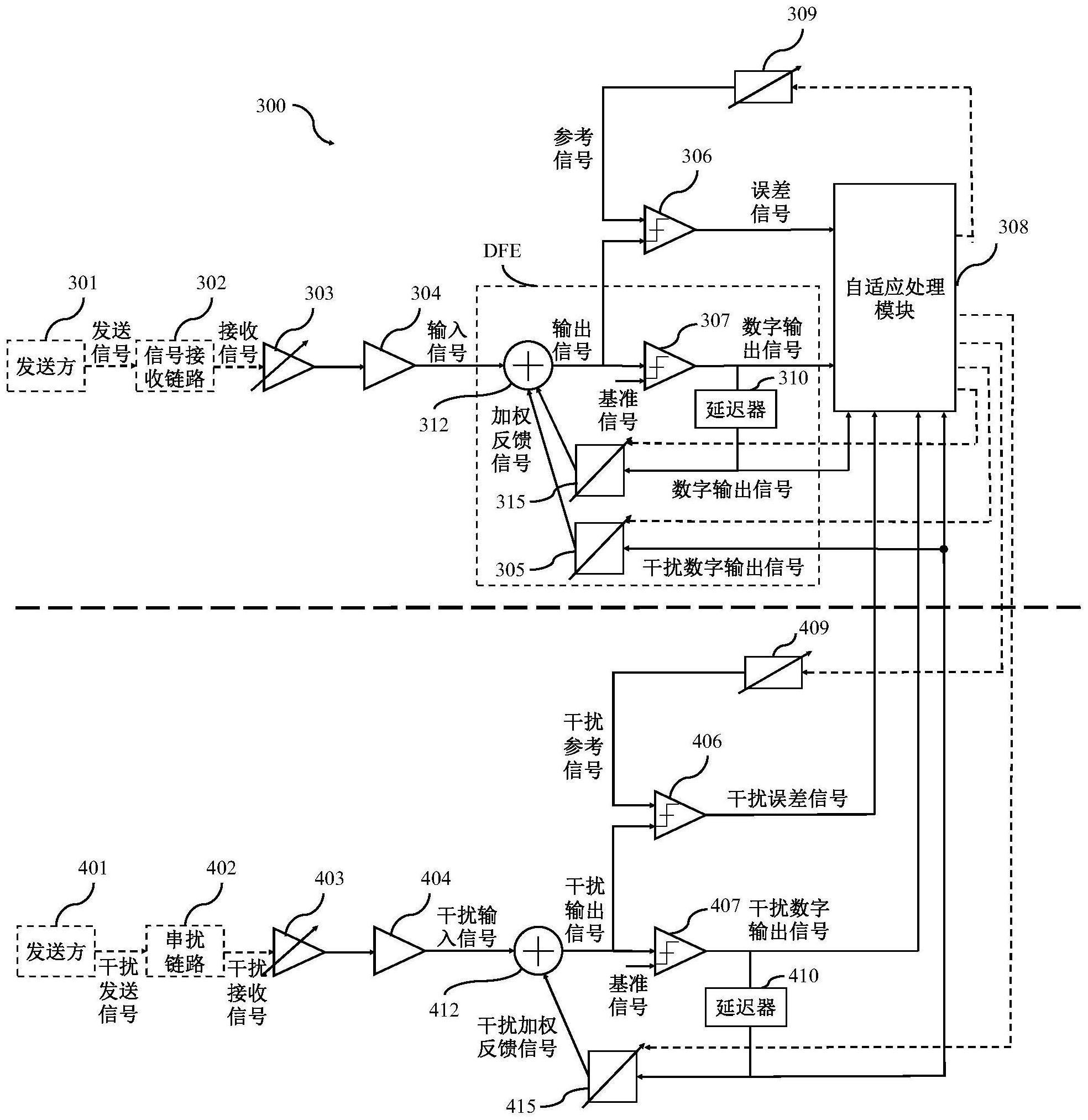

2、根据本申请的一方面,提供一种用于存储系统接口电路的信号处理方法。所述存储系统接口电路包括至少两个信号引脚,其中每个信号引脚经由分别的信号接收链路接收发送信号并在所述信号接收链路的接收端产生接收信号,所述方法包括:对目标信号引脚的目标信号接收链路的接收端处产生的接收信号进行预处理,以得到输入信号,其中所述目标信号引脚是所述至少两个信号引脚中的一个信号引脚;从所述输入信号中去除加权反馈信号以得到输出信号,其中所述加权反馈信号是通过反馈路径中的有限长单位冲激响应fir滤波器提供的;基于预定基准信号对所述输出信号进行判决以生成数字输出信号;生成串扰链路相关的干扰数字输出信号,其中所述串扰链路是邻近所述目标信号接收链路的信号接收链路,其对应于所述至少两个信号引脚中的另一信号引脚,并且所述串扰链路的传输特性干扰所述目标信号接收链路并使得所述接收信号中产生码间干扰;经由所述fir滤波器的滤波系数矩阵对所述干扰数字输出信号进行加权,以得到加权反馈信号;将所述输出信号与参考信号进行比较以产生误差信号;以及根据所述干扰数字输出信号与所述误差信号之间的相关性来确定所述fir滤波器的滤波系数矩阵的一组优化滤波系数,以及根据所述数字输出信号与所述误差信号之间的相关性来确定所述参考信号,以至少部分地减小由所述串扰链路的传输特性引入所述接收信号中的码间干扰。

3、根据本申请的另一方面,提供了一种用于接口电路的信号处理装置,其特征在于,所述存储系统接口电路包括具有至少两个信号引脚,其中每个信号引脚经由分别的信号接收链路接收发送信号并在所述信号接收链路的接收端产生接收信号,针对所述至少两个信号引脚中的一个目标信号引脚,所述信号处理装置包括:预处理模块,其配置成对所述目标信号引脚的目标信号接收链路的接收端处产生的接收信号进行预处理,以得到输入信号;判决反馈均衡器,所述判决反馈均衡器包括其中耦接有输出采样器的输出路径、以及其中耦接有有限长单位冲激响应fir滤波器的反馈路径;所述判决反馈均衡器被配置成从所述输入信号中去除加权反馈信号以得到输出信号,并且由所述输出采样器基于预定基准信号对所述输出信号进行判决以生成数字输出信号;其中所述加权反馈信号是由所述fir滤波器的滤波系数矩阵对干扰数字输出信号进行加权得到的,其中所述串扰链路是邻近所述目标信号接收链路的信号接收链路,其对应于所述至少两个信号引脚中的另一信号引脚,并且所述串扰链路的传输特性干扰所述目标信号接收链路并使得所述接收信号中产生码间干扰;误差采样器,其配置成将所述输出信号与参考信号进行比较以产生误差信号;以及自适应处理模块,其配置成根据所述干扰数字输出信号与所述误差信号之间的相关性来确定所述fir滤波器的滤波系数矩阵的一组优化滤波系数,以及根据所述数字输出信号与所述误差信号之间的相关性来确定所述参考信号,以至少部分地减小由所述串扰链路的传输特性引入所述接收信号中的码间干扰。

4、以上为本申请的概述,可能有简化、概括和省略细节的情况,因此本领域的技术人员应该认识到,该部分仅是示例说明性的,而不旨在以任何方式限定本申请范围。本概述部分既非旨在确定所要求保护主题的关键特征或必要特征,也非旨在用作为确定所要求保护主题的范围的辅助手段。

技术特征:1.一种用于存储系统接口电路的信号处理方法,其特征在于,所述存储系统接口电路包括至少两个信号引脚,其中每个信号引脚经由分别的信号接收链路接收发送信号并在所述信号接收链路的接收端产生接收信号,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述预处理包括以下至少一种:连续时间线性均衡处理、增益处理或这两者的组合。

3.根据权利要求1所述的方法,其特征在于,根据所述数字输出信号与所述误差信号之间的相关性来确定所述参考信号包括:

4.根据权利要求3所述的方法,其特征在于,以预定参考步长更新所述参考信号包括:

5.根据权利要求4所述的方法,其特征在于,以最小均方算法来确定所述参考信号包括以下式更新所述参考信号:

6.根据权利要求4所述的方法,其特征在于,以符号符号最小均方算法来确定所述参考信号包括以下式更新所述参考信号:

7.根据权利要求1所述的方法,其特征在于,所述fir滤波器包括m级,其中m为正整数,根据所述干扰数字输出信号与所述误差信号之间的相关性来确定所述fir滤波器的滤波系数矩阵的一组优化滤波系数包括:

8.根据权利要求7所述的方法,其特征在于,以预定滤波步长更新所述第k级的滤波系数包括:

9.根据权利要求8所述的方法,其特征在于,以最小均方算法来确定所述第k级的滤波系数包括以下式更新所述滤波系数:

10.根据权利要求8所述的方法,其特征在于,以符号符号最小均方算法来确定所述第k级的滤波系数包括以下式更新所述滤波系数:

11.根据权利要求1所述的方法,其特征在于,所述发送信号为随机生成的信号或伪随机序列。

12.根据权利要求1所述的方法,其特征在于,所述方法被以预定时间间隔重复地执行,以重新确定所述fir滤波器的滤波系数矩阵的一组优化滤波系数以及所述参考信号。

13.根据权利要求1所述的方法,其特征在于,所述存储系统接口电路被集成在存储器控制器的存储器接口中。

14.根据权利要求1所述的方法,其特征在于,所述存储系统接口电路被集成在存储模块的接口中。

15.根据权利要求1所述的方法,其特征在于,生成串扰链路相关的干扰数字输出信号包括:

16.根据权利要求15所述的方法,其特征在于,所述干扰发送信号与所述发送信号是相同类型的并行信号。

17.一种用于接口电路的信号处理装置,其特征在于,所述存储系统接口电路包括具有至少两个信号引脚,其中每个信号引脚经由分别的信号接收链路接收发送信号并在所述信号接收链路的接收端产生接收信号,针对所述至少两个信号引脚中的一个目标信号引脚,所述信号处理装置包括:

18.根据权利要求17所述的信号处理装置,其特征在于,所述自适应处理模块被配置为以最小均方算法来确定所述参考信号,其基于下式更新所述参考信号:

19.根据权利要求17所述的信号处理装置,其特征在于,所述自适应处理模块被配置为以符号符号最小均方算法来确定所述参考信号,其基于下式更新所述参考信号:

20.根据权利要求17所述的信号处理装置,其特征在于,所述fir滤波器包括m级,其中m为正整数,所述自适应处理模块配置成以最小均方算法来确定所述滤波系数,其基于下式更新所述滤波系数:

21.根据权利要求17所述的信号处理装置,其特征在于,所述fir滤波器包括m级,其中m为正整数,所述自适应处理模块配置成以符号符号最小均方算法来确定所述滤波系数,其基于下式更新所述滤波系数:

22.根据权利要求17所述的信号处理装置,其特征在于,所述发送信号为随机生成的信号或伪随机信号。

23.根据权利要求22所述的信号处理装置,其特征在于,所述发送信号是循环移位寄存器产生的伪随机信号。

24.根据权利要求17所述的信号处理装置,其特征在于,所述自适应处理模块配置成根据随机生成的发送信号以预定时间间隔重新确定所述fir滤波器的滤波系数。

25.根据权利要求17所述的信号处理装置,其特征在于,所述干扰数字输出信号是通过下述方式生成的:

26.根据权利要求25所述的方法,其特征在于,所述干扰发送信号与所述发送信号是相同类型的并行信号。

27.一种存储器控制器,包括根据权利要求17至26中任一项所述的信号处理装置。

28.根据权利要求27所述的存储器控制器,其特征在于,所述存储器控制器是寄存时钟驱动器或数据缓冲器。

29.一种存储模块,包括根据权利要求17至26中任一项所述的信号处理装置。

30.一种计算机可读存储介质,其中存储有指令,当所述指令由处理器执行时,使得所述处理器执行如权利要求1-16中任一项所述的信号处理方法。

技术总结本申请涉及用于存储系统接口电路的信号处理方法,包括:对接收信号进行预处理,以得到输入信号;从输入信号中去除加权反馈信号以得到输出信号;基于预定基准信号对输出信号进行判决以生成数字输出信号;生成串扰链路相关的干扰数字输出信号;经由所述FIR滤波器的滤波系数矩阵对所述干扰数字输出信号进行加权,以得到加权反馈信号;将所述输出信号与参考信号进行比较以产生误差信号;以及根据所述干扰数字输出信号与所述误差信号之间的相关性来确定所述FIR滤波器的滤波系数矩阵的一组优化滤波系数,以及根据所述数字输出信号与所述误差信号之间的相关性来确定所述参考信号,以至少部分地减小由所述串扰链路的传输特性引入所述接收信号中的码间干扰。技术研发人员:祖秋艳,孙春来,严钢,王勇,王武广受保护的技术使用者:澜起电子科技(昆山)有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181893.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表