半导体存储装置的制作方法

- 国知局

- 2024-07-31 19:24:48

本发明的实施方式涉及半导体存储装置。

背景技术:

1、作为半导体存储装置,已知有nand型闪速存储器。

技术实现思路

1、在本发明的一个实施方式中,提供一种能够抑制芯片面积的增加的半导体存储装置。

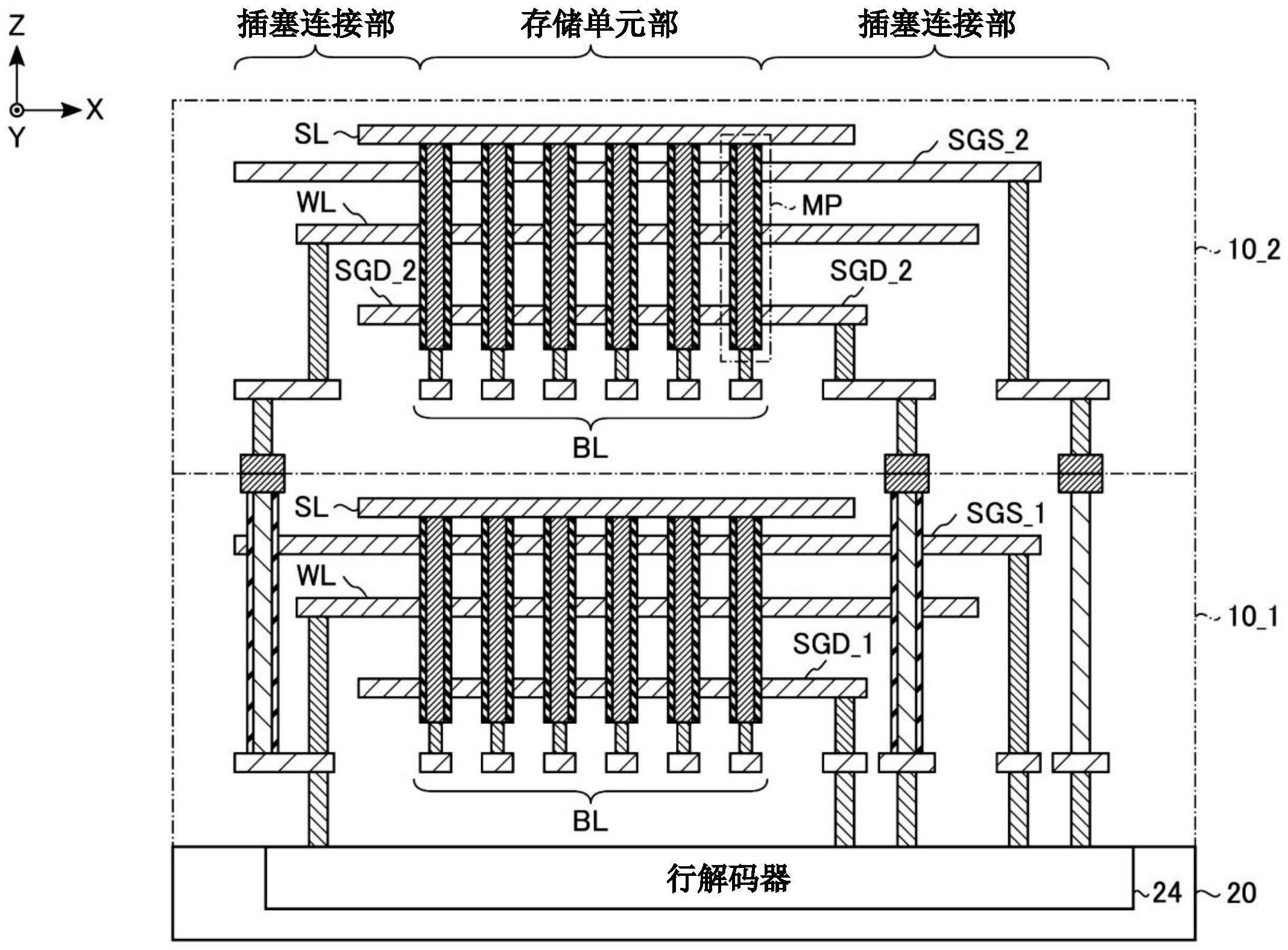

2、实施方式所涉及的半导体存储装置包含第一存储单元阵列、在第一方向上配置在所述第一存储单元阵列的上方的第二存储单元阵列、以及行解码器。所述第一存储单元阵列包含:沿所述第一方向配置且串联连接的第一选择晶体管、第一存储单元及第二选择晶体管;在与所述第一方向相交的第二方向上延伸且与所述第一存储单元连接的第一字线;在所述第二方向上延伸且与所述第一选择晶体管连接的第一选择栅极线;以及在所述第二方向上延伸且与所述第二选择晶体管连接的第二选择栅极线。所述第二存储单元阵列包含:沿所述第一方向配置且串联连接的第三选择晶体管、第二存储单元及第四选择晶体管;在所述第二方向上延伸且与所述第二存储单元连接的第二字线;在所述第二方向上延伸且与所述第三选择晶体管连接的第三选择栅极线;以及在所述第二方向上延伸且与所述第四选择晶体管连接的第四选择栅极线。所述第一字线和所述第二字线共通地连接到所述行解码器。所述第一选择栅极线、所述第二选择栅极线、所述第三选择栅极线和所述第四选择栅极线分别与所述行解码器连接。

3、根据上述的构成,能够提供一种能抑制芯片面积的增加的半导体存储装置。

技术特征:1.一种半导体存储装置,具备:

2.根据权利要求1所述的半导体存储装置,其中,

3.根据权利要求1或2所述的半导体存储装置,其中,

4.根据权利要求1所述的半导体存储装置,其中,

5.根据权利要求1所述的半导体存储装置,其中,

6.根据权利要求1所述的半导体存储装置,其中,

7.根据权利要求1所述的半导体存储装置,其中,

8.根据权利要求7所述的半导体存储装置,其中,

9.根据权利要求1所述的半导体存储装置,其中,

技术总结根据实施方式,半导体存储装置包含第一存储单元阵列(11_1)和第二存储单元阵列(11_2)。第一存储单元阵列包含第一存储单元(MC)、第一选择晶体管(ST1)、第二选择晶体管(ST2)、第一字线(WL)、第一选择栅极线(SGD_1)和第二选择栅极线(SGS_1)。第二存储单元阵列包含第二存储单元(MC)、第三选择晶体管(ST1)、第四选择晶体管(ST2)、第二字线(WL)、第三选择栅极线(SGD_2)和第四选择栅极线(SGS_2)。第一字线和第二字线共通地连接到行解码器(24)。第一选择栅极线、第二选择栅极线、第三选择栅极线和第四选择栅极线分别与行解码器连接。技术研发人员:中木寛,中塚圭祐受保护的技术使用者:铠侠股份有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182501.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表