多项目晶圆测试系统及方法与流程

- 国知局

- 2024-07-31 19:34:00

本发明涉及半导体,特别涉及一种多项目晶圆测试系统及方法。

背景技术:

1、在半导体行业,在产品量产之前,需要对设计的产品进行样片验证以验证设计是否存在缺陷,以免对量产造成损失。或者是有些机构或公司,其设计的产品无需量产仅需要生产少量的芯片进行验证。这时芯片代工厂(foundry)提供了一项服务,即多个项目(产品)制造在同一个晶圆上(multi project wafer,mpw),mpw业务既满足了相关方的需求,又有效的降低了费用。

2、mpw虽然有效降低了设计新产品芯片的制版费用,但是通常不同的产品芯片测试的探针卡及测试程序是不同的,目前在对mpw晶圆的测试中,往往是采用单测进行测试的。尤其,涉及到含有存储器(存储单元)的产品,即便是测试端口通道完全相同,测试的存储器容量大小不同时,也必须使用不同的测试程序进行测试。因此,有必要降低多项目晶圆的测试成本。

技术实现思路

1、本发明的目的在于提供一种多项目晶圆测试方法及系统,用以降低多项目晶圆的存储单元的测试成本。

2、为解决上述技术问题,本发明提供的多项目晶圆测试系统,包括:

3、基板,其一个曝光区上设有第一至第n待测存储单元,所述第一至第n待测存储单元具有相同的测试端口且其中至少一个具有不同的存储容量,n为大于或等于2的整数;

4、多同测探针卡,其针位涵盖至少一个曝光区的所述第一至第n待测存储单元的测试端口;

5、多同测试模块,将所述第一至第n待测存储单元的各测试向量以周期整合为统一向量,利用所述多同测探针卡及所述统一向量对所述基板上的第一至第n待测存储单元以并行方式执行功能测试,直至存储容量最大的待测存储单元完成功能测试。

6、可选的,所述基板为多项目晶圆,所述多项目晶圆的一个曝光区具有第一至第n待测器件,所述第一至第n待测器件各自具有对应的所述第一至第n待测存储单元。

7、可选的,所述多同测试模块包括自动测试机、运行于所述自动测试机上的主测试程序及执行于所述主测试程序上的统一向量,所述主测试程序以多个相同待测器件并行测试的架构构建,所述统一向量的各通道根据所述第一至第n待测存储单元的实际排布定义。

8、可选的,所述统一向量的各通道均能施加或读取信号状态。

9、可选的,所述第一至第n待测存储单元具有多个测试模式,所述第一至第n待测存储单元的各测试模式下的测试向量分别整合至所述多同测试模块对应测试模式下的统一向量。

10、可选的,所述第一至第n待测存储单元均为嵌入式非易失存储结构,所述第一至第n待测存储单元包括擦除测试模式、编程测试模式及读取测试模式。

11、可选的,以所述第一至第n待测存储单元中的最大存储容量作为所述统一向量的每个通道的统一长度,所述统一向量对其中存储容量小于所述最大存储容量的通道填充至所述统一长度并使其io口处于高阻态或非写非比较态。

12、可选的,采用发送休眠命令或停止时钟命令以使对应待测存储单元的io口处于高阻态或非写非比较态。

13、可选的,所述多同测试模块还利用所述多同测探针卡对所述基板上的第一至第n待测存储单元进行交流参数测量及直流参数测量。

14、基于本发明的另一方面,还提供一种多项目晶圆测试方法,包括:

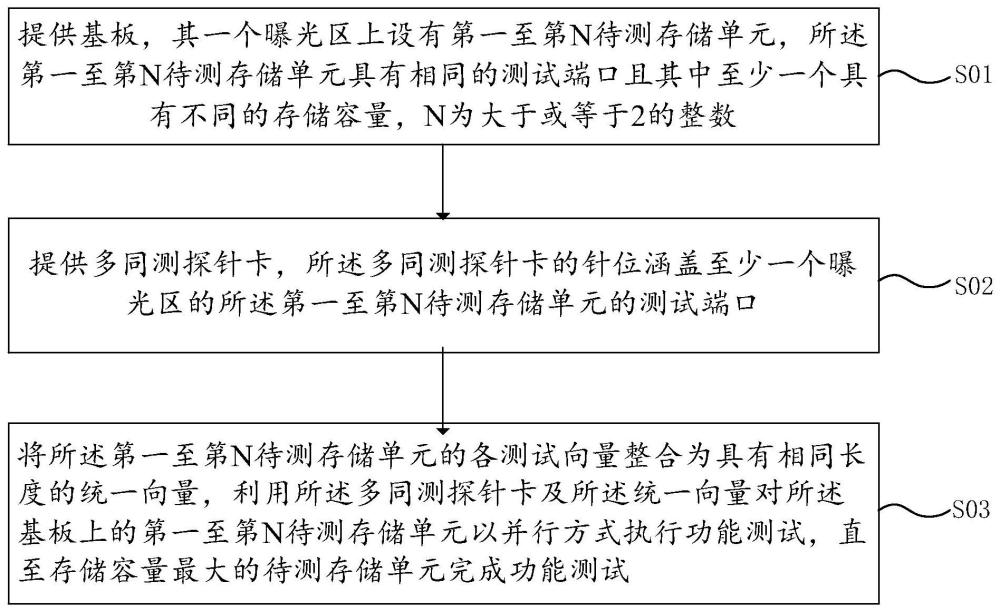

15、提供基板,其一个曝光区上设有第一至第n待测存储单元,所述第一至第n待测存储单元具有相同的测试端口且其中至少一个具有不同的存储容量,n为大于或等于2的整数;

16、提供多同测探针卡,所述多同测探针卡的针位涵盖至少一个曝光区的所述第一至第n待测存储单元的测试端口;

17、将所述第一至第n待测存储单元的各测试向量整合为具有相同长度的统一向量,利用所述多同测探针卡及所述统一向量对所述基板上的第一至第n待测存储单元以并行方式执行功能测试,直至存储容量最大的待测存储单元完成功能测试。

18、综上所述,本发明对基板一个曝光区上具有相同测试端口且不同存储容量的第一至第n待测存储单元以并行地方式进行功能测试,其中,探针卡的针位涵盖至少一个曝光区的第一至第n待测存储单元的测试端口,在利用探针卡及测试模块进行功能测试时,将第一至第n待测存储单元的各测试向量据周期整合为具有相同长度的统一向量,并对上述第一至第n待测存储单元同时进行测试,直至存储容量最大的待测存储单元完成功能测试,从而实现同时测量基板上多个不同的待测存储单元,提高测试效率,降低测试成本。

技术特征:1.一种多项目晶圆测试系统,其特征在于,包括:

2.根据权利要求1所述的多项目晶圆测试系统,其特征在于,所述基板为多项目晶圆,所述多项目晶圆的一个曝光区具有第一至第n待测器件,所述第一至第n待测器件各自具有对应的所述第一至第n待测存储单元。

3.根据权利要求1所述的多项目晶圆测试系统,其特征在于,所述多同测试模块包括自动测试机、运行于所述自动测试机上的主测试程序及执行于所述主测试程序上的统一向量,所述主测试程序以多个相同待测器件并行测试的架构构建,所述统一向量的各通道根据所述第一至第n待测存储单元的实际排布定义。

4.根据权利要求3所述的多项目晶圆测试系统,其特征在于,所述统一向量的各通道均能施加或读取信号状态。

5.根据权利要求3所述的多项目晶圆测试系统,其特征在于,所述第一至第n待测存储单元具有多个测试模式,所述第一至第n待测存储单元的各测试模式下的测试向量分别整合至所述多同测试模块对应测试模式下的统一向量。

6.根据权利要求5所述的多项目晶圆测试系统,其特征在于,所述第一至第n待测存储单元均为嵌入式非易失存储结构,所述第一至第n待测存储单元包括擦除测试模式、编程测试模式及读取测试模式。

7.根据权利要求3所述的多项目晶圆测试系统,其特征在于,以所述第一至第n待测存储单元中的最大存储容量作为所述统一向量的每个通道的统一长度,所述统一向量对其中存储容量小于所述最大存储容量的通道填充至所述统一长度并使其io口处于高阻态或非写非比较态。

8.根据权利要求7所述的多项目晶圆测试系统,其特征在于,采用发送休眠命令或停止时钟命令以使对应待测存储单元的io口处于高阻态或非写非比较态。

9.根据权利要求1所述的多项目晶圆测试系统,其特征在于,所述多同测试模块还利用所述多同测探针卡对所述基板上的第一至第n待测存储单元进行交流参数测量及直流参数测量。

10.一种多项目晶圆测试方法,其特征在于,包括:

技术总结本发明提供了一种多项目晶圆测试系统及方法,所述测试系统包括:基板,其一个曝光区上设有第一至第N待测存储单元,第一至第N待测存储单元具有相同的测试端口且其中至少一个具有不同的存储容量;多同测探针卡,其针位涵盖至少一个曝光区的第一至第N待测存储单元的测试端口;多同测试模块,将第一至第N待测存储单元的各测试向量以周期整合为统一向量,利用多同测探针卡及统一向量对基板上的第一至第N待测存储单元以并行方式执行功能测试,直至存储容量最大的待测存储单元完成功能测试。本发明中,通过实现对具有相同测试端口但存储容量不同的多个待测存储单元同时进行功能测试,从而提高测试效率,降低成本。技术研发人员:谢晋春受保护的技术使用者:上海华虹宏力半导体制造有限公司技术研发日:技术公布日:2024/1/22本文地址:https://www.jishuxx.com/zhuanli/20240731/183093.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表