用于减少长代码的门数的混合精度MS解码器的制作方法

- 国知局

- 2024-07-31 19:42:20

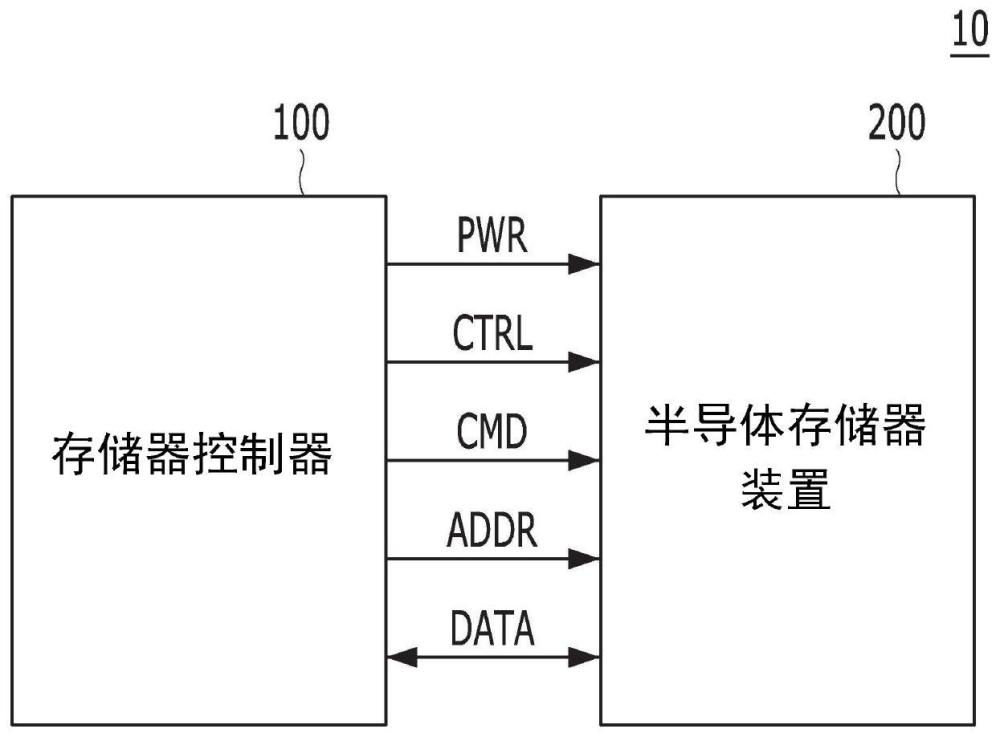

本公开的实施例涉及一种具有解码器的存储器系统以及操作这种系统和解码器的方法,具体地,涉及解码失败预测。

背景技术:

1、计算机环境范例已经转变为可以随时随地使用的普适计算系统。因此,诸如移动电话、数码相机和笔记本电脑的便携式电子装置的使用迅速增加。这些便携式电子装置通常使用具有存储器装置即数据存储装置的存储器系统。数据存储装置用作便携式电子装置的主存储器装置或辅助存储器装置。

2、因为使用存储器装置的数据存储装置不具有移动部件,所以使用存储器装置的数据存储装置提供了优异的稳定性、耐久性、高信息访问速度和低功耗。具有这种优点的数据存储装置的示例包括通用串行总线(usb)存储器装置、具有各种接口的存储卡、以及固态驱动器(ssd)。

3、ssd可以包括闪速存储器组件和控制器,该控制器包括将闪速存储器组件桥接到ssd输入/输出(i/o)接口的电子装置。ssd控制器可以包括嵌入式处理器,该嵌入式处理器可以运行诸如固件的功能组件。ssd功能组件专用于装置,并且在大多数情况下可以被更新。

4、两种主要类型的闪速存储器组件以nand逻辑门和nor逻辑门命名。各个闪速存储器单元呈现与其相应栅极相似的内部特性。nand型闪速存储器可以以比整个存储器空间小得多的块(或页面)来写入和读取。nor型闪速存储器允许将单个机器字(字节)写入到已擦除位置或者单独地读取单个机器字(字节)。nand型闪速存储器主要以用于通用存储和数据传输的存储卡、usb闪存驱动器、固态驱动器和类似产品来操作。

5、基于nand闪存的存储装置因其更快的读取/写入性能、更低的功耗和防震特性而被广泛采用。然而,通常,它们比硬盘驱动器(hdd)更昂贵。为了降低成本,nand闪存制造商一直在将其制造工艺的极限推向20纳米甚至更低,这通常会导致使用寿命缩短和数据可靠性下降。因此,需要比传统的博斯-查德胡里-霍昆格姆(bose-chaudhuri-hocquenghem,bch)码更强大的错误校正码(ecc)来克服相关的噪声和干扰,从而提高数据完整性。ecc的一种这样的代码是低密度奇偶校验(ldpc)代码。各种算法可以用于解码ldpc码。

6、ldpc码和相关解码器具有不同的迭代解码算法,诸如位翻转(bf)解码算法、置信传播(bp)解码算法、和积(sp)解码算法、最小和(ms)解码算法、最小-最大解码算法等。一些算法可提供速度,而另一些算法则在更高的噪音水平下更具性能。在特定系统中可以使用多种解码算法,以根据诸如噪声水平和干扰的条件使用不同的解码器对不同的码字进行解码。

7、在该背景下,出现了本发明的实施例。

技术实现思路

1、本发明的方面包括一种用于操作ms解码器的方法。该方法确定ms解码器的操作模式。该方法针对每个变量节点,计算变量至校验节点v2c消息。该方法根据操作模式,将与所计算的v2c消息相关联的校验信息存储在校验节点单元cnu存储器中。校验信息包括当操作模式为高精度模式时的完整信息以及当操作模式为低精度模式时的部分信息。

2、本发明的其他方面包括一种存储器系统,包括:存储器装置、与存储器装置通信并被配置为控制存储器装置的控制器、以及与存储器装置的存储装置通信的最小和(ms)解码器。ms解码器被配置为:针对每个变量节点,计算变量至校验节点v2c消息;并且根据ms解码器的操作模式,将与所计算的v2c消息相关联的校验信息存储在校验节点单元cnu存储器中。校验信息包括当操作模式为高精度模式时的完整信息以及当操作模式为低精度模式时的部分信息。

3、本发明的其他方面包括方法,特别是操作包括解码器或与解码器相关联的存储器系统的方法。这种操作存储器系统的方法包括输入。

4、鉴于以下描述和附图,本发明的其他特征、方面和优点将变得清楚。

技术特征:1.一种操作ms解码器的方法,包括:

2.根据权利要求1所述的方法,其中对于每个校验和,所述完整信息包括min1值、min1索引、min2值、min2索引和校验和。

3.根据权利要求2所述的方法,其中

4.根据权利要求2所述的方法,其中对于所述完整信息,所述操作模式以4kb模式操作。

5.根据权利要求1所述的方法,其中对于每个校验和,所述部分信息包括min1值、min1索引、min2值和校验和。

6.根据权利要求5所述的方法,其中

7.根据权利要求5所述的方法,其中对于所述部分信息,所述操作模式以8kb或16kb模式操作。

8.根据权利要求1所述的方法,其中所述ms解码器中的所述校验节点单元cnu存储器作为ms ldpc解码器的一部分操作。

9.根据权利要求8所述的方法,其中ms ldpc解码的迭代继续进行,直到达到最大迭代次数或者直到ldpc码字被成功解码为止。

10.根据权利要求9所述的方法,其中与完全以所述高精度模式操作的解码器相比,所述ms解码器的门数减少。

11.一种存储器系统,包括:

12.根据权利要求11所述的系统,其中对于每个校验和,所述完整信息包括min1值、min1索引、min2值、min2索引和校验和。

13.根据权利要求12所述的系统,其中

14.根据权利要求12所述的系统,其中对于所述完整信息,所述操作模式以4kb模式操作。

15.根据权利要求11所述的系统,其中对于每个校验和,所述部分信息包括min1值、min1索引、min2值和校验和。

16.根据权利要求15所述的系统,其中

17.根据权利要求15所述的系统,其中,对于所述部分信息,所述操作模式以8kb或16kb模式操作。

18.根据权利要求11所述的系统,其中所述ms解码器中的所述校验节点单元cnu存储器作为ms ldpc解码器的一部分操作。

19.根据权利要求18所述的系统,其中ms ldpc解码的迭代继续进行,直到达到最大迭代次数或者直到ldpc码字被成功解码为止。

20.根据权利要求19所述的系统,其中与完全以所述高精度模式操作的解码器相比,所述ms解码器的门数减少。

技术总结一种操作MS解码器的方法和使用该MS解码器的相关联的存储器系统。该方法确定MS解码器的操作模式。该方法针对每个变量节点,计算变量至校验节点V2C消息。该方法根据操作模式,将与所计算的V2C消息相关联的校验信息存储在校验节点单元CNU存储器中。校验信息包括当操作模式为高精度模式时的完整信息以及当操作模式为低精度模式时的部分信息。技术研发人员:张帆,段宏伟,王浩博受保护的技术使用者:爱思开海力士有限公司技术研发日:技术公布日:2024/3/4本文地址:https://www.jishuxx.com/zhuanli/20240731/183603.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表