相变存储器控制方法及其操作系统、PCM控制器

- 国知局

- 2024-07-31 19:49:35

本发明属于存储器,更具体地,涉及一种相变存储器控制方法及其操作系统、pcm控制器。

背景技术:

1、相变存储器的低疲劳特性以及其高写入延迟是其在市场化应用中的两大挑战。

2、低疲劳特性指的是相变存储单元在写入一定次数(一般为10的9次)后由于疲劳无法再次进行读写。针对相变存储器的疲劳特性优化,khwa等在文献中提出一种原位自退火技术(in-situ-self-anneal,issa)。该技术揭示了相变存储单元的疲劳特性可以在其被写入10的4次左右进行修复,且揭示了相变存储单元在set/reset循环写入下reset状态阻值随写入次数的变化关系,因此,可以以10的4次循环后的reset状态阻值作为阻值预警点cap,在每次reset操作之后,对相变存储器单元reset状态阻值进行读取监测,如若相变存储器reset状态下的阻值低于设定的写入次数下的阻值预警点cap,说明写入次数已达退火要求,触发退火信号,对相变存储器单元施加退火脉冲,进行退火操作,从而实现对相变存储器疲劳特性的修复。由于该技术依靠reset操作之后的相变存储器件单元阻值作为退火触发条件,然而在实际应用中,相变存储器单元在reset之前可能会经历连续set或者reset操作,这将对reset阻值产生一定影响。例如set之后进行reset相较于reset之后进行的reset,其非晶化体积更小,阻值更低。故实际应用中reset之后的阻值未必能准确反映出相变存储器件单元循环次数,退火时机未必准确。

3、相变存储器的写入延迟高度依赖于数据:当进行reset操作时,需要施加短脉冲,但当进行set操作时,需要长脉冲。set操作的进行时间几乎是reset操作进行时间的8倍,因此,写延迟主要由set操作决定。而issa技术在每次reset之后均要进行一次读操作,且如若其阻值触发退火判定,还需对整个单元进行10μs级别的退火脉冲操作,这将产生极大时延,使本就不占优势的写延时更大。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本发明提供了一种相变存储器控制方法及其操作系统、pcm控制器,其目的在于准确判断退火时机且同时优化写数据的延时。

2、一种相变存储器控制方法,包括;

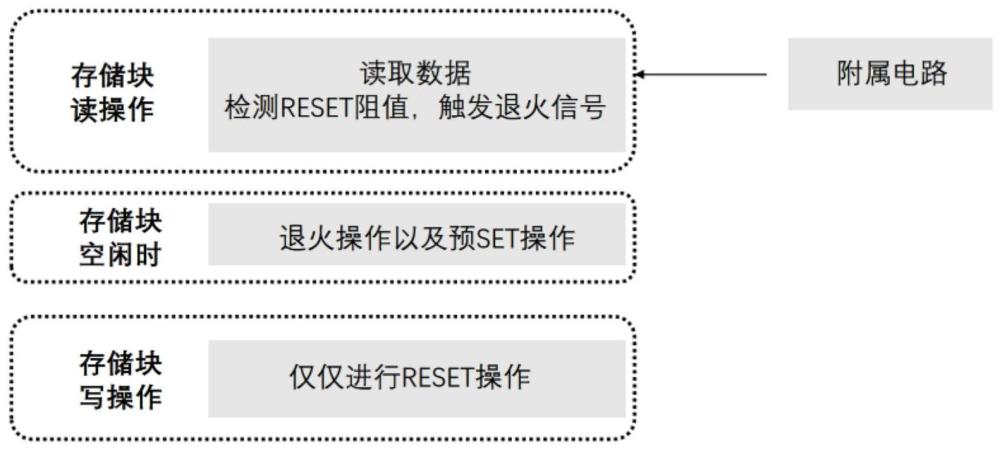

3、在存储块读操作期间,对其中相变存储单元进行读数据操作并对处于reset态且阻值低于退火阈值的相变存储单元触发对应的退火信号;

4、在存储块空闲期间,控制其中已触发退火信号的相变存储单元执行退火操作,对写指令中需要将reset态转换为set态的相变存储单元进行预set操作;

5、在存储块写操作期间,对写指令中需要将处于set态转换为reset态的相变存储单元进行reset操作;

6、其中,所述相变存储单元进行set操作后处于set态,所述相变存储单元进行reset操作后处于reset态,set态的阻值相较reset态的阻值低。

7、在其中一个实施例中,所述方法还包括:将所述存储块的空闲时段划分为两个时间窗口:

8、其中一个为退火窗口,所述退火窗口位于基于读指令将所述相变存储单元的数据存入末级缓存的时间t0至基于写指令使末级缓存发生第一次数据修改的时间t1之间的时段内,在所述退火窗口控制执行退火操作;

9、另一个为预写窗口,所述预写窗口位于基于写指令使末级缓存发生第一次数据修改的时间t1至数据从末级缓存全部逐出的时间tn之间的时段内,在所述预写窗口执行预set操作。

10、在其中一个实施例中,

11、在存储块读操作期间,将所读取的数据存入读队列并传输给末级缓存,以及将触发退火信号的相变存储单元的位置信息存入退火队列;

12、在存储块空闲期间,对所述退火队列所指向的所有相变存储单元进行退火;以及将需要进行预set操作的相变存储器的位置信息按时序存入预写队列并对所述预写队列所指向的所述相变存储单元进行set操作;

13、在存储块写操作期间,对所述写队列中所指向的所有相变存储单元进行reset操作,其中需要进行reset操作的相变存储单元的位置信息在末级缓存逐出数据时存入写队列。

14、在其中一个实施例中,在存储块空闲期间,对所述退火队列所指向的位于同一字线上的相变存储单元同时进行退火。

15、在其中一个实施例中,在存储块空闲期间,一旦所述预写队列中存入位置信息,则开始对所述预写队列所指向的所述相变存储单元按照存入顺序依次进行set操作。

16、在其中一个实施例中,在存储块写操作期间,对所述写队列中所指向的位于同一字线上的相变存储单元同时进行reset操作。

17、在其中一个实施例中,对所述相变存储单元进行set操作表示写入数据“1”,对所述相变存储单元进行reset操作表示写入数据“0”。

18、一种pcm控制器,所述pcm控制器用于执行上述的相变存储器控制方法。

19、一种相变存储器操作系统,包括cpu、缓存、pcm控制器,其中,

20、所述cpu用于向所述pcm控制器发送控制存储块读取和写入的读指令和写指令,所述读指令包含相变存储单元的位置信息,所述写指令包含相变存储单元的位置信息以及写入数据;

21、所述缓存用于实现所述cpu和所述pcm控制器之间的数据和位置信息交互;

22、所述pcm控制器用于执行上述的相变存储器控制方法。

23、在其中一个实施例中,还包括多功能电路,所述pcm控制器用于通过所述多功能电路对相变存储单元进行读数据操作并对处于reset态且阻值低于退火阈值的相变存储单元触发对应的退火信号;

24、所述多功能电路包括预置电路、电流镜电路、预置电阻r1、第一迟滞比较器、第二迟滞比较器和异或门,其中,

25、所述预置电路用于向相变存储单元提供稳定电压,以产生流经所述相变存储单元的电流ipcm;

26、所述电流镜电路用于将电流ipcm镜像到预置电阻r1,以使所述预置电阻r1产生电压vr;

27、所述第一迟滞比较器用于比较电压vr与读预置电压vreadref并输出结果out,当vr<vreadref,结果out为低电平,当vr>vreadref,结果out为高电平;电压vannealref为相变存储单元reset态阻值达到退火阈值时预置电阻r1上的电压,其低于相变存储单元处于正常reset态时预置电阻r1上的电压;

28、所述第二迟滞比较器用于比较电压vr与退火预置电压vannealref并输出结果vh2,当vr<vannealref,结果vh2为低电平,否则,输出高电平;

29、所述异或门用于对结果out和结果vh2做逻辑运算,输出异或结果anneal_out;

30、以结果out的电平高低作为相变存储单元存储的不同数据;以结果anneal_out为高电平时表示触发退火信号。

31、总体而言,通过本发明所构思的以上技术方案与现有技术相比,能够取得下列有益效果:

32、(1)本发明在读操作的同时对相变存储器reset态的阻值进行判断,对处于reset态且阻值低于退火阈值的相变存储单元触发对应的退火信号,相比于在执行写操作之后施加单独的相变存储器阻值判断操作,降低了退火判断操作带来的时延,提高了相变存储器的操作效率。

33、(2)本发明通过在存储块空闲时间对相变存储器执行退火操作,消除了退火操作对相变存储器读写延时影响,提高了相变存储器的读写速度。

34、(3)本发明写操作分为预set操作和reset操作,预set操作负责将reset态转换为set态,reset操作负责将set态转换为reset态,不会出现重复进行reset操作或重复进行set操作的情况,对相变存储器执行set-reset的准确循环,因此,相变存储器reset态下的阻值能更好地反映相变存储单元的疲劳程度,从而使退火操作时机更加准确,提高退火操作对相变存储器疲劳特性修复的成功率。

35、(4)本发明在存储块空闲时间对相变存储器进行预set操作,在写操作期间只要执行reset操作,相比于将set操作和reset操作均设置于写操作期间,可以大大降低写操作的延时。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184204.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。