存算一体电路、芯片及电子设备

- 国知局

- 2024-07-31 19:57:40

本申请涉及半导体,尤其涉及一种存算一体电路、芯片及电子设备。

背景技术:

1、随着处理器和存储器的工艺提升差的变大,冯诺依曼体系结构下存储墙剪刀差不断增大,访存功耗墙问题也日益突出,工业界和学术界开始从聚焦计算转到聚焦存储。与此同时,目前各种机器学习算法的逐步成熟与落地,越来越多的基于人工神经网络的算法部署在各种场景执行智能分辨或智能识别等任务,计算量的飞速增加,存储器中的数据搬运慢、搬运能耗大等问题成为了计算效率的关键瓶颈之一。

技术实现思路

1、本发明提供了一种存算一体电路、芯片及电子设备,以解决或者部分解决存储器因为存储墙和功耗墙导致的数据搬运能耗大的技术问题。

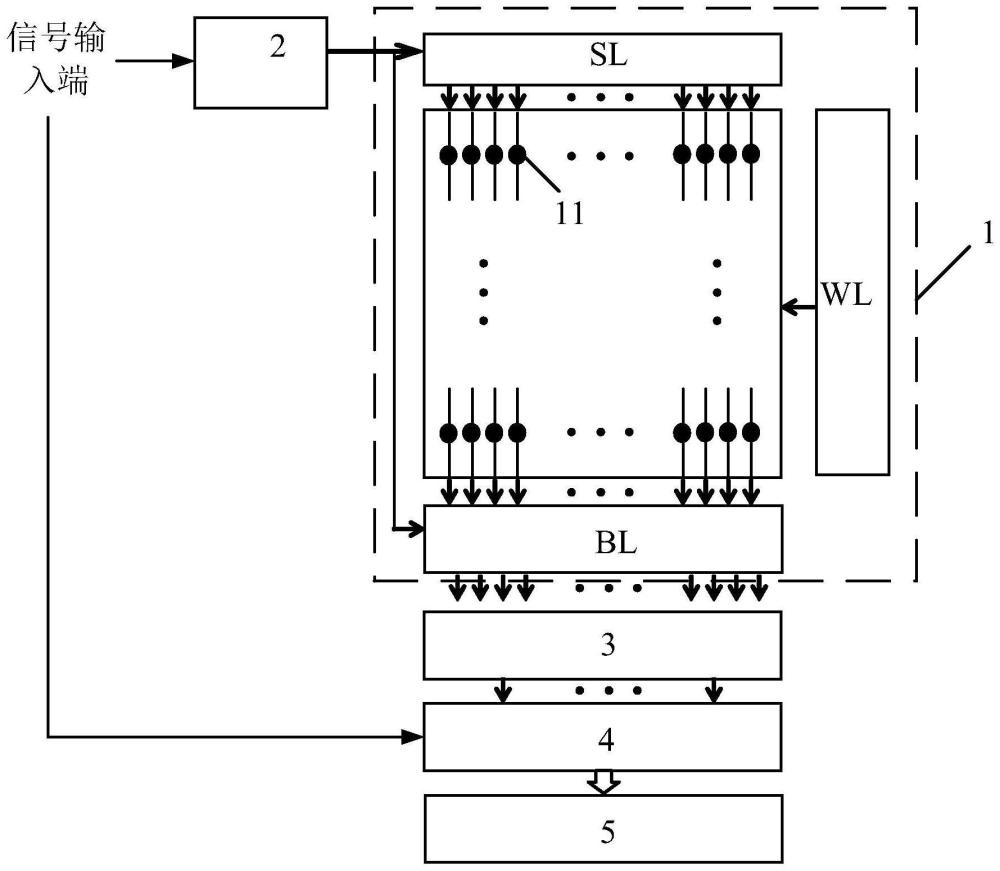

2、第一方面,根据本发明实施例提供了一种存算一体电路,包括阻变存储器阵列、钳位电路、电流镜和模数转换电路;

3、所述钳位电路连接在信号输入端和所述阻变存储器阵列之间,用于对所述阻变存储器阵列中的n个选定阻变存储器输入钳位电压信号,n≥2且为整数;

4、所述电流镜连接在所述阻变存储器阵列和所述模数转换电路之间,用于基于所述n个选定阻变存储器输出的n路电流,输出汇合电流至所述模数转换电路;

5、所述模数转换电路用于将所述汇合电流转换为数字信号。

6、可选的,所述阻变存储器阵列包括源线、字线、位线和多个存储单元,一个所述存储单元包括一个第一晶体管和一个阻变存储器;

7、所述第一晶体管的源极连接所述源线,栅极连接所述字线;

8、所述阻变存储器连接在所述第一晶体管的漏极和所述钳位电路之间。

9、可选的,所述钳位电路的数量与所述存储单元的数量相等;一个所述钳位电路连接在所述信号输入端和一个所述存储单元之间;

10、所述钳位电路包括运算放大器和第二晶体管;所述运算放大器的正相输入端连接所述信号输入端,反向输入端连接所述位线,输出端连接所述第二晶体管的栅极;所述第二晶体管的源极连接所述位线,漏极连接所述电流镜。

11、可选的,所述模数转换电路为电流型逐次逼近模数转换电路。

12、可选的,所述电流型逐次逼近模数转换电路包括:第三晶体管、第四晶体管、第一反相器、第二反相器和第三反相器;

13、所述第三晶体管的漏极连接参考电流阵列,源极连接所述第四晶体管的源极,栅极连接所述第四晶体管的栅极;所述第四晶体管的漏极连接所述电流镜;

14、所述第一反相器的输出端和所述第二反相器的输入端与所述第四晶体管的漏极相连;所述第一反相器的输入端和所述第二反相器的输出端与所述第三反相器的输入端相连。

15、可选的,所述第一反相器包括第一上拉晶体管和第一下拉晶体管,所述第二反相器包括第二上拉晶体管和第二下拉晶体管,所述第三反相器包括第三上拉晶体管和第三下拉晶体管;

16、所述第一上拉晶体管的漏极、所述第二上拉晶体管的源极和所述第三上拉晶体管的源极连接电源端;所述第一下拉晶体管的漏极、所述第二下拉晶体管的源极和所述第三下拉晶体管的源极接地;

17、所述第一上拉晶体管的源极连接所述第一下拉晶体管的源极,所述第一上拉晶体管的栅极连接所述第一下拉晶体管的栅极;

18、所述第二上拉晶体管的栅极连接所述第二下拉晶体管的栅极,所述第二上拉晶体管的漏极连接所述第二下拉晶体管的漏极;

19、所述第三上拉晶体管的栅极连接所述第三下拉晶体管的栅极,所述第三上拉晶体管的漏极连接所述第三下拉晶体管的漏极。

20、可选的,存算一体电路还包括数字组合电路,所述数字组合电路的输入端连接所述第三反相器的输出端,用于将所述数字信号转换为目标编码。

21、可选的,存算一体电路还包括地址译码器,所述地址译码器连接在所述信号输入端和所述阻变存储器阵列之间。

22、第二方面,根据本发明实施例提供了一种存算一体芯片,包括第一方面提供的任一项存算一体电路。

23、第三方面,根据本发明实施例提供了一种电子设备,包括第一方面提供的存算一体芯片。

24、通过本发明的一个或者多个技术方案,本发明具有以下有益效果或者优点:

25、本发明提供了一种存算一体电路,一方面,利用阻变存储器(rram)阵列可以实现基础的数据读写操作;另一方面,通过钳位电路可以将不同的读出电压钳位在阻变存储器两端,结合阻变存储器阵列中被选定的n个阻变存储器的阻态高低,输出n路电流信号;n路电流经电流镜的赋值处理后输出汇合电流或整合电流,汇合电流再经模数转换电路转换为数字信号,实现了输入数据与n个选定的阻变存储器的对应数据的乘法运算;该存算一体电路利用阻变存储器阵列适合电流型计算的特点,在数据读出的时候进行计算,通过存算一体设计将计算和存储功能一体化,可在数据读出的时候进行计算,避免了传统数字电路乘法器计算时的较大翻转功耗;同时,通过钳位电路对输入信号进行钳位,钳位电压通过阻变存储器阵列转为电流信号,输出的电流经电流镜和模数转换电路读出数字信号,因此在做计算时仅有一次电压到电流的转换,不需要再将电流信号额外转换成电压信号读出,减少了电流-电压转换产生的额外电路开销,从而提高了运算速率,降低了电路和系统的运算功耗。

26、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:1.一种存算一体电路,其特征在于,包括阻变存储器阵列、钳位电路、电流镜和模数转换电路;

2.如权利要求1所述的存算一体电路,其特征在于,所述阻变存储器阵列包括源线、字线、位线和多个存储单元,一个所述存储单元包括一个第一晶体管和一个阻变存储器;

3.如权利要求2所述的存算一体电路,其特征在于,所述钳位电路的数量与所述存储单元的数量相等;一个所述钳位电路连接在所述信号输入端和一个所述存储单元之间;

4.如权利要求1所述的存算一体电路,其特征在于,所述模数转换电路为电流型逐次逼近模数转换电路。

5.如权利要求4所述的存算一体电路,其特征在于,所述电流型逐次逼近模数转换电路包括:第三晶体管、第四晶体管、第一反相器、第二反相器和第三反相器;

6.如权利要求5所述的存算一体电路,其特征在于,所述第一反相器包括第一上拉晶体管和第一下拉晶体管,所述第二反相器包括第二上拉晶体管和第二下拉晶体管,所述第三反相器包括第三上拉晶体管和第三下拉晶体管;

7.如权利要求5所述的存算一体电路,其特征在于,还包括数字组合电路,所述数字组合电路的输入端连接所述第三反相器的输出端,用于将所述数字信号转换为目标编码。

8.如权利要求1所述的存算一体电路,其特征在于,还包括地址译码器,所述地址译码器连接在所述信号输入端和所述阻变存储器阵列之间。

9.一种存算一体芯片,其特征在于,包括如权利要求1至8中任一项所述的存算一体电路。

10.一种电子设备,其特征在于,包括如权利要求9所述的存算一体芯片。

技术总结本发明公开了一种存算一体电路、芯片及电子设备,其中的存算一体电路包括:包括阻变存储器阵列、钳位电路、电流镜和模数转换电路;所述钳位电路连接在信号输入端和所述阻变存储器阵列之间,用于对所述阻变存储器阵列中的N个选定阻变存储器输入钳位电压信号,N≥2且为整数;所述电流镜连接在所述阻变存储器阵列和所述模数转换电路之间,用于基于所述N个选定阻变存储器输出的N路电流,输出汇合电流至所述模数转换电路;所述模数转换电路用于将所述汇合电流转换为数字信号。该存算一体电路可在数据读出的时候进行计算,且能够提高运算速率,降低了电路和系统的运算功耗。技术研发人员:张锋,吴昊受保护的技术使用者:中国科学院微电子研究所技术研发日:技术公布日:2024/5/27本文地址:https://www.jishuxx.com/zhuanli/20240731/184768.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表