EFUSE存储单元、烧写读取电路及电子设备的制作方法

- 国知局

- 2024-07-31 20:14:25

本技术涉及集成电路,特别涉及一种efuse存储单元、烧写读取电路及电子设备。

背景技术:

1、efuse的全称是“电子熔断器”(electronic fuse),是一种可编程电子保险丝,是一种用于存储信息和保护芯片的非易失性存储器件。efuse相对于fuse(熔丝)和激光熔丝等其他一次性编程(one time program,otp)的存储器而言,具有不需要额外的设备辅助熔断、工艺兼容性好、占用面积小等优点,因此得到了广泛的应用。

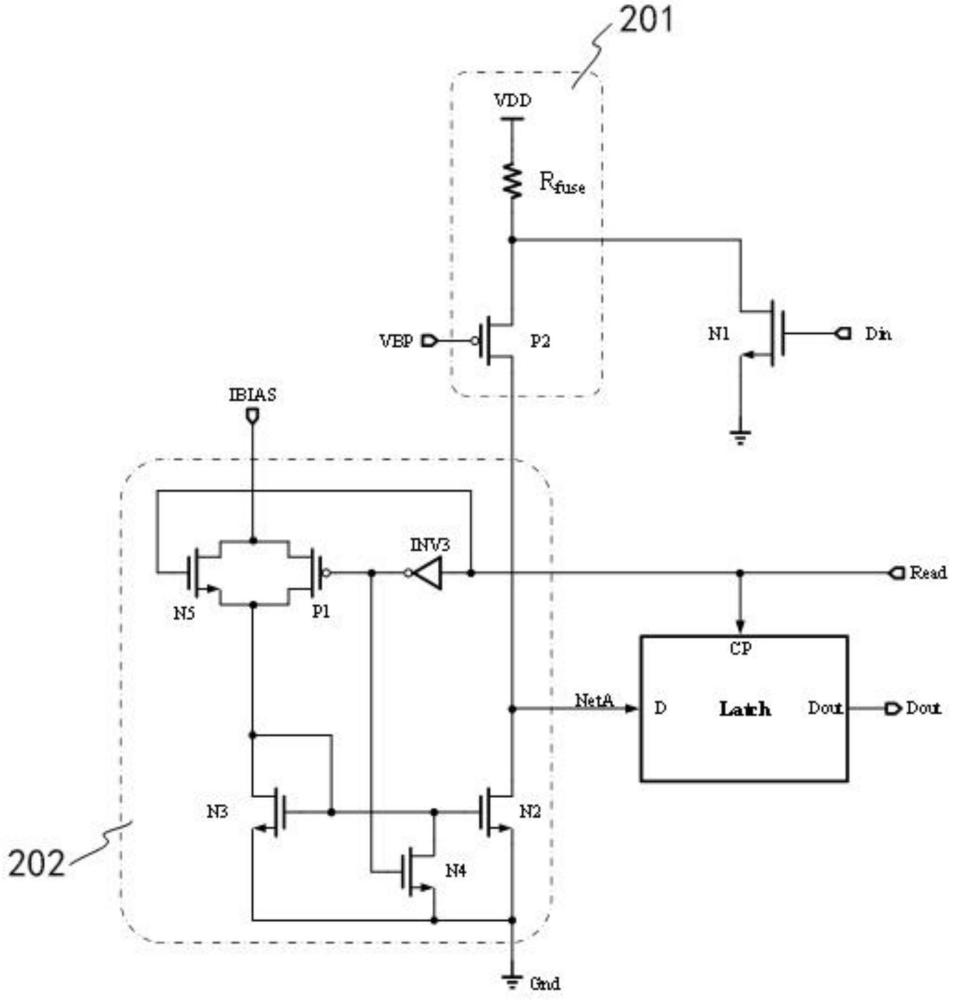

2、传统的efuse存储单元如图1所示,rfuse是电子熔断器,一般由一段很细的多晶硅构成,在烧录之前,其阻值较小,例如几十欧姆。第一nmos管n1是一个宽长比较大的nmos管,它的栅极被烧录信号din所控制,当din=1时n1导通,此时将会有较大的电流通过rfuse和n1流到gnd(地),这个大电流在熔丝上产生的热量,在理想状况下将会导致熔丝完全被烧断,从而呈现开路,rfuse的等效电阻接近无穷大。

3、第二nmos管n2的栅极接到一个偏置电压vbias上,第二nmos管n2相当于一个恒流源,设其电流值为i;第三nmos管n3、第一pmos管p1和反相器inv3组成一个传输门,反相器inv3的输入端以及第三nmos管n3的栅极接到读取控制信号read。当read=1时,此传输门导通。对于没有经过烧录的efuse存储单元,rfuse阻值很小,neta节点的电压等于vdd-i×rfuse,这是一个非常接近vdd的值,所以neta节点表现为逻辑1;而对于经受过烧录的eufse存储单元,理想状况下rfuse是完全熔断并呈现为开路的,所以neta节点的电压将等于gnd,即表现为逻辑0。

4、图1中的latch是一个锁存器,其电路如图2所示,它的采样时钟信号cp接到了读取控制信号read上,当read=1时,锁存器对neta节点的逻辑状态进行采样,当read=0时,neta节点的逻辑状态被锁存下来并从其dout端口输出。

5、但是由于某些非理想情况的存在,会出现rfuse在烧录后并没有完全熔断,而是会呈现为一个较大的电阻,比如几千欧姆到几十千欧姆,此时即使再次进行烧录,由于此时rfuse电阻较大,流过它的电流太小,产生的热量不足以将它完全熔断。在这种情况下,当读取控制信号read=1,由第三nmos管n3、第一pmos管p1和反相器inv3组成的传输门导通时,由于rfuse并没有被完全熔断,而是等效为一个阻值为几千欧姆到几十千欧姆的电阻,如果恒流源的电流i比较小,则neta节点的电压将等于vdd-i×rfuse,这是一个处于vdd和gnd之间的一个电压,极端情况下甚至有可能处于vdd和gnd的中间值附近,这将导致后续的latch锁存器电路无法判断neta节点的逻辑状态是0还是1,导致读取错误。

6、一般采用增大恒流源的电流i的方式,使i×rfuse的值大于vdd,从而让neta节点的电压等于gnd(即表现为逻辑0),所以为了能读出正确的值,必须设置一个较大的恒流源电流i,这将导致读取时功耗较大。

7、需要说明的是,公开于该实用新型背景技术部分的信息仅仅旨在加深对本实用新型一般背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

技术实现思路

1、本实用新型的目的在于提供一种efuse存储单元、烧写读取电路及电子设备,以解决存在rfuse未完全熔断导致latch锁存器无法准确判断neta节点的状态,即无法判断电路状况或者说rfuse的状况的问题。

2、为解决上述技术问题,本实用新型提供一种efuse存储单元,包括:

3、恒流源模块,用于连接烧录控制信号端口和偏置电压信号端口,并在烧录前提供大于预设值的第一电流,在烧录后提供小于所述预设值的第二电流,所述恒流源模块包括电子熔断器;

4、latch电路模块,所述latch电路模块的锁存数据输入端口与第一节点相连、采样时钟端口与读出控制信号相连;

5、数控电流镜模块,包括反相器、传输门和电流镜,所述反相器的输入端与所述读出控制信号相连,所述反相器的输入端和输出端分别接入所述传输门的第一控制输入端和第二控制输入端相连,所述传输门的信号输入端与偏置电流输入端口相连,所述偏置电流输入端口用于提供具有所述预设值的偏置电流信号,所述传输门的信号输出端与所述电流镜的基准电流输入端相连,所述电流镜的复制电流输入端与所述第一节点相连,所述第一节点还与所述电子熔断器的第二端相连,其中,所述电流镜中的栅极互连节点还与第四开关晶体管的漏极相连,所述第四开关晶体管的栅极与所述反相器的输出端相连,所述第四开关晶体管的源极与所述电流镜的基准电流输出端及复制电流输出端共接至地。

6、优选地,所述恒流源模块还包括第二控制晶体管,所述电子熔断器的第一端接电源电压、第二端与所述第二控制晶体管的源极相连,所述第二控制晶体管的漏极与所述第一节点相连、栅极与所述偏置电压信号端口相连,所述烧录控制信号端口与第一开关晶体管的栅极相连,所述第一开关晶体管的漏极与所述电子熔断器的第二端相连,所述第一开关晶体管的源极接地。

7、优选地,所述传输门包括第五开关晶体管和第一控制晶体管,所述第五开关晶体管和所述第一控制晶体管的漏极互连作为所述信号输入端,以与所述偏置电流输入端口相连,所述第五开关晶体管的栅极作为所述第一控制输入端,以与所述反相器的输入端相连;所述第五开关晶体管和所述第一控制晶体管的源极互连作为所述信号输出端,以与所述电流镜的基准电流输入端相连,所述第一控制晶体管的栅极作为所述第二控制输入端,以与所述反相器的输出端相连。

8、优选地,所述电流镜包括第三开关晶体管和第二开关晶体管,所述第三开关晶体管和所述第二开关晶体管的栅极互连并作为所述栅极互连节点,所述第三开关晶体管的漏极和栅极互连作为所述基准电流输入端,所述第二开关晶体管的漏极作为所述复制电流输入端,以与所述第一节点相连,所述第二开关晶体管和所述第三开关晶体管的源极分别为复制电流输出端和基准电流输出端。

9、本技术还提供了一种efuse烧写读取电路,包括:

10、公共偏置单元,用于向偏置电流输入端口提供偏置电流信号,以及向偏置电压信号端口提供偏置电压信号;

11、至少一efuse存储单元,所述efuse存储单元包括:

12、恒流源模块,用于连接烧录控制信号端口和偏置电压信号端口,并在烧录前提供大于预设值的第一电流,在烧录后提供小于所述预设值的第二电流,所述恒流源模块包括电子熔断器;

13、latch电路模块,所述latch电路模块的锁存数据输入端口与第一节点相连、采样时钟端口与读出控制信号相连;

14、数控电流镜模块,包括反相器、传输门和电流镜,所述反相器的输入端与所述读出控制信号相连,所述反相器的输入端和输出端分别接入所述传输门的第一控制输入端和第二控制输入端相连,所述传输门的信号输入端与偏置电流输入端口相连,所述偏置电流输入端口用于提供具有所述预设值的偏置电流信号,所述传输门的信号输出端与所述电流镜的基准电流输入端相连,所述电流镜的复制电流输入端与所述第一节点相连,所述第一节点还与所述电子熔断器的第二端相连,其中,所述电流镜中的栅极互连节点还与第四开关晶体管的漏极相连,所述第四开关晶体管的栅极与所述反相器的输出端相连,所述第四开关晶体管的源极与所述电流镜的基准电流输出端及复制电流输出端共接至地。

15、优选地,所述公共偏置单元包括第一电阻、第二电阻、第三控制晶体管和第四控制晶体管,所述第一电阻的第一端和第二电阻的第一端共接,并接至电源电压,所述第三控制晶体管的源极与所述第一电阻的第二端相连,所述第三控制晶体管的栅极与漏极共接,用于接入外部偏置电流信号,所述第四控制晶体管的源极与所述第二电阻的第二端相连,所述第三控制晶体管和第四控制晶体管的栅极共接,并连接所述偏置电压信号端口以提供偏置电压信号,所述第四控制晶体管的漏极用于向所述偏置电流输入端口输出所述偏置电流信号。

16、优选地,所述恒流源模块还包括第二控制晶体管,所述电子熔断器的第一端接电源电压、第二端与所述第二控制晶体管的源极相连,所述第二控制晶体管的漏极与所述第一节点相连、栅极与所述偏置电压信号端口相连,所述烧录控制信号端口与第一开关晶体管的栅极相连,所述第一开关晶体管的漏极与所述电子熔断器的第二端相连,所述第一开关晶体管的源极接地。

17、优选地,所述传输门包括第五开关晶体管和第一控制晶体管,所述第五开关晶体管和所述第一控制晶体管的漏极互连作为所述信号输入端,以与所述偏置电流输入端口相连,所述第五开关晶体管的栅极作为所述第一控制输入端,以与所述反相器的输入端相连;所述第五开关晶体管和所述第一控制晶体管的源极互连作为所述信号输出端,以与所述电流镜的基准电流输入端相连,所述第一控制晶体管的栅极作为所述第二控制输入端,以与所述反相器的输出端相连。

18、优选地,所述电流镜包括第三开关晶体管和第二开关晶体管,所述第三开关晶体管和所述第二开关晶体管的栅极互连并作为所述栅极互连节点,所述第三开关晶体管的漏极和栅极互连作为所述基准电流输入端,所述第二开关晶体管的漏极作为所述复制电流输入端,以与所述第一节点相连,所述第二开关晶体管和所述第三开关晶体管的源极分别为复制电流输出端和基准电流输出端。

19、本公开还提供了一种电子设备,采用上述的efuse烧写读取电路,对efuse存储单元进行烧录和读取。

20、本公开还提供了一种efuse烧写读取电路的烧写读取方法,采用上述的efuse烧写读取电路,对efuse存储单元进行烧录和读取,还包括以下步骤:

21、当进行烧录时:向所述efuse存储单元提供读出控制信号,且所述读出控制信号处于第一电平时,依次对所述efuse存储单元进行烧录,并通过所述latch电路模块的锁存数据输出端口的电平信号判断所述efuse存储单元的烧录状态;

22、当进行读取时:向所述efuse存储单元提供读出控制信号,且所述读出控制信号处于第二电平时,依次对所述efuse存储单元进行读取。

23、在本实用新型提供的efuse存储单元中,当读出控制信号read由1跳变到0时,第一节点neta的逻辑状态被latch电路模块锁存下来,并输出到其锁存数据输出端口dout,若锁存数据输出端口dout为逻辑1,则表示此efuse存储单元未被烧录,锁存数据输出端口dout为逻辑0,则表示此efuse存储单元已被烧录,从而避免电子熔断器rfuse未被完全烧录造成读取错误的问题。进一步的,预设值的大小并不影响第一节点neta的输出结果,因此可将偏置电流信号i设置成一较小的值,能够大大降低读取过程中的功耗。

24、本实用新型提供的efuse烧写读取电路及电子设备与本实用新型提供的efuse存储单元属于同一实用新型构思,因此,本实用新型提供的efuse烧写读取电路及电子设备至少具有本实用新型提供的efuse存储单元的所有优点,在此不再赘述。公共偏置单元用于向偏置电流输入端口提供偏置电流信号,以及向偏置电压信号端口提供偏置电压信号;至少一efuse存储单元,所述efuse存储单元包括:恒流源模块,用于连接烧录控制信号端口和偏置电压信号端口,并在烧录前提供大于预设值的第一电流,在烧录后提供小于所述预设值的第二电流,所述恒流源模块包括电子熔断器;latch电路模块,所述latch电路模块的锁存数据输入端口与第一节点相连、采样时钟端口与读出控制信号相连;数控电流镜模块,包括反相器、传输门和电流镜,所述反相器的输入端与所述读出控制信号相连,所述反相器的输入端和输出端分别接入所述传输门的第一控制输入端和第二控制输入端相连,所述传输门的信号输入端与偏置电流输入端口相连,所述偏置电流输入端口用于提供具有所述预设值的偏置电流信号,所述传输门的信号输出端与所述电流镜的基准电流输入端相连,所述电流镜的复制电流输入端与所述第一节点相连,所述第一节点还与所述电子熔断器的第二端相连,其中,所述电流镜中的栅极互连节点还与第四开关晶体管的漏极相连,所述第四开关晶体管的栅极与所述反相器的输出端相连,所述第四开关晶体管的源极与所述电流镜的基准电流输出端及复制电流输出端共接至地。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185512.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表