一种适用于多类型延迟线结构的ONFIPHY训练方法与流程

- 国知局

- 2024-09-05 14:36:39

本发明涉及存储器数据读写领域,更具体的,涉及一种适用于多类型延迟线结构的onfi phy训练方法。

背景技术:

1、对于遵循onfi协议的存储器件,访问flash的设备在执行读写操作时,dq(数据)和dqs(数据选取脉冲)需要满足采样的setup、hold时序,phy内部会使用一种延时调节电路(delayline)来实现调节读写两个方向不同dq bit和dqs相位关系,从而满足数据采样时序需求。

2、受工作频点、温度、电压、实现工艺、io质量和delayline设计等因素的影响,不同条件下phy_dq和phy_dqs通过数据通路到达数据采样电路flash的时间存在差异和变化,无法提供一个满足所有场景的delayline预设值。因此,实际上需要通过训练(training)调节delayline配置与调整dq dqs相位,确保写方向flash和读方向phy可以正确的采样数据。

3、由于工作速率提升、io质量、芯片工艺、封装设计与制造、以及芯片运行过程中的温度电压变化等因素,对时序的影响变得愈发明显。并且onfi协议dq是并口出数据,dq bit之间的skew对采样窗口也造成了影响。这些因素给系统的正常工作带来了挑战。在这种情况下,现有训练方案存在一系列问题,第一,缺乏灵活性,现有技术在寻找最大最小值时初始值需要额外操作进行提前设定。如果实际配置和理论相差较大,则初始值有可能无法正确采样。会导致训练失败。第二,采样窗口小,应对pvt变化能力降低。onfi协议dq信号是8bit并口数据,由于走线、io质量、工艺等原因,dq路径无法做到完全齐平,dq之间存在skew。单段式delayline和训练方案没有考虑dq skew因素,这会损失部分采样窗口,降低抵抗pvt变化的能力。第三,当温度变化,电压和工艺变化时,不同dq bit的采样会变化,当dq采样窗口重叠部分减小时容易漂移,当窗口完全消失时需要重复训练,从而降低了可用性。

技术实现思路

1、本发明克服了现有技术的缺陷,提出了一种适用于多类型延迟线结构的onfi phy训练方法。

2、本发明第一方面提供了一种适用于多类型延迟线结构的onfi phy训练方法,包括:

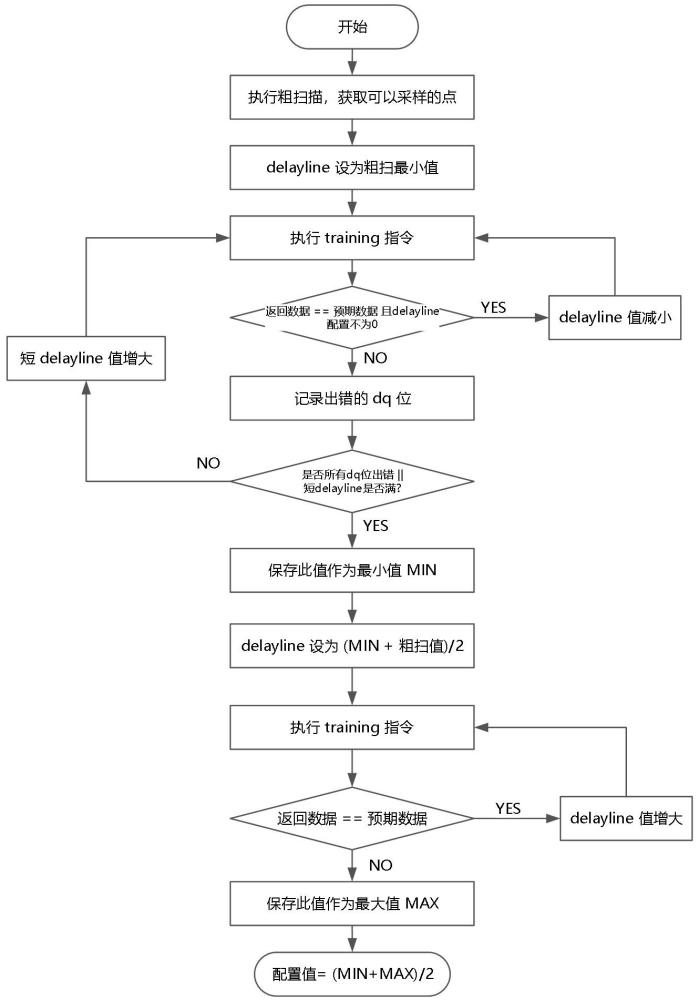

3、s1:粗扫描获取可采样值,在长delayline上使用固定步进扫描获取粗采样窗口,取粗扫描窗口得到的配置作为后续流程的配置参考;

4、s2:训练得到长delayline配置中的最小值并对齐dq;

5、步骤a1:短delayline全部配置为0,长delayline使用粗扫窗口最小值作为初始点;

6、步骤a2:执行预设训练指令比对数据,如果数据正确,长delayline减小预设单位并重复步骤2;如果数据出错且长delayline配置不为0则退出步骤a2,进行下一流程,此时表示delayline已经到达临界位置;如果delayline配置为0则退出步骤a2,表示长delayline已经最小;

7、步骤a3:记录出错的dq bit位;如果所有dq bit位出错,表示dq已经对齐,skew降到最低并退出步骤3;如果短delayline有一组已经达到最大值,表示某个dq对应短delayline调节能力已经用完短delayline已满,无法继续降低dq skew,此时退出步骤3;否则出错的dq对应的短delayline增大预设单位,回到步骤a2;

8、步骤a4:冻结此时的短delayline配置,表示dq已对齐,记录此时的长delayline为min,表示采样窗口下限;

9、s3:取流程二得到的min和粗扫窗口中心值的平均值作为流程s4的初始点;

10、s4:训练得到长delayline配置最大值;

11、步骤b1:执行训练指令对比数据,数据正确则增大预设单位长delayline配置值,并循环执行训练指令对比数据,直至数据出错,进入步骤b2;

12、步骤b2:记录此时的长delayline为max,表示采样窗口上限;

13、s5:取流程s2得到的min和流程s4得到的max的平均值作为最终训练结果值,标记为最终配置值。

14、本发明第二方面还提供了一种适用于多类型延迟线结构的onfi phy训练系统,该系统包括:存储器、处理器,所述存储器中包括适用于多类型延迟线结构的onfi phy训练程序,所述适用于多类型延迟线结构的onfi phy训练程序被所述处理器执行时实现如下步骤:

15、s1:粗扫描获取可采样值,在长delayline上使用固定步进扫描获取粗采样窗口,取粗扫描窗口得到的配置作为后续流程的配置参考;

16、s2:训练得到长delayline配置中的最小值并对齐dq;

17、步骤a1:短delayline全部配置为0,长delayline使用粗扫窗口最小值作为初始点;

18、步骤a2:执行预设训练指令比对数据,如果数据正确,长delayline减小预设单位并重复步骤2;如果数据出错且长delayline配置不为0则退出步骤a2,进行下一流程,此时表示delayline已经到达临界位置;如果delayline配置为0则退出步骤a2,表示长delayline已经最小;

19、步骤a3:记录出错的dq bit位;如果所有dq bit位出错,表示dq已经对齐,skew降到最低并退出步骤3;如果短delayline有一组已经达到最大值,表示某个dq对应短delayline调节能力已经用完短delayline已满,无法继续降低dq skew,此时退出步骤3;否则出错的dq对应的短delayline增大预设单位,回到步骤a2;

20、步骤a4:冻结此时的短delayline配置,表示dq已对齐,记录此时的长delayline为min,表示采样窗口下限;

21、s3:取流程二得到的min和粗扫窗口中心值的平均值作为流程s4的初始点;

22、s4:训练得到长delayline配置最大值;

23、步骤b1:执行训练指令对比数据,数据正确则增大预设单位长delayline配置值,并循环执行训练指令对比数据,直至数据出错,进入步骤b2;

24、步骤b2:记录此时的长delayline为max,表示采样窗口上限;

25、s5:取流程s2得到的min和流程s4得到的max的平均值作为最终训练结果值,标记为最终配置值。

26、本发明第三方面还提供一种计算机可读存储介质,所述计算机可读存储介质中包括适用于多类型延迟线结构的onfi phy训练程序,所述适用于多类型延迟线结构的onfiphy训练程序被处理器执行时,实现如上述任一项所述的适用于多类型延迟线结构的onfiphy训练方法的步骤。

27、本发明公开了一种适用于多类型延迟线结构的onfi phy训练方法。本流程首先通过粗扫描确定可采样值的范围,利用长delayline固定步进获取粗采样窗口作为后续参考。随后,通过训练找到长delayline的最小值并对齐dq。过程中,使用短delayline调整dqskew,直至dq对齐或短delayline调节能力用尽。接着,将粗扫窗口中心值与最小值的平均值作为初始点,训练长delayline的最大值。最后,取最小值和最大值的平均值作为最终配置值,完成整个训练流程。通过本发明,能够同时执行寻找采样窗口和对齐dq的动作,增大数据窗口,提升训练的效果与效率。

本文地址:https://www.jishuxx.com/zhuanli/20240905/287281.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。