器件制备方法和半导体器件与流程

- 国知局

- 2024-09-14 14:23:42

本公开涉及半导体,更具体地,涉及一种器件制备方法和半导体器件。

背景技术:

1、随着半导体技术的发展,已经可以制备出多种多样的器件用于各种应用。在一些半导体器件中,可能需要制备具有可控微结构的半导体层,以改善器件的性能。例如,在半导体光电器件中,可以通过制备具有特定微结构的半导体材料层来改善光吸收效果。然而,目前制备这种具有特定微结构的半导体层的工艺还存在很多不可控的因素,导致例如对材料的刻蚀深度过深、所产生的微结构的密度过低等问题。此外,现有工艺的流程复杂,导致了器件成本的增加。因此,存在对器件制备过程进行改进的需求。

技术实现思路

1、本公开的目的之一在于提供一种器件制备方法和半导体器件,以通过分子自组装的方式形成具有特定微结构的半导体器件,从而改善器件性能和降低器件制备成本。

2、根据本公开的第一方面,提供了一种器件制备方法,包括:

3、提供待处理组件,其中,所述待处理组件包括功能材料层;

4、在所述待处理组件上方沉积共聚物材料层,其中,所述共聚物材料层包括第一聚合物和第二聚合物;

5、基于第一聚合物和第二聚合物的微相分离形成图案化的第一聚合物层;以及

6、至少以所述图案化的第一聚合物层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部。

7、在一些实施例中,所述共聚物材料层由嵌段共聚物材料形成。

8、在一些实施例中,第一聚合物包括聚苯乙烯ps;以及

9、第二聚合物包括聚甲基丙烯酸甲酯pmma、聚(2-乙烯基吡啶)p2vp、聚甲基乙撑碳酸酯ppc和聚丙烯酸paa中的至少一者。

10、在一些实施例中,基于第一聚合物和第二聚合物的微相分离形成图案化的第一聚合物层包括:

11、通过常规热退火法、快速热退火法、激光退火法和溶液退火法中的至少一者使第一聚合物和第二聚合物彼此微相分离;和

12、至少去除第二聚合物,以形成图案化的第一聚合物层。

13、在一些实施例中,通过常规热退火法使第一聚合物和第二聚合物彼此微相分离包括:

14、在210~220℃、220~230℃或230~250℃的退火温度下对第一聚合物和第二聚合物进行热退火50~60min或60~70min,以使第一聚合物和第二聚合物彼此微相分离。

15、在一些实施例中,至少去除第二聚合物,以形成图案化的第一聚合物层包括:

16、利用氧等离子体对微相分离后的共聚物材料层进行干法刻蚀,以去除第一聚合物的一部分和第二聚合物,使第一聚合物的剩余部分形成为图案化的第一聚合物层,

17、其中,第一聚合物的刻蚀速率小于或等于第二聚合物的刻蚀速率的二分之一。

18、在一些实施例中,在第二聚合物为聚甲基丙烯酸甲酯pmma的情况下,至少去除第二聚合物,以形成图案化的第一聚合物层包括:

19、利用紫外光对微相分离后的共聚物材料层进行照射;和

20、利用醋酸对紫外光照射后的共聚物材料层进行湿法刻蚀,以去除第二聚合物。

21、在一些实施例中,至少以所述图案化的第一聚合物层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部包括:

22、通过反应离子刻蚀法、飞秒激光刻蚀法、纳秒激光刻蚀法和湿法刻蚀中的至少一者对所述功能材料层进行刻蚀。

23、在一些实施例中,在所述功能材料层包括第一硅材料层的情况下,至少以所述图案化的第一聚合物层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部包括:

24、利用六氟化硫/氧气、含卤素气体/氧气以及硫化物/氧气中的至少一者对所述第一硅材料层进行反应离子刻蚀,以形成作为包含具有目标刻蚀深度的目标微结构的功能部的黑硅。

25、在一些实施例中,在所述功能材料层包括第一硅材料层的情况下,至少以所述图案化的第一聚合物层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部包括:

26、利用四甲基氢氧化铵tmah溶液和氢氧化钾koh溶液中的至少一者对所述第一硅材料层进行湿法刻蚀,以形成作为包含具有目标刻蚀深度的目标微结构的功能部的黑硅。

27、在一些实施例中,所述目标微结构包括以下中的至少一者:

28、在上下方向上延伸的纳米柱结构,其中,所述纳米柱结构的高度与所述目标刻蚀深度相一致;和

29、在垂直于所述上下方向的平面上延伸的纳米线结构,其中,所述纳米线结构的高度与所述目标刻蚀深度相一致。

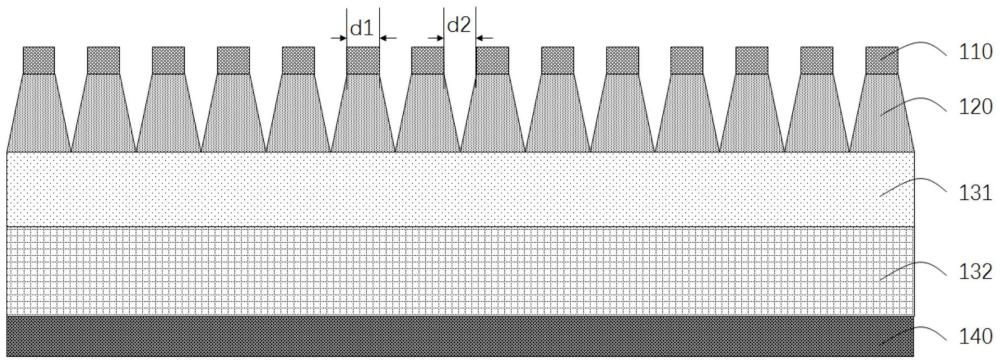

30、在一些实施例中,所述纳米柱结构的横截面的宽度在从下至上的方向上逐渐减小;或

31、所述纳米线结构的横截面的宽度在从下至上的方向上逐渐减小。

32、在一些实施例中,所述纳米柱结构的顶端横截面的最小宽度为20~30nm或30~100nm;或

33、所述纳米线结构的顶端横截面的最小宽度为20~30nm或30~100nm。

34、在一些实施例中,相邻两个纳米柱结构的顶端之间的间隔宽度为10~20nm或20~50nm;或

35、相邻两条纳米线结构的顶端之间的间隔宽度为10~20nm或20~50nm。

36、在一些实施例中,所述目标刻蚀深度为100~180nm或180~200nm。

37、在一些实施例中,在至少以所述图案化的第一聚合物层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部之后,所述器件制备方法还包括:

38、去除剩余的第一聚合物。

39、在一些实施例中,通过以下中的至少一者去除剩余的第一聚合物:

40、利用氧气对剩余的第一聚合物进行干法刻蚀;和

41、利用丙酮和异丙酮中的至少一者清洗剩余的第一聚合物。

42、在一些实施例中,所述待处理组件还包括布置在所述功能材料层上方的第一附加层,其中,

43、在所述待处理组件上方沉积共聚物材料层包括:

44、在所述第一附加层上方沉积所述共聚物材料层;以及

45、至少以所述图案化的第一聚合物层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部包括:

46、以所述图案化的第一聚合物层为掩模,对所述第一附加层进行刻蚀,以形成图案化的第一附加层;和

47、至少以所述图案化的第一附加层为掩模,对所述功能材料层进行刻蚀,直至所述功能材料层的至少一部分形成为包含具有目标刻蚀深度的目标微结构的功能部。

48、在一些实施例中,提供待处理组件包括:

49、通过物理气相沉积法和化学气相沉积法中的至少一者在所述功能材料层上方沉积所述第一附加层。

50、在一些实施例中,所述第一附加层的厚度为10~50nm。

51、在一些实施例中,所述第一附加层包括第一电极层,其中,所述第一电极层由透明且导电的第一电极材料形成。

52、在一些实施例中,所述第一电极材料包括氧化镉、氧化亚铜、氧化锡、氧化汞、氧化铟锡、铜/铬叠层、金属纳米线、石墨烯、氧化石墨烯和氧化锌中的至少一者。

53、在一些实施例中,以所述图案化的第一聚合物层为掩模,对所述第一附加层进行刻蚀,以形成图案化的第一附加层包括:

54、以所述图案化的第一聚合物层为掩模,利用六氟化硫/氧气以及三氟甲烷/氧气中的至少一者对所述第一附加层进行干法刻蚀,以形成图案化的第一附加层。

55、在一些实施例中,所述待处理组件还包括布置在所述功能材料层下方的基板。

56、在一些实施例中,在所述功能材料层包括第一硅材料层的情况下,所述基板包括第二硅材料层和第三硅材料层,其中,所述第二硅材料层布置在所述第一硅材料层与所述第三硅材料层之间,所述第一硅材料层与所述第二硅材料层的掺杂类型相反,所述第二硅材料层与所述第三硅材料层的掺杂类型相同,所述第一硅材料层的掺杂浓度大于所述第二硅材料层的掺杂浓度,且所述第二硅材料层的掺杂浓度小于所述第三硅材料层的掺杂浓度。

57、在一些实施例中,所述第一硅材料层和所述第三硅材料层中的至少一者被配置为通过外延层掺杂法或离子注入法而形成。

58、在一些实施例中,所述器件制备方法还包括:

59、在所述待处理组件的与所述功能部相对的一侧上沉积第二附加层。

60、在一些实施例中,所述第二附加层包括第二电极层,其中,所述第二电极层由导电的第二电极材料形成。

61、在一些实施例中,在所述待处理组件的与所述功能部相对的一侧上沉积第二附加层包括:

62、通过磁控溅射法、热蒸发法、电子束蒸发法和脉冲激光沉积法中的至少一者在所述待处理组件的与所述功能部相对的一侧上沉积第二电极材料;以及

63、对所沉积的第二电极材料进行退火处理。

64、在一些实施例中,所述第二电极材料包括金、银、铜、镍、铝、钛、钛铂硅、铱硅、钨硅和钯硅中的至少一者。

65、根据本公开的第二方面,提供了一种半导体器件,包括:

66、功能部,其中,所述功能部包含具有目标刻蚀深度的目标微结构;

67、第一电极层,其中,所述第一电极层设于所述功能部的顶端表面上,且所述第一电极层与所述功能部电连接;以及

68、第二电极层,其中,所述第二电极层与所述第一电极层关于所述功能部相对设置,且所述第二电极层与所述功能部电连接。

69、在一些实施例中,所述目标微结构包括以下中的至少一者:

70、在上下方向上延伸的纳米柱结构,其中,所述纳米柱结构的高度与所述目标刻蚀深度相一致;和

71、在垂直于所述上下方向的平面上延伸的纳米线结构,其中,所述纳米线结构的高度与所述目标刻蚀深度相一致。

72、在一些实施例中,所述功能部包括具有纳米柱结构的黑硅。

73、在一些实施例中,所述黑硅中的纳米柱结构的横截面的直径在从下至上的方向上逐渐减小,纳米柱结构的顶端横截面的最小宽度为20~30nm或30~100nm,相邻两个纳米柱结构的顶端之间的间隔宽度为10~20nm或20~50nm,以及纳米柱结构的高度为100~180nm或180~200nm。

74、在一些实施例中,所述第一电极层由氧化镉、氧化亚铜、氧化锡、氧化汞、氧化铟锡、铜/铬叠层、金属纳米线、石墨烯、氧化石墨烯和氧化锌中的至少一者形成,且所述第一电极层的厚度为10~50nm;以及

75、所述第二电极层由金、银、铜、镍、铝、钛铂硅、铱硅、钨硅和钯硅中的至少一者形成。

76、在一些实施例中,所述半导体器件还包括基板,其中,所述基板设于所述功能部与所述第二电极层之间,且所述第二电极层经由所述基板与所述功能部电连接。

77、在一些实施例中,所述基板包括第二硅材料层和第三硅材料层,其中,所述第二硅材料层布置在所述功能部与所述第三硅材料层之间,所述功能部与所述第二硅材料层的掺杂类型相反,所述第二硅材料层与所述第三硅材料层的掺杂类型相同,以使得所述功能部与所述基板共同形成pn结。

78、在一些实施例中,所述功能部的掺杂浓度为1019cm-3~1021cm-3;

79、所述第二硅材料层的掺杂浓度为1012cm-3~1015cm-3;以及

80、所述第三硅材料层的掺杂浓度为1018cm-3~1020cm-3。

81、在一些实施例中,所述半导体器件包括光电器件,其中,所述功能部被配置为对光进行吸收,所述第一电极层和所述第二电极层被配置为输出由所吸收的光产生的电信号。

82、在一些实施例中,所述半导体器件被配置为基于根据如上所述的器件制备方法而形成。

83、通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其他特征及其优点将会变得更为清楚。

本文地址:https://www.jishuxx.com/zhuanli/20240914/293811.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表