提升锗外延工艺质量的方法、器件中间结构及制作方法与流程

- 国知局

- 2024-09-14 14:23:11

本发明涉及硅基光电子,尤其涉及一种用于提升锗光电探测器的锗外延工艺质量的方法、器件中间结构及制作方法。

背景技术:

1、近年来,随着大数据和移动互联网的蓬勃发展,通信的速率和容量面临着更高的要求和挑战。光通信和光互连技术被认为是解决这一问题的有力手段,将逐渐取代传统的电通信和电互连技术,成为下一代通信系统发展的主流方向。

2、硅基光电子器件具有大带宽、低损耗、低成本、与cmos工艺兼容等优势,可以用于不同场景的光通信和光互连,结合多维复用和相干通信等技术进一步提升传输速率和容量,并降低成本和损耗,对未来通信系统的发展意义重大。

3、相对于锗硅(sige)材料来说,锗材料具有带隙小、吸收系数大、迁移率高和与硅工艺兼容等优点,被广泛地应用到硅基探测器的研制中。但由于硅和锗的晶格失配较大,达到4.2%,在硅上直接外延纯锗材料,将引入大量的失配位错,并使表面粗糙。高的位错密度将增加器件的漏电流,降低器件的性能;而粗糙的表面将增加器件制作的工艺难度。高性能的光电探测器是几乎所有光学系统都不可或缺的核心器件,因而减少位错密度和降低表面粗糙度,成为外延生长高质量硅基锗材料的关键。其中,锗外延前处理工艺是影响锗外延质量的一个重要工艺步骤。

4、请参阅图1-图2。锗外延前,需要通过对位于底层硅层10上的顶层介质层11进行刻蚀,在底层硅层10上形成锗外延窗口12。而在进行刻蚀后的清洗、干燥,以及等待过程中,在锗外延窗口12中裸露的底层硅层10表面上会形成一层薄薄的原生氧化硅层121,如图1所示。锗外延前处理工艺,正是为了去除锗外延窗口12中位于底层硅层10表面上的原生氧化硅层121与颗粒,避免底层硅层10表面上的原生缺陷对后续锗外延工艺的影响。而表面原生氧化硅层121与颗粒能否去除干净,在很大程度上将影响锗外延的缺陷及位错密度。常规的锗外延前处理工艺,通常是采用介质刻蚀方式,来去除该原生氧化硅层121及颗粒,但容易发生以下问题:一种是刻蚀后锗外延窗口12结构虽完好,但是原生氧化硅层121去除不干净;另一种是发生锗外延窗口上顶层介质层侧壁122的过刻蚀,造成在底层硅层10表面产生台阶裸露形态123等问题,如图2所示。这种台阶裸露问题,使得在随后的外延生长过程中,发生不同晶向的锗之间相互竞争生长现象,最终导致位错密度过大,甚至出现孔洞等缺陷,从而严重影响了锗外延的质量。

技术实现思路

1、本发明的目的在于克服现有技术存在的上述缺陷,提供一种提升锗外延工艺质量的方法、器件中间结构及制作方法。

2、为实现上述目的,本发明的技术方案如下:

3、本发明提供一种提升锗外延工艺质量的器件中间结构,包括:

4、半导体层;

5、设于所述半导体层表面上的顶层介质层;

6、设于所述顶层介质层表面上且底面位于所述半导体层表面下方的过渡外延窗口;

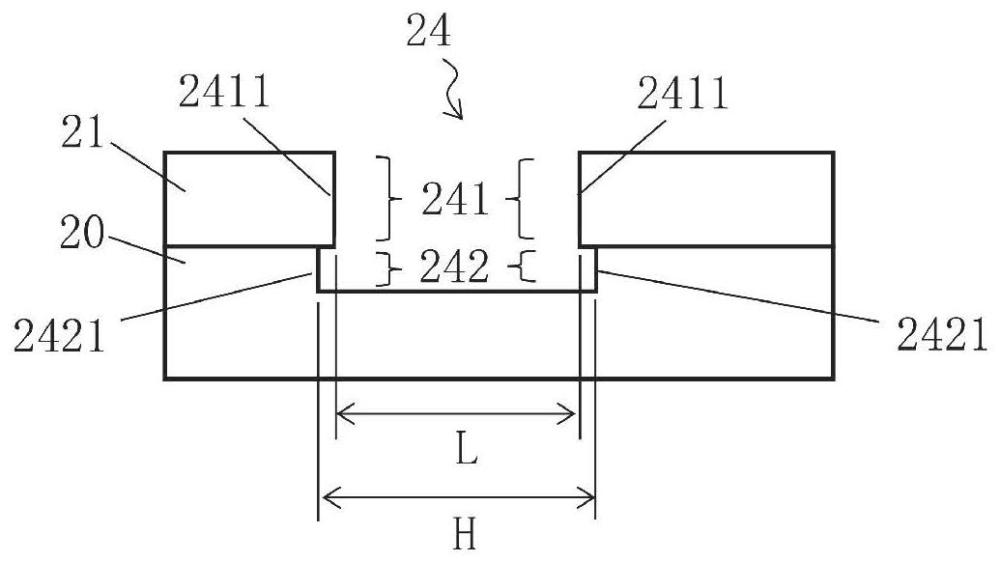

7、所述过渡外延窗口包括位于所述顶层介质层中的第一窗口部,和对应位于所述半导体层中的第二窗口部,所述第二窗口部的第二横向尺寸大于所述第一窗口部的第一横向尺寸,从而在所述第一窗口部下方形成内嵌空腔结构;

8、其中,所述第二横向尺寸与所述第一横向尺寸之间差值,与后续进行外延前处理工艺时对所述第一窗口部侧壁造成的过刻蚀量对应。

9、进一步地,还包括:位于所述过渡外延窗口底面以下的所述半导体层中的p型掺杂区和n型掺杂区。

10、进一步地,所述p型掺杂区和所述n型掺杂区形成横向pn结。

11、进一步地,所述第二窗口部的高度尺寸小于所述第二窗口部的第二横向尺寸。

12、进一步地,所述器件中间结构建立在绝缘体上硅衬底上,其中,所述半导体层由所述绝缘体上硅衬底的上层硅层形成。

13、本发明还提供一种提升锗外延工艺质量的器件中间结构的制作方法,包括:

14、提供具有半导体层的衬底;

15、在所述半导体层表面上形成顶层介质层;

16、在所述顶层介质层表面上向下形成第一过渡外延窗口,并使所述第一过渡外延窗口的底面位于所述半导体层的表面下方;

17、在所述第一过渡外延窗口位于所述半导体层中的内壁表面上形成所述半导体层材料的氧化物层;

18、去除所述半导体层材料的氧化物层,在所述第一过渡外延窗口基础上形成第二过渡外延窗口;其中,所述第二过渡外延窗口包括位于所述顶层介质层中的第一窗口部,和对应位于所述半导体层中的第二窗口部,所述第二窗口部的第二横向尺寸大于所述第一窗口部的第一横向尺寸,以在所述第一窗口部下方形成内嵌空腔结构。

19、进一步地,采用快速热氧化退火工艺,形成所述半导体层材料的氧化物层,和/或,采用炉管热氧化工艺,形成所述顶层介质层,和/或,采用湿法工艺,去除所述半导体层材料的氧化物层。

20、进一步地,所述半导体层材料的氧化物层厚度,与后续进行外延前处理工艺时对所述第一窗口部侧壁造成的过刻蚀量对应。

21、进一步地,在所述半导体层表面上形成顶层介质层之前,还包括:采用离子注入掺杂工艺,在所述半导体层中形成p型掺杂区和n型掺杂区,以形成横向pn结;以及,在所述顶层介质层表面上向下形成第一过渡外延窗口时,使所述第一过渡外延窗口的底面与所述pn结相接触。

22、本发明还提供一种提升锗外延工艺质量的方法,包括:

23、提供具有半导体层的衬底;

24、在所述半导体层表面上形成顶层介质层;

25、在所述顶层介质层表面上向下形成第一过渡外延窗口,并使所述第一过渡外延窗口的底面位于所述半导体层的表面下方;

26、在所述第一过渡外延窗口位于所述半导体层中的内壁表面上形成所述半导体层材料的氧化物层;

27、去除所述半导体层材料的氧化物层,在所述第一过渡外延窗口基础上形成第二过渡外延窗口;其中,所述第二过渡外延窗口包括位于所述顶层介质层中的第一窗口部,和对应位于所述半导体层中的第二窗口部,所述第二窗口部的第二横向尺寸大于所述第一窗口部的第一横向尺寸,以在所述第一窗口部下方形成内嵌空腔结构;

28、执行外延前处理工艺,形成最终外延窗口;其中,利用所述第二窗口部侧壁之间具有的所述第二横向尺寸,对所述外延前处理工艺对所述第一窗口部侧壁造成的过刻蚀量进行补偿,使所述第一横向尺寸与所述第二横向尺寸趋于一致;

29、执行锗外延工艺。

30、由上述技术方案可以看出,本发明通过预先形成具有内嵌空腔结构的过渡外延窗口(第二过渡外延窗口)结构,在执行外延前处理工艺时,可利用过渡外延窗口中内嵌空腔结构侧壁之间距离(第二横向尺寸)大于顶层介质层侧壁之间距离(第一横向尺寸)的结构特点,对外延前处理工艺对顶层介质层侧壁造成的过刻蚀量进行补偿,使第一横向尺寸与第二横向尺寸趋于一致,从而可在过渡外延窗口基础上形成满足外延工艺要求的最终外延窗口,能够有效改善锗外延工艺质量,减小锗外延缺陷与位错密度,由此能减小光电探测器暗电流,因此提升了硅光芯片性能。

本文地址:https://www.jishuxx.com/zhuanli/20240914/293755.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表