一种集成电路利用磊晶原理形成混晶层的方法与流程

- 国知局

- 2024-09-14 14:33:38

本发明属于混晶层形成,尤其涉及一种集成电路利用磊晶原理形成混晶层的方法。

背景技术:

1、在现行的集成电路混晶层形成技术中,晶圆首先被传送到tiw(钛钨)腔室进行tiw薄膜层的物理气相沉积(pvd)。随后,晶圆被传送到au(金)腔室继续沉积au薄膜层。这两个步骤通常都是一次性完成的,导致tiw层与au层之间形成的共晶层较小,粘附力较弱。这种结构在后续的bumping过程中,尤其是在进行shear剪切力测试时,容易导致tiw层的漏出,以及电镀出来的bump(凸点)的脱落,这严重影响了集成电路的可靠性和耐用性。

技术实现思路

1、针对上述情况,为克服现有技术的缺陷,本发明提供了一种集成电路利用磊晶原理形成混晶层的方法。

2、为了实现上述目的,采用了如下技术方案:本发明提供了一种集成电路利用磊晶原理形成混晶层的方法,包括如下步骤:

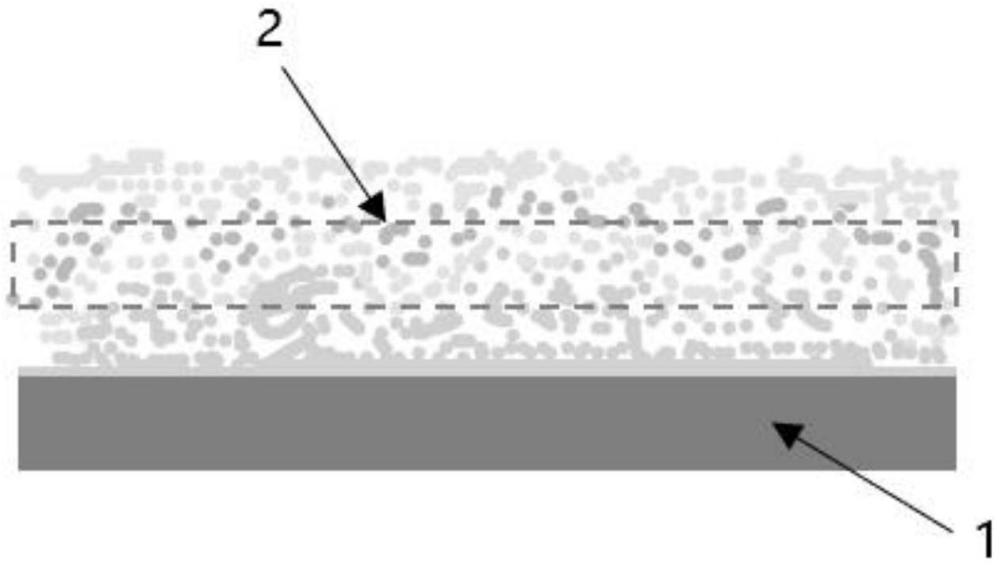

3、s1、晶粒聚结及暂停:将晶圆放入tiw腔室中,在腔室内对晶圆进行tiw薄膜层的物理气相沉积,监控tiw层的沉积过程,直至晶粒开始聚结,形成连续的薄膜,当晶粒聚结达到一定阶段,表面出现缝隙和凹坑时,暂停沉积过程,此时tiw层表面有很多缝隙及凹坑;

4、s2、au薄膜填补:将晶圆从tiw腔室转移到au腔室,在au腔室内对晶圆进行au薄膜的物理气相沉积,通过沉积的au薄膜填补tiw层表面的缝隙和凹坑,增强其表面平整度;

5、s3、tiw层二次沉积:将晶圆再次送回tiw腔室进行tiw薄膜的二次沉积,继续沉积tiw薄膜,直至达到工艺要求的厚度,监控沉积过程,确保tiw层的均匀性和完整性,达到所需厚度后暂停沉积;

6、s4、共晶层形成:在tiw层表面再次进行au薄膜的沉积,当au薄膜达到工艺规定的厚度后停止沉积,通过在tiw层上沉积au薄膜,形成tiw和au的共晶层,这增强了材料间的结合力,共晶层的形成是为了提高集成电路结构稳定性和可靠性;

7、s5、电镀凸块:在ubm层完全成长好后,,通过电镀工艺在ubm层上生长出金凸块。

8、进一步地,所述方法根据薄膜沉积原理。

9、进一步地,所述tiw层用于保护晶圆表面及pad。

10、进一步地,所述au层作为种子层,供电镀生长出金凸块。

11、进一步地,所述步骤s2中,通过au薄膜填补tiw层的缝隙,使金属间产生更大的共晶层,使薄膜间黏附力增强。

12、进一步地,所述步骤s5后进一步还包括对晶圆进行shear剪切力测试。

13、进一步地,所述shear剪切力测试用来检测金凸块的机械剪切强度,检验金凸块在剪切力作用下是否会发生损坏,如tiw层的漏出或金凸块的脱落,shear剪切力测试的目的是确保晶圆在实际使用中,这些连接点能够承受预期的机械应力,从而保证电子组件的可靠性和耐用性。

14、本发明的有益效果是:本发明通过在tiw层沉积过程中引入au薄膜填补缝隙的步骤,增加了tiw和au之间的共晶层面积,从而显著提高了薄膜间的粘附力,由于共晶层的增强,bump的机械剪切强度得到提升,在shear剪切力测试中表现出更好的性能,减少了tiw层漏出和bump脱落的风险,通过形成更稳定的共晶层,集成电路的整体可靠性得到显著提高,确保了在实际使用中的耐用性和稳定性,改进后的混晶层形成方法能够提升集成电路的性能,尤其是在需要高可靠性和机械强度的应用场景中。

技术特征:1.一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:包括如下步骤:

2.根据权利要求1所述的一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:所述方法根据薄膜沉积原理。

3.根据权利要求2所述的一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:所述tiw层用于保护晶圆表面及pad。

4.根据权利要求3所述的一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:所述au层作为种子层,供电镀生长出金凸块。

5.根据权利要求4所述的一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:所述步骤s2中,通过au薄膜填补tiw层的缝隙,使金属间产生更大的共晶层,使薄膜间黏附力增强。

6.根据权利要求5所述的一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:所述步骤s5后进一步还包括对晶圆进行shear剪切力测试。

7.根据权利要求6所述的一种集成电路利用磊晶原理形成混晶层的方法,其特征在于:所述shear剪切力测试用来检测金凸块的机械剪切强度,检验金凸块在剪切力作用下是否会发生损坏,如tiw层的漏出或金凸块的脱落,shear剪切力测试的目的是确保晶圆在实际使用中,这些连接点能够承受预期的机械应力,从而保证电子组件的可靠性和耐用性。

技术总结本发明公开了混晶层形成技术领域的一种集成电路利用磊晶原理形成混晶层的方法,包括如下步骤:S1、晶粒聚结及暂停;S2、Au薄膜填补;S3、TiW层二次沉积;S4、共晶层形成;S5、电镀凸块。本发明通过在TiW层沉积过程中引入Au薄膜填补缝隙的步骤,增加了TiW和Au之间的共晶层面积,从而显著提高了薄膜间的粘附力,由于共晶层的增强,Bump的机械剪切强度得到提升,在Shear剪切力测试中表现出更好的性能,减少了TiW层漏出和Bump脱落的风险,通过形成更稳定的共晶层,集成电路的整体可靠性得到显著提高,确保了在实际使用中的耐用性和稳定性,改进后的混晶层形成方法能够提升集成电路的性能,尤其是在需要高可靠性和机械强度的应用场景中。技术研发人员:高利,赖忠良受保护的技术使用者:日月新半导体(昆山)有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/294771.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表