包括沟槽晶体管基元单元的半导体装置的制作方法

- 国知局

- 2024-09-14 14:53:58

本公开涉及一种半导体装置,特别地涉及一种包括沟槽晶体管基元单元的半导体装置。

背景技术:

1、新生代半导体装置(例如,绝缘栅双极晶体管(igbt)或金属氧化物半导体场效应晶体管(mosfet))的技术开发旨在通过缩小装置几何形状来改进电气装置特性并且减小成本。虽然通过缩小装置几何形状可减小成本,但当增加每单位面积的装置功能时必须满足各种折衷和挑战。例如,面积比接通状态电阻ronxa和接通效率之间的折衷需要设计优化。

2、因此,存在对改进的半导体装置的需要。

技术实现思路

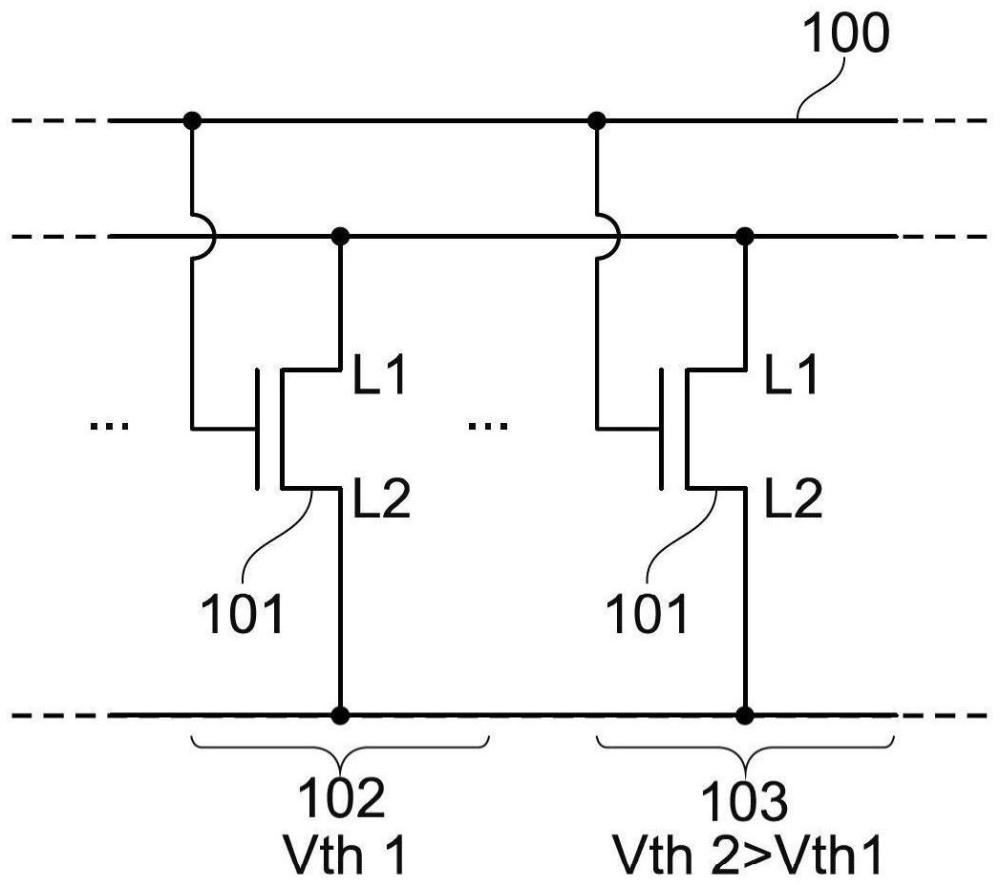

1、本公开的示例涉及一种半导体装置。半导体装置包括:半导体主体,包括沟槽晶体管基元阵列。沟槽晶体管基元阵列包括第一沟槽晶体管基元单元和第二沟槽晶体管基元单元。基于第一沟槽晶体管基元单元的晶体管基元和基于第二沟槽晶体管基元单元的晶体管基元按照电气方式并联连接。第一沟槽晶体管基元单元包括第一阈值电压。第二沟槽晶体管基元单元包括大于第一阈值电压的第二阈值电压。在接通晶体管基元阵列的标称电流时的du/dt的绝对值是在接通晶体管基元阵列的标称电流的10%时的du/dt的绝对值的至少50%,du/dt是沟槽晶体管基元阵列的负载端子之间的电压u的时间导数。

2、本公开的另一示例涉及一种用于制造半导体装置的方法。所述方法包括:在半导体主体中形成沟槽晶体管基元阵列。沟槽晶体管基元阵列包括第一沟槽晶体管基元单元和第二沟槽晶体管基元单元。基于第一沟槽晶体管基元单元的晶体管基元和基于第二沟槽晶体管基元单元的晶体管基元按照电气方式并联连接。第一沟槽晶体管基元单元包括第一阈值电压。第二沟槽晶体管基元单元包括大于第一阈值电压的第二阈值电压。在接通晶体管基元阵列的标称电流时的du/dt的绝对值是在接通晶体管基元阵列的标称电流的10%时的du/dt的绝对值的至少50%,du/dt是沟槽晶体管基元阵列的负载端子之间的电压u的时间导数。

3、本领域技术人员将会在阅读下面的详细描述时并且在观看附图时意识到另外的特征和优点。

技术特征:1.一种半导体装置(100),包括:

2.如前一权利要求所述的半导体装置(100),其中第一内部栅极电阻器(rg1)被串联连接在所述第一沟槽晶体管基元单元(102)的栅电极(g1)和栅极焊盘(gp)之间,并且第二内部栅极电阻器(rg2)被串联连接在所述第二沟槽晶体管基元单元(103)的栅电极(g2)和所述栅极焊盘(gp)之间,其中所述第一内部栅极电阻器(rg1)小于所述第二内部栅极电阻器(rg2)。

3.如前一权利要求所述的半导体装置(100),其中所述第一内部栅极电阻器(rg1)和所述第二内部栅极电阻器(rg2)包括掺杂多晶硅,并且所述第一内部栅极电阻器(rg1)的横截面大于所述第二内部栅极电阻器(rg2)的横截面。

4.如前面权利要求之一所述的半导体装置(100),其中所述第一沟槽晶体管基元单元(102)内的源极区或发射极区(1041)的份额小于所述第二沟槽晶体管基元单元(103)内的源极区或发射极区(1241)的份额。

5.如前一权利要求所述的半导体装置(100),其中至少所述第一沟槽晶体管基元单元(102)包括第一台面区(1061)和第二台面区(1062),并且所述源极区或发射极区(1041)被布置在所述第一台面区(1061)中并且在所述第二台面区(1062)中被省略,其中与在所述第二沟槽晶体管基元单元(103)中相比,第一台面区(1061,1261)与第二台面区(1062,1262)之比在所述第一沟槽晶体管基元单元(102)中更大。

6.如前面两个权利要求中任一项所述的半导体装置(100),其中至少所述第一沟槽晶体管基元单元(102)包括第一台面区(1061)和第二台面区(1062),并且所述第二台面区(1062)沿侧向受到沟槽电极结构局限,所述沟槽电极结构具有按照电气方式与栅电极(g1)断开连接的沟槽电极。

7.如前一权利要求所述的半导体装置(100),其中所述第二台面区(1062)按照电气方式连接到所述第二台面区(1062)之上的源极或发射极电极(l2)。

8.如前面两个权利要求中任一项所述的半导体装置(100),其中所述沟槽电极结构按照电气方式连接到源极或发射极电极(l2)。

9.如前一权利要求所述的半导体装置(100),其中与所述第二沟槽晶体管基元单元(103)的栅电极(g2)相比,所述第一沟槽晶体管基元单元(102)的栅电极(g1)具有更大的基元单元有源区域份额。

10.如前面权利要求中任一项所述的半导体装置(100),其中所述第一沟槽晶体管基元单元(102)包括第一势垒区(1081),所述第一势垒区(1081)具有不同于第二导电型的第一导电型,所述第一势垒区(1081)被布置在所述第二导电型的漂移区(112)和所述第一导电型的主体区(111)之间。

11.如前一权利要求所述的半导体装置(100),其中所述第一势垒区(1081)仅存在于所述第一沟槽晶体管基元单元(102)中,或者与在所述第二沟槽晶体管基元单元(103)中相比包括更高的掺杂浓度。

12.如前面两个权利要求中任一项所述的半导体装置(100),其中所述第一势垒区(1081)沿垂直方向受到所述漂移区(112)局限,并且通过至少一个其它半导体区(1121)而与所述主体区(111)分离。

13.如前面权利要求中任一项所述的半导体装置(100),其中所述第二沟槽晶体管基元单元(103)包括第二势垒区(1282),所述第二势垒区(1282)具有不同于第一导电型的第二导电型,所述第二势垒区(1282)被布置在所述第一导电型的主体区(121)和所述第二导电型的漂移区(122)之间,其中所述第二势垒区(1282)的最大掺杂浓度大于与所述第二势垒区(1282)的底侧邻接的漂移区部分的最大掺杂浓度。

14.如前一权利要求所述的半导体装置(100),其中所述第二势垒区(1081)仅存在于所述第二沟槽晶体管基元单元(102)中,或者与在所述第一沟槽晶体管基元单元(103)中相比包括更高的掺杂浓度。

15.如前面权利要求中任一项所述的半导体装置(100),其中所述第一沟槽晶体管基元单元(102)的每面积的沟道宽度(w1)小于所述第二沟槽晶体管基元单元(103)的每面积的沟道宽度(w2)。

16.如前面权利要求中任一项所述的半导体装置(100),其中所述第二沟槽晶体管基元单元(103)与所述第一沟槽晶体管基元单元(102)的不同之处在于沿侧向图案化的集电极区(1381,1382)。

17.如前面权利要求中任一项所述的半导体装置(100),其中所述第一沟槽晶体管基元单元(102)具有所述沟槽晶体管基元阵列的有源区域的5%到20%份额。

18.如前面权利要求中任一项所述的半导体装置(100),其中所述沟槽晶体管基元阵列还包括第三沟槽晶体管基元单元(109),所述第三沟槽晶体管基元单元(109)包括大于所述第二阈值电压(vth2)的第三阈值电压;并且其中

19.如前面权利要求中任一项所述的半导体装置(100),其中所述半导体装置(100)是n沟道igbt,并且与所述第二沟槽晶体管基元单元(103)的所述pnp晶体管增益相比,所述第一沟槽晶体管基元单元(102)的所述pnp晶体管增益更大。

20.一种半导体装置(100),包括:

21.一种用于制造半导体装置(100)的方法,所述方法包括:

技术总结本公开涉及包括沟槽晶体管基元单元的半导体装置。提出一种半导体装置。半导体装置包括:半导体主体,包括沟槽晶体管基元阵列。沟槽晶体管基元阵列包括第一沟槽晶体管基元单元和第二沟槽晶体管基元单元。基于第一沟槽晶体管基元单元的晶体管基元和基于第二沟槽晶体管基元单元的晶体管基元按照电气方式并联连接。第一沟槽晶体管基元单元包括第一阈值电压。第二沟槽晶体管基元单元包括大于第一阈值电压的第二阈值电压。在接通晶体管基元阵列的标称电流时的dU/dt的绝对值是在接通晶体管基元阵列的标称电流的10%时的dU/dt的绝对值的至少50%,dU/dt是沟槽晶体管基元阵列的负载端子之间的电压U的时间导数。技术研发人员:A·菲利普,R·巴伯斯克,F·普菲尔施,F·J·尼德诺斯泰德受保护的技术使用者:英飞凌科技股份有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/296307.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表