纠错码编码电路和包括该电路的半导体器件的制作方法

- 国知局

- 2024-10-21 14:25:28

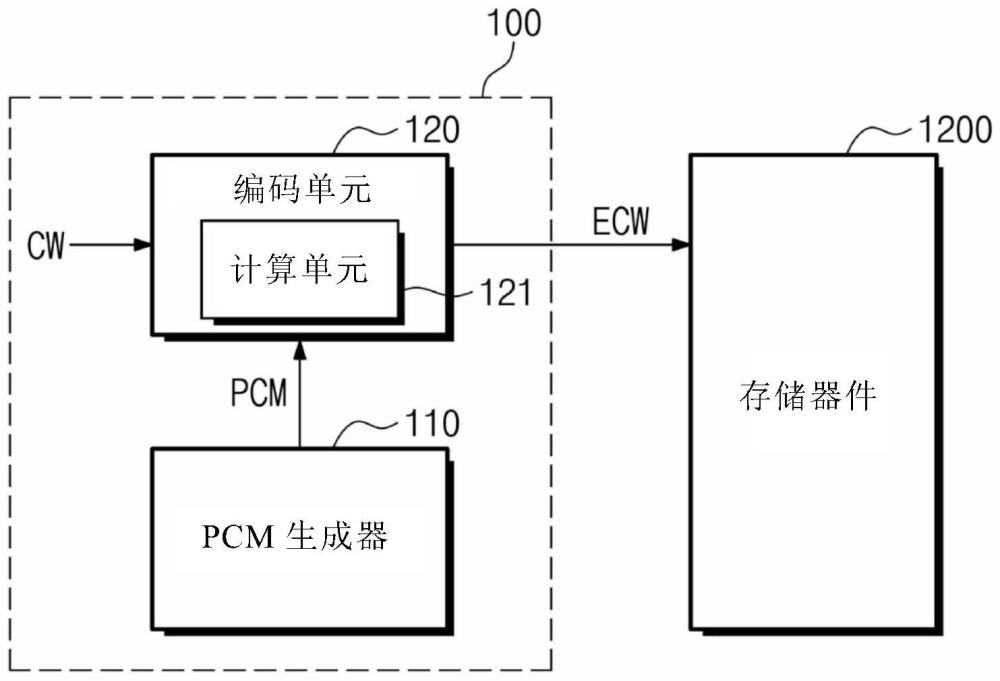

本文描述的本公开的实施例涉及纠错码(error correcting code,ecc)编码电路和包括该ecc编码电路的半导体器件,更具体地,涉及一种对码字进行编码以生成编码码字的ecc编码器。

背景技术:

1、半导体器件可以包括易失性存储器件和非易失性存储器件。易失性存储器件可以指当电源被切断时丢失存储在其中的数据的存储器件。易失性存储器件可以包括静态随机存取存储器(static random access memory,sram)、动态ram(dram)、同步dram等。非易失性存储器件可以指即使当电源被切断时也保持存储在其中的数据的存储器件。非易失性存储器件可以包括只读存储器(read only memory,rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)、闪存器件、相变ram(pram)、磁性ram(mram)、电阻式ram(rram)、铁电ram(fram)等。闪存器件被主要分类为nor型闪存器件和nand型闪存器件。

2、当读取在存储器件中编程的数据时,可能发生错误。当在读取操作期间发生错误时,读取数据可能包括错误。为了纠正读取数据中的错误,可以使用诸如博斯-乔赫里-霍克文黑姆(bose-chaudhuri-hocquenghem,bch)码、里德-所罗门(reed-solomon,rs)码、低密度奇偶校验(low density parity check,ldpc)码和turbo码的编码调制来执行纠错码(ecc)运算。然而,由于半导体器件的制造设计规则的持续收缩,位错误可能迅速地增加,并且半导体器件的生产率可能降低。因此,改进ecc运算的效率是有用的。

技术实现思路

1、本公开的实施例提供了一种编码电路,所述编码电路包括ecc编码器,所述ecc编码器使用奇偶校验矩阵结构,能够进行低复杂度编码,同时改进误差底限和瀑布特性。

2、根据实施例,纠错码(ecc)编码器基于奇偶校验矩阵对码字进行编码,并且生成包括信息位和奇偶位的编码码字(ecw)。所述奇偶校验矩阵被划分成与所述信息位相对应的信息部分和与所述奇偶位相对应的奇偶部分。所述奇偶部分包括:分块矩阵t,所述分块矩阵t包括按双对角结构排列的多个第一子矩阵;分块矩阵b,所述分块矩阵b包括第一子矩阵和第1-a子矩阵;分块矩阵d,所述分块矩阵d由所述第一子矩阵组成;以及分块矩阵e,所述分块矩阵e包括所述第一子矩阵和掩蔽的第1-(a+1)子矩阵。所述分块矩阵b和所述分块矩阵d位于相同子列中。所述分块矩阵t和所述分块矩阵e位于相同子列中。所述第一子矩阵处于所述分块矩阵b中的位置先于所述掩蔽的第1-(a+1)子矩阵处于所述分块矩阵e中的位置。所述第1-a子矩阵处于所述分块矩阵b中的位置先于所述第一子矩阵处于所述分块矩阵e中的位置。所述第一子矩阵被定义为大小为z×z的单位矩阵。所述第1-a子矩阵被定义为通过对所述第一子矩阵执行左循环移位“a”次而获得的矩阵。所述掩蔽的第1-(a+1)子矩阵被定义为在通过对所述第一子矩阵执行左循环移位“a+1”次而获得的矩阵中掩蔽第一行的矩阵。

3、根据实施例,一种半导体器件可以包括ecc编码器,所述ecc编码器被配置为:基于奇偶校验矩阵对码字进行编码,并且生成包括信息位和奇偶位的编码码字(ecw)。所述奇偶校验矩阵被划分成与所述信息位相对应的信息部分和与所述奇偶位相对应的奇偶部分。所述奇偶部分包括:多个子行和多个子列;分块矩阵t,所述分块矩阵t包括按双对角结构排列的多个第一子矩阵;分块矩阵b,所述分块矩阵b包括:第一列向量,所述第一列向量位于所述多个子列中的第一子列中并且包括第1-a1子矩阵,以及第二列向量,所述第二列向量位于所述多个子列中的第二子列中并且包括第1-a2子矩阵;分块矩阵c,所述分块矩阵包括:第一列向量,所述第一列向量位于所述多个子列中的第一子列中并且包括第1-a1子矩阵,以及第二列向量,所述第二列向量位于所述多个子列中的第二子列中并且包括第1-a2子矩阵;分块矩阵e,所述分块矩阵e包括:第一行向量,所述第一行向量位于所述多个子行中的第一子行中并且包括第一子矩阵,以及第二行向量,所述第二行向量位于所述多个子行中的第二子行中并且包括所述第一子矩阵;以及分块矩阵d,所述分块矩阵d包括:掩蔽的第1-(a1+1)子矩阵,所述掩蔽的第1-(a1+1)子矩阵位于所述第一子列和所述第一子行中;第1-(a1-2)子矩阵,所述第1-(a1-2)子矩阵位于所述第一子列和所述第二子行中;以及掩蔽的第1-(a2+1)子矩阵,所述掩蔽的第1-(a2+1)子矩阵位于所述第二子列和所述第二子行中。所述第1-a1子矩阵处于所述第一列向量中的位置先于所述第一子矩阵处于所述第一行向量中的位置。所述分块矩阵b的所述第1-a2子矩阵处于所述第二列向量中的位置先于所述分块矩阵e的所述第一子矩阵处于所述第二行向量中的位置。所述第一子矩阵被定义为大小为z×z的单位矩阵。每一个所述第1-aj子矩阵被定义为通过对所述第一子矩阵执行左循环移位“aj”次而获得的矩阵。所述掩蔽的第1-(aj+1)子矩阵被定义为在通过对所述第一子矩阵执行左循环移位“aj+1”次而获得的矩阵中掩蔽第一行的矩阵。所述第1-(aj-2)子矩阵被定义为通过对所述第一子矩阵执行左循环移位“aj-2”次而获得的矩阵。

4、根据实施例,一种半导体器件可以包括ecc编码器,所述ecc编码器被配置为:基于奇偶校验矩阵生成包括信息位和奇偶位的编码码字。所述ecc编码器可以包括:位累加器,所述位累加器通过执行将下三角矩阵乘以输入位的运算来生成中间位;以及第一移位器,所述第一移位器通过执行将第1-(z-ai)子矩阵乘以所述中间位的运算来生成所述奇偶位。

技术特征:1.一种编码电路,所述编码电路包括:

2.根据权利要求1所述的编码电路,其中,所述纠错码编码电路包括:

3.根据权利要求2所述的编码电路,其中,所述编码单元还被配置为执行用于计算出所述奇偶位的运算,并且

4.根据权利要求3所述的编码电路,其中,所述奇偶位包括与所述分块矩阵b和分块矩阵d进行运算的第一奇偶位以及与所述分块矩阵t和所述分块矩阵e进行运算的第二奇偶位,并且

5.根据权利要求2所述的编码电路,其中,所述奇偶校验矩阵生成器包括:

6.根据权利要求5所述的编码电路,其中,划分到所述分块矩阵bb和所述分块矩阵db中的列的权重是3,并且

7.根据权利要求5所述的编码电路,其中,所述分块矩阵bb包括“1”的第一分量和第二分量以及“0”的多个分量,

8.根据权利要求7所述的编码电路,其中,所述分块矩阵bb的“1”的第一分量的位置值小于所述分块矩阵eb的“1”的第一分量的位置值,并且

9.根据权利要求8所述的编码电路,其中,所述矩阵变换单元被配置为通过以下操作来生成所述奇偶部分:

10.根据权利要求1所述的编码电路,其中,所述奇偶部分的行对应于校验节点,

11.一种半导体器件,所述半导体器件包括:

12.根据权利要求11所述的半导体器件,其中,所述纠错码编码器包括:

13.根据权利要求12所述的半导体器件,其中,所述奇偶校验矩阵生成器包括:

14.根据权利要求13所述的半导体器件,其中,所述分块矩阵bb包括:

15.根据权利要求14所述的半导体器件,其中,所述矩阵变换单元被配置为通过以下操作来生成所述奇偶部分:

16.一种半导体器件,所述半导体器件包括:

17.根据权利要求16所述的半导体器件,其中,所述纠错码编码器还包括:

18.根据权利要求17所述的半导体器件,其中,“ai”和“a(i-1)-2”都是0。

19.根据权利要求17所述的半导体器件,其中,所述输入位、所述中间位和所述变换位均以包括多个位的向量格式表达。

20.根据权利要求16所述的半导体器件,其中,所述“ai”是0。

技术总结一种半导体器件可以包括:纠错码(ECC)编码器,所述ECC编码器基于奇偶校验矩阵对码字进行编码,并且生成包括信息位和奇偶位的编码码字。所述奇偶校验矩阵被划分成与所述信息位相对应的信息部分和与所述奇偶位相对应的奇偶部分。所述奇偶部分包括:分块矩阵T,所述分块矩阵T包括按双对角结构排列的多个第一子矩阵;分块矩阵B,所述分块矩阵B包括第一子矩阵和第1‑a子矩阵;分块矩阵D,所述分块矩阵D由所述第一子矩阵组成;以及分块矩阵E,所述分块矩阵E包括所述第一子矩阵和掩蔽的第1‑(a+1)子矩阵。所述第一子矩阵处于所述分块矩阵B中的位置先于所述掩蔽的第1‑(a+1)子矩阵处于所述分块矩阵E中的位置。技术研发人员:全基俊,朴暻彬,孙弘乐,梁大烈,柳根荣,全甫晥,黄映竣受保护的技术使用者:三星电子株式会社技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/318091.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。