半导体存储装置以及读取半导体存储装置的方法与流程

- 国知局

- 2024-07-31 19:14:21

本发明有关于半导体存储装置,特别是有关于具备检测错误并订正的功能的半导体存储装置。

背景技术:

1、在已知半导体存储装置中,已知在回应从外部装置(例如存储器控制器等)输入的读取指令而输出的数据包含错误位时,有具备检测错误并订正的功能者,例如错误更正码(error correcting code,ecc)。例如issi所公开的型号为is67wvh16m8edall的hyperramtm产品,在输出到外部的数据包含错误时,让用以指示ecc事件发生的err信号变成有效。

2、然而,对于外部装置来说,无法根据变成有效的err信号来辨识出除了被输出的数据发生错误之外的事情,亦即难以辨识错误的具体内容(例如检测到可订正的数目(例如1位)的错误位,或者,检测到不可订正的数目(例如2位以上)的错误位等)。

技术实现思路

1、有鉴于上述课题,本发明的目的为提供一种半导体存储装置,可以容易地辨识发生于被输出的数据的错误的具体内容。

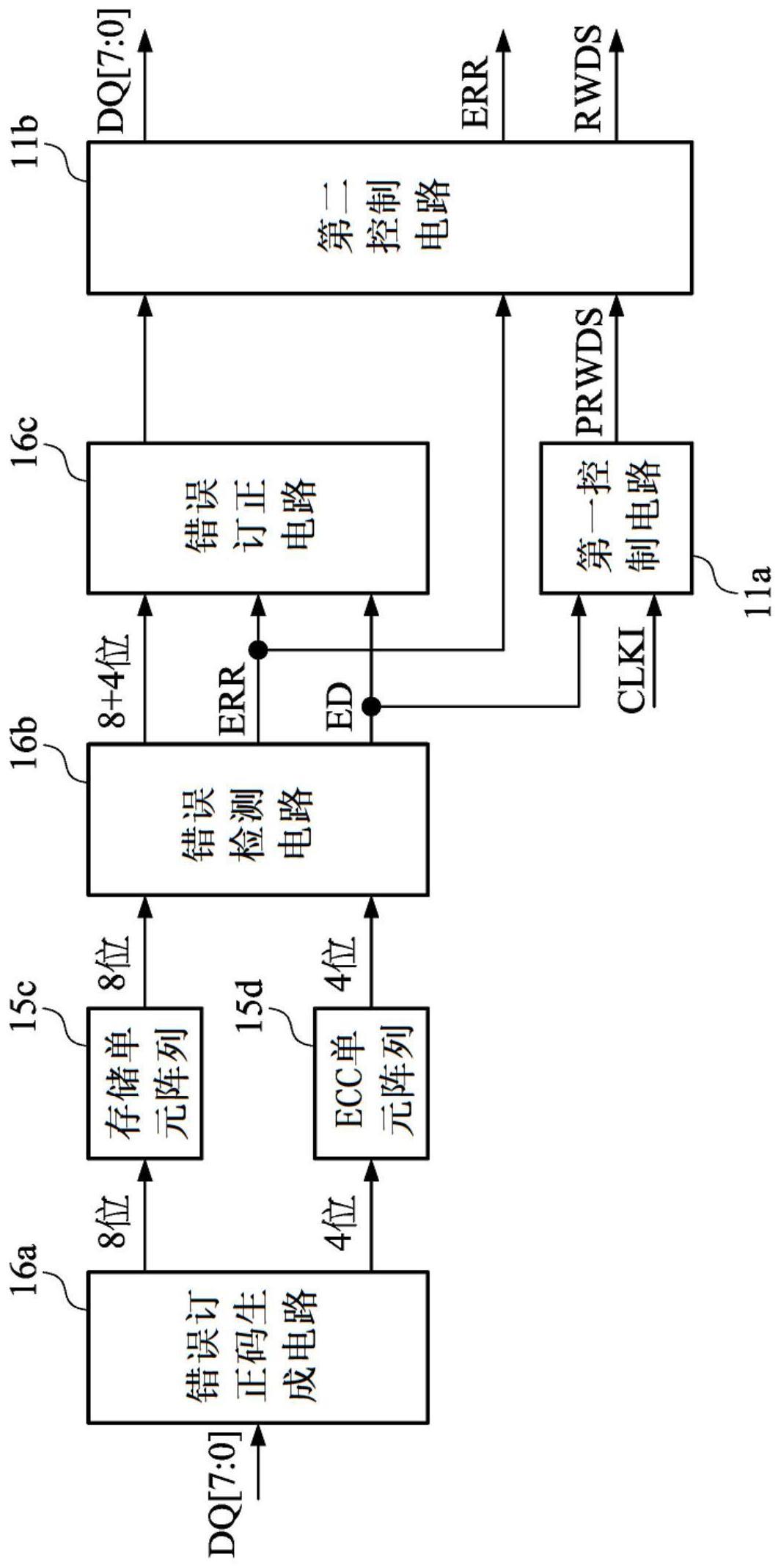

2、为了解决上述课题,本发明提供一种半导体存储装置,包括:存储单元阵列,包含多个存储单元;错误检测订正电路,耦接至该存储单元阵列,且被配置为检测从该存储单元阵列输出的数据中的错误位,当该数据包含可订正的错误位时,将用以表示检测到该可订正错误位的错误检测信号变成有效,且订正该可订正的错误位;及输入与输出电路,耦接至该错误检测订正电路,该输入与输出电路被配置为自该错误检测订正电路接收该数据及该错误检测信号,且输出数据选通信号、该数据及该错误检测信号,其中在该数据包含该可订正的错误位时,该数据选通信号具有响应于时钟信号的多个时钟脉冲,在该数据包含不可订正位时,该输入与输出电路停止产生该数据选通信号的该些时钟脉冲的至少一个,其中该不可订正位的错误位数大于该错误检测订正电路可订正的错误位数。

3、根据本发明的一实施例,不只可以经由让错误检测信号变成有效,辨识出输出数据包含可订正错误位,同时也可以经由停止数据选通信号的时钟脉冲,辨识出输出数据包含不可订正位。因此,可以根据错误检测信号以及数据选通信号,容易地辨识于被输出的数据发生的错误的具体内容。

技术特征:1.一种半导体存储装置,其特征在于,包括:

2.如权利要求1所述的半导体存储装置,其特征在于:

3.如权利要求2所述的半导体存储装置,其特征在于,该输入与输出电路仅在该检测信号变成有效的期间,停止产生该数据选通信号的所述多个时钟脉冲的至少一个。

4.如权利要求2所述的半导体存储装置,其特征在于,在该数据包含该不可订正位时,该输入与输出电路停止产生该数据选通信号的所述多个时钟脉冲,直到包含该数据的数据序列的读取操作完成为止。

5.如权利要求1所述的半导体存储装置,其特征在于,该错误检测订正电路被配置为仅在包含该可订正错误位的该数据被输出的期间,将该错误检测信号变成有效。

6.如权利要求1所述的半导体存储装置,其特征在于,该错误检测订正电路被配置为,在该数据包含该可订正错误位时,将该错误检测信号变成有效,直到包含该数据的数据序列的读取操作完成为止。

7.如权利要求2所述的半导体存储装置,其特征在于:

8.如权利要求7所述的半导体存储装置,其特征在于,该第二控制电路被配置为在包含该存储单元阵列、该错误检测订正电路、以及该第一控制电路的半导体芯片没有被选择时,将从该半导体芯片输出的该错误检测信号、该数据、以及该数据选通信号中的至少一个设定为高阻抗状态。

9.如权利要求7所述的半导体存储装置,其特征在于,该第一控制电路包括数据选通驱动器,且该数据选通驱动器包括:

10.如权利要求9所述的半导体存储装置,其特征在于,该逻辑门电路包括串联于高电位侧电源与低电位侧电源之间的p通道型金属氧化物半导体场效应晶体管mosfet与n通道型mosfet,且该p通道型mosfet与该n通道型mosfet的栅极均耦接至该时钟信号;

11.如权利要求10所述的半导体存储装置,其特征在于,该数据选通驱动器还包括:

12.如权利要求7所述的半导体存储装置,其特征在于,还包括指令解码器,耦接至该第二控制电路,其被配置为根据芯片选择信号生成活化信号,且将该活化信号输出至该第二控制电路。

13.如权利要求12所述的半导体存储装置,其特征在于,该第二控制电路包括芯片外驱动器,且该芯片外驱动器包括:

14.如权利要求13所述的半导体存储装置,其特征在于,当该活化信号为高电平,且该数据、该数据选通信号以及该错误检测信号中的任一个为高电平时,该上拉电路为开启状态,且该下拉电路为关闭状态,使该芯片外驱动器输出高电平。

15.如权利要求13所述的半导体存储装置,其特征在于,当该活化信号为高电平,且该数据、该数据选通信号以及该错误检测信号中的任一个为低电平时,该上拉电路为关闭状态,且该下拉电路为开启状态,使该芯片外驱动器输出低电平。

16.如权利要求13所述的半导体存储装置,其特征在于,该上拉电路控制电路包括第一p通道型mosfet、第一n通道型mosfet、第二n通道型mosfet及第二p通道型mosfet,该第一p通道型mosfet、该第一n通道型mosfet及该第二n通道型mosfet串联连接于高电位侧电源与低电位侧电源之间,该第二p通道型mosfet耦接于该第一p通道型mosfet及该第一n通道型mosfet间的连接节点及该高电位侧电源之间,该第一p通道型mosfet及该第一n通道型mosfet间的该连接节点被配置以输出该第一门控制信号,该数据、该数据选通信号、以及该错误检测信号中的任一个被输入到该第一p通道型mosfet与该第二n通道型mosfet各自的栅极,该活化信号被输入到该第一n通道型mosfet与该第二p通道型mosfet各自的栅极。

17.如权利要求13所述的半导体存储装置,其特征在于,该下拉电路控制电路包括第一p通道型mosfet、第二p通道型mosfet、第一n通道型mosfet及第二n通道型mosfet,该第一p通道型mosfet、该第二p通道型mosfet及该第一n通道型mosfet串联连接于高电位侧电源与低电位侧电源之间,该第二n通道型mosfet耦接于该第二p通道型mosfet与该第一n通道型mosfet之间的连接节点及该低电位侧电源之间,该第二p通道型mosfet与该第一n通道型mosfet之间的该连接节点被配置以输出该第二门控制信号,该数据、该数据选通信号、以及该错误检测信号中的任一个的逻辑反转信号被输入到该第一p通道型mosfet与该第二n通道型mosfet各自的栅极,该活化信号的逻辑反转信号被输入到该第二p通道型mosfet与该第一n通道型mosfet各自的栅极。

18.一种读取半导体存储装置的方法,其特征在于,包括:

19.如权利要求18所述的读取半导体存储装置的方法,其特征在于,该半导体存储装置包括多个半导体芯片,且该方法还包括将从所述多个半导体芯片中未被选择者所输出的该错误检测信号、该数据、以及该数据选通信号中的至少一个设定为高阻抗状态。

20.如权利要求18所述的读取半导体存储装置的方法,其特征在于,该停止产生该数据选通信号的所述多个时钟脉冲的至少一个的步骤包括:

技术总结本发明公开了一种半导体存储装置以及读取半导体存储装置的方法,可以容易地辨识发生于输出数据的错误的具体内容。半导体存储装置包括:存储单元阵列,包含多个存储单元;错误检测订正电路,检测并订正包含于从存储单元阵列输出的数据的错误位,当前述数据包含可订正的错误位时,将错误检测信号变成有效;输入与输出电路,当前述数据包含不可订正位时,输入与输出电路停止与前述数据一起输出的数据选通信号的时钟脉冲的至少一个。技术研发人员:藤冈伸也受保护的技术使用者:华邦电子股份有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181988.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。