存储芯片的测试方法、装置、存储介质与电子设备与流程

- 国知局

- 2024-07-31 19:16:15

所属的技术人员能够理解,本公开的各个方面可以实现为系统、方法或程序产品。因此,本公开的各个方面可以具体实现为以下形式,即:完全的硬件实施方式、完全的软件实施方式(包括固件、微代码等),或硬件和软件方面结合的实施方式,这里可以统称为“电路”、“模块”或“系统”。本公开的示例性实施方式还提供了一种计算机可读存储介质,其上存储有能够实现本说明书上述方法的程序产品。在一些可能的实施方式中,本公开的各个方面还可以实现为一种程序产品的形式,其包括程序代码,当程序产品在终端设备上运行时,程序代码用于使终端设备执行本说明书上述“示例性方法”部分中描述的根据本公开各种示例性实施方式的步骤。参考图7所示,描述了根据本公开的示例性实施方式的用于实现上述方法的程序产品700,其可以采用便携式紧凑盘只读存储器(cd-rom)并包括程序代码,并可以在终端设备,例如个人电脑上运行。然而,本公开的程序产品不限于此,在本文件中,可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。程序产品700可以采用一个或多个可读介质的任意组合。可读介质可以是可读信号介质或者可读存储介质。可读存储介质例如可以为但不限于电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。可读存储介质的更具体的例子(非穷举的列表)包括:具有一个或多个导线的电连接、便携式盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。计算机可读信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了可读程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。可读信号介质还可以是可读存储介质以外的任何可读介质,该可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、有线、光缆、rf等等,或者上述的任意合适的组合。可以以一种或多种程序设计语言的任意组合来编写用于执行本公开操作的程序代码,程序设计语言包括面向对象的程序设计语言—诸如java、c++等,还包括常规的过程式程序设计语言—诸如“c”语言或类似的程序设计语言。程序代码可以完全地在用户计算设备上执行、部分地在用户设备上执行、作为一个独立的软件包执行、部分在用户计算设备上部分在远程计算设备上执行、或者完全在远程计算设备或服务器上执行。在涉及远程计算设备的情形中,远程计算设备可以通过任意种类的网络,包括局域网(lan)或广域网(wan),连接到用户计算设备,或者,可以连接到外部计算设备(例如利用因特网服务提供商来通过因特网连接)。本公开的示例性实施方式还提供了一种能够实现上述方法的电子设备。下面参照图8来描述根据本公开的这种示例性实施方式的电子设备800。图8显示的电子设备800仅仅是一个示例,不应对本公开实施方式的功能和使用范围带来任何限制。如图8所示,电子设备800可以以通用计算设备的形式表现。电子设备800的组件可以包括但不限于:上述至少一个处理单元810、上述至少一个存储单元820、连接不同系统组件(包括存储单元820和处理单元810)的总线830和显示单元840。其中,存储单元820存储有程序代码,程序代码可以被处理单元810执行,使得处理单元810执行本说明书上述“示例性方法”部分中描述的根据本公开各种示例性实施方式的步骤。例如,处理单元810可以执行图1至图2、图4至图5所示的方法步骤等。存储单元820可以包括易失性存储单元形式的可读介质,例如随机存取存储单元(ram)821和/或高速缓存存储单元822,还可以进一步包括只读存储单元(rom)823。存储单元820还可以包括具有一组(至少一个)程序模块825的程序/实用工具824,这样的程序模块825包括但不限于:操作系统、一个或者多个应用程序、其它程序模块以及程序数据,这些示例中的每一个或某种组合中可能包括网络环境的实现。总线830可以为表示几类总线结构中的一种或多种,包括存储单元总线或者存储单元控制器、外围总线、图形加速端口、处理单元或者使用多种总线结构中的任意总线结构的局域总线。电子设备800也可以与一个或多个外部设备900(例如键盘、指向设备、蓝牙设备等)通信,还可与一个或者多个使得用户能与该电子设备800交互的设备通信,和/或与使得该电子设备800能与一个或多个其它计算设备进行通信的任何设备(例如路由器、调制解调器等等)通信。这种通信可以通过输入/输出(i/o)接口850进行。并且,电子设备800还可以通过网络适配器860与一个或者多个网络(例如局域网(lan),广域网(wan)和/或公共网络,例如因特网)通信。如图所示,网络适配器860通过总线830与电子设备800的其它模块通信。应当明白,尽管图中未示出,可以结合电子设备800使用其它硬件和/或软件模块,包括但不限于:微代码、设备驱动器、冗余处理单元、外部磁盘驱动阵列、raid系统、磁带驱动器以及数据备份存储系统等。应当注意,尽管在上文详细描述中提及了用于动作执行的设备的若干模块或者单元,但是这种划分并非强制性的。实际上,根据本公开的示例性实施方式,上文描述的两个或更多模块或者单元的特征和功能可以在一个模块或者单元中具体化。反之,上文描述的一个模块或者单元的特征和功能可以进一步划分为由多个模块或者单元来具体化。此外,上述附图仅是根据本公开示例性实施方式的方法所包括的处理的示意性说明,而不是限制目的。易于理解,上述附图所示的处理并不表明或限制这些处理的时间顺序。另外,也易于理解,这些处理可以是例如在多个模块中同步或异步执行的。通过以上的实施方式的描述,本领域的技术人员易于理解,这里描述的示例性实施方式可以通过软件实现,也可以通过软件结合必要的硬件的方式来实现。因此,根据本公开示例性实施方式的技术方案可以以软件产品的形式体现出来,该软件产品可以存储在一个非易失性存储介质(可以是cd-rom,u盘,移动硬盘等)中或网络上,包括若干指令以使得一台计算设备(可以是个人计算机、服务器、终端装置、或者网络设备等)执行根据本公开示例性实施方式的方法。本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其他实施方式。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本中的公知常识或惯用技术手段。说明书和实施方式仅被视为示例性的,本公开的真正范围和精神由权利要求指出。

背景技术:

1、存储芯片是许多电子产品的重要部件。在存储芯片的生产过程中,测试技术是检测存储芯片的产品良率和使用功能的重要环节。

2、存储芯片的测试包括多种测试类型,比如可靠性测试、环境测试、功能测试和读写测试等。其中,读写测试需要对存储芯片中的所有存储单元进行扫描测试,而随着存储芯片的存储容量的不断提升和制程工艺的复杂化,存储芯片的失效模式越来越多,如何对存储芯片进行完整和高效地测试,成为技术人员重点关注的研究内容。

3、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开提供了一种存储芯片的测试方法、存储芯片的测试装置、计算机可读存储介质与电子设备,进而至少在一定程度上改善现有技术中存储芯片的测试效率不高和完整性不强的问题。

2、本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本公开的实践而习得。

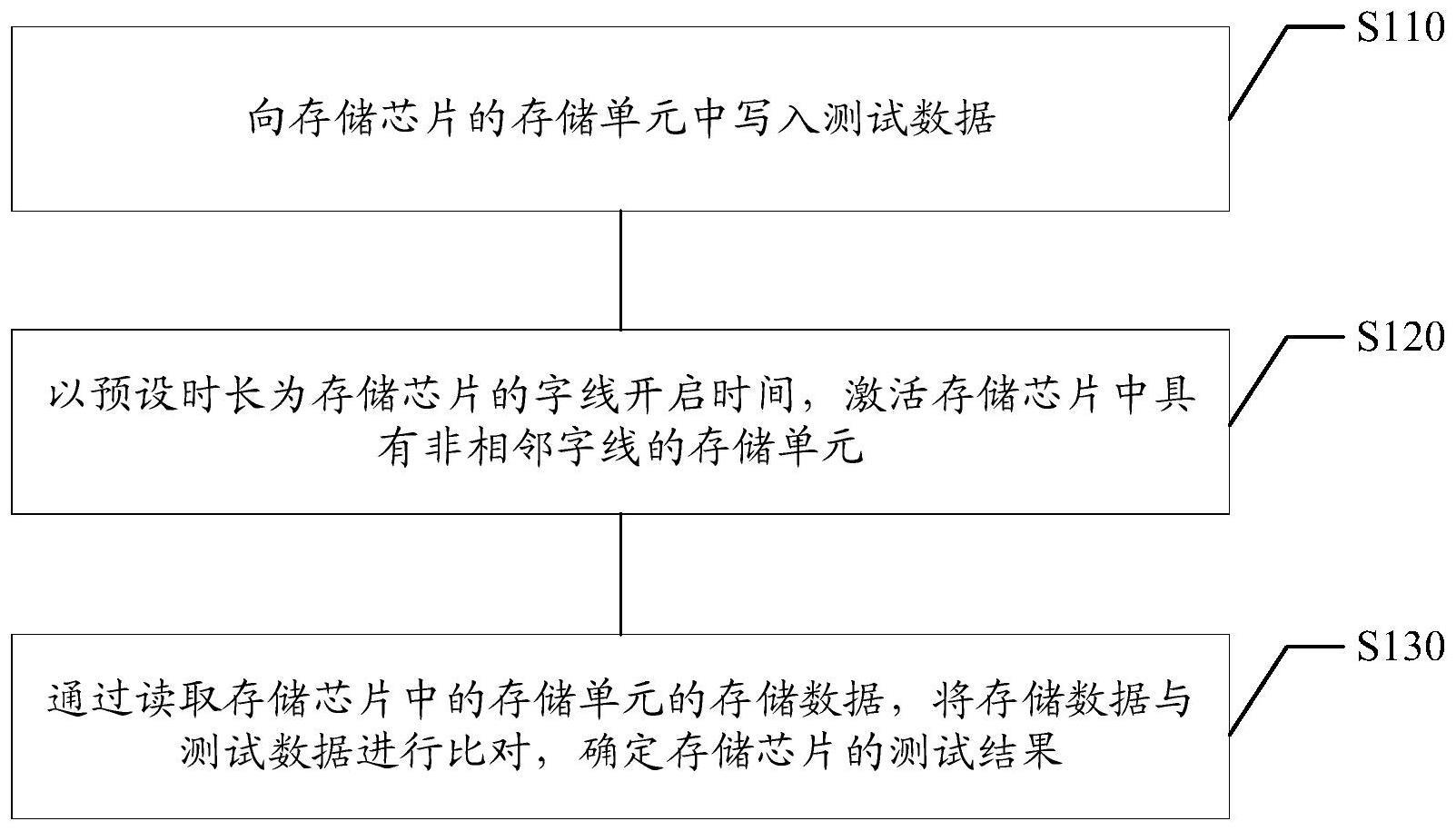

3、根据本公开的第一方面,提供一种存储芯片的测试方法,所述方法包括:向存储芯片的存储单元中写入测试数据;以预设时长为所述存储芯片的字线开启时间,激活所述存储芯片中具有非相邻字线的存储单元,所述预设时长大于所述存储芯片的标准字线开启时间,且所述预设时长通过设置tras时序参数得到;通过读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述测试数据进行比对,确定所述存储芯片的测试结果。

4、在本公开的一种示例性实施方式中,所述向存储芯片的存储单元中写入测试数据,包括:逐条向所述存储芯片的每条字线上的存储单元中写入所述测试数据,以使所述存储芯片的每条字线上的每个存储单元中写入一位二进制数据。

5、在本公开的一种示例性实施方式中,所述逐条向所述存储芯片的每条字线上的存储单元中写入所述测试数据,包括:在每次向所述存储芯片的当前字线上的存储单元中写入所述测试数据之前,开启所述当前字线;在所述当前字线上的存储单元中,按照单位突发长度向所述存储单元中写入所述测试数据,并在每次完成所述单位突发长度对应的存储单元的数据写入时,关闭所述当前字线,直至完成所述当前字线上的全部存储单元的数据写入,然后向所述存储芯片的下一字线上的存储单元写入所述测试数据。

6、在本公开的一种示例性实施方式中,所述以预设时长为所述存储芯片的字线开启时间,激活所述存储芯片中具有非相邻字线的存储单元,包括:以预设时长为所述存储芯片的字线开启时间,分别对所述存储芯片中具有偶数字线编号的存储单元和具有奇数字线编号的存储单元进行重复激活;在完成对所述具有偶数字线编号的存储单元和所述具有奇数字线编号的存储单元中的任意一种存储单元的重复激活后,读取所述存储芯片中的全部存储单元的存储数据,将所述存储数据与所述测试数据进行比对,以确定所述存储芯片的测试结果。

7、在本公开的一种示例性实施方式中,所述测试数据包括多组不同的数据拓扑,所述方法还包括:向所述存储芯片的全部存储单元中分别写入每组数据拓扑;在完成任意一组数据拓扑在所述存储芯片的存储单元中的写入后,执行激活所述存储芯片中具有非相邻字线的存储单元的步骤;读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述任意一组数据拓扑进行比对,确定所述存储芯片关于所述任意一组数据拓扑的测试结果。

8、在本公开的一种示例性实施方式中,每组数据拓扑中包括多个不同的二进制序列,在向所述存储芯片的全部存储单元中分别写入每组数据拓扑时,所述方法还包括:分别确定所述存储芯片中具有奇数字线编号和偶数字线编号的全部存储单元,得到第一存储单元和第二存储单元;将所述任意一组数据拓扑中不同的二进制序列分别写入所述第一存储单元和所述第二存储单元,以在所述存储芯片中相邻两个字线的存储单元中写入不同的二进制序列。

9、在本公开的一种示例性实施方式中,在将所述任意一组数据拓扑中不同的二进制序列分别写入所述第一存储单元和所述第二存储单元后,所述方法还包括:以预设时长为所述存储芯片的字线开启时间,分别激活所述第一存储单元或所述第二存储单元;在完成对所述第一存储单元或所述第二存储单元的激活操作时,读取所述存储芯片中的全部存储单元的存储数据,将所述存储数据与所述任意一组数据拓扑中对应的二进制序列进行比对,确定所述存储芯片的测试结果。

10、在本公开的一种示例性实施方式中,所述多组数据拓扑包括具有两种二进制序列的第一数据拓扑,在所述第一数据拓扑的每种二进制序列中,相邻数据位的数据不同。

11、在本公开的一种示例性实施方式中,所述将所述任意一组数据拓扑中不同的二进制序列分别写入所述第一存储单元和所述第二存储单元,包括:将所述第一数据拓扑中的第一种二进制序列写入所述第一存储单元,并将所述第一数据拓扑中的第二种二进制序列写入所述第二存储单元;或者将所述第一数据拓扑中的第二种二进制序列写入所述第一存储单元,并将所述第一数据拓扑中的第一种二进制序列写入所述第二存储单元。

12、在本公开的一种示例性实施方式中,所述多组数据拓扑包括具有两种二进制序列的第二数据拓扑,其中,所述两种二进制序列分别为全0序列和全1序列。

13、在本公开的一种示例性实施方式中,所述将所述任意一组数据拓扑中不同的二进制序列分别写入所述第一存储单元和所述第二存储单元,包括:将所述第二数据拓扑中的全0序列写入所述第一存储单元,并将所述第二数据拓扑中的全1序列写入所述第二存储单元;或者将所述第二数据拓扑中的全1序列写入所述第一存储单元,并将所述第二数据拓扑中的全0序列写入所述第二存储单元。

14、在本公开的一种示例性实施方式中,所述方法还包括:当所述第一存储单元和所述第二存储单元中写入的二进制序列均被更新时,以预设时长为所述存储芯片的字线开启时间,分别激活所述第一存储单元或所述第二存储单元;在完成对所述第一存储单元或所述第二存储单元的激活后,读取所述存储芯片中的全部存储单元的存储数据,将所述存储数据与对应的数据拓扑中的二进制序列进行比对,确定所述存储芯片的测试结果。

15、在本公开的一种示例性实施方式中,所述通过读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述测试数据进行比对,确定所述存储芯片的测试结果,包括:读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述测试数据进行逐位比对,确定所述存储芯片中的各个存储单元是否发生读写错误以及发生读写错误的位数,以得到所述测试结果。

16、在本公开的一种示例性实施方式中,所述读取所述存储芯片中的存储单元的存储数据,包括:在每次读取所述存储芯片的当前字线上的存储单元的存储数据之前,开启所述当前字线;在所述当前字线上的存储单元中,按照所述单位突发长度读取存储单元中的存储数据,并在每次完成所述单位突发长度对应的存储单元的数据读取时,关闭所述当前字线,直至完成所述当前字线上的全部存储单元的数据读取,然后读取所述存储芯片的下一字线上的存储单元的存储数据。

17、在本公开的一种示例性实施方式中,在以预设时长为所述存储芯片的字线开启时间,激活所述存储芯片中具有非相邻字线的存储单元时,所述方法还包括:降低所述存储芯片的字线关闭电压,以增强所述存储芯片中相邻字线的存储单元之间的gidl效应。

18、在本公开的一种示例性实施方式中,在向存储芯片的存储单元中写入测试数据后,所述方法还包括:按照预设刷新周期对所述存储芯片的存储单元进行刷新处理。

19、根据本公开的第二方面,提供一种存储芯片的测试装置,所述装置包括:写入模块,用于向存储芯片的存储单元中写入测试数据;激活模块,用于以预设时长为所述存储芯片的字线开启时间,激活所述存储芯片中具有非相邻字线的存储单元,所述预设时长大于所述存储芯片的标准字线开启时间,且所述预设时长通过设置tras时序参数得到;比对模块,用于通过读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述测试数据进行比对,确定所述存储芯片的测试结果。

20、在本公开的一种示例性实施方式中,所述写入模块用于逐条向所述存储芯片的每条字线上的存储单元中写入所述测试数据,以使所述存储芯片的每条字线上的每个存储单元中写入一位二进制数据。

21、在本公开的一种示例性实施方式中,所述写入模块还用于在每次向所述存储芯片的当前字线上的存储单元中写入所述测试数据之前,开启所述当前字线,在所述当前字线上的存储单元中,按照单位突发长度向所述存储单元中写入所述测试数据,并在每次完成所述单位突发长度对应的存储单元的数据写入时,关闭所述当前字线,直至完成所述当前字线上的全部存储单元的数据写入,然后向所述存储芯片的下一字线上的存储单元写入所述测试数据。

22、在本公开的一种示例性实施方式中,所述激活模块用于以预设时长为所述存储芯片的字线开启时间,分别对所述存储芯片中具有偶数字线编号的存储单元和具有奇数字线编号的存储单元进行重复激活,在完成对所述具有偶数字线编号的存储单元和所述具有奇数字线编号的存储单元中的任意一种存储单元的重复激活后,所述比对模块用于读取所述存储芯片中的全部存储单元的存储数据,将所述存储数据与所述测试数据进行比对,以确定所述存储芯片的测试结果。

23、在本公开的一种示例性实施方式中,所述测试数据包括多组不同的数据拓扑,所述写入模块用于向所述存储芯片的全部存储单元中分别写入每组数据拓扑;所述激活模块用于在完成任意一组数据拓扑在所述存储芯片的存储单元中的写入后,执行激活所述存储芯片中具有非相邻字线的存储单元的步骤;所述比对模块用于读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述任意一组数据拓扑进行比对,确定所述存储芯片关于所述任意一组数据拓扑的测试结果。

24、在本公开的一种示例性实施方式中,每组数据拓扑中包括多个不同的二进制序列,在向所述存储芯片的全部存储单元中分别写入每组数据拓扑时,所述写入模块还用于分别确定所述存储芯片中具有奇数字线编号和偶数字线编号的全部存储单元,得到第一存储单元和第二存储单元,将所述任意一组数据拓扑中不同的二进制序列分别写入所述第一存储单元和所述第二存储单元,以在所述存储芯片中相邻两个字线的存储单元中写入不同的二进制序列。

25、在本公开的一种示例性实施方式中,在将所述任意一组数据拓扑中不同的二进制序列分别写入所述第一存储单元和所述第二存储单元后,所述激活模块还用于以预设时长为所述存储芯片的字线开启时间,分别激活所述第一存储单元或所述第二存储单元;在完成对所述第一存储单元或所述第二存储单元的激活操作时,所述比对模块还用于读取所述存储芯片中的全部存储单元的存储数据,将所述存储数据与所述任意一组数据拓扑中对应的二进制序列进行比对,确定所述存储芯片的测试结果。

26、在本公开的一种示例性实施方式中,所述多组数据拓扑包括具有两种二进制序列的第一数据拓扑,在所述第一数据拓扑的每种二进制序列中,相邻数据位的数据不同。

27、在本公开的一种示例性实施方式中,所述写入模块还用于将所述第一数据拓扑中的第一种二进制序列写入所述第一存储单元,并将所述第一数据拓扑中的第二种二进制序列写入所述第二存储单元,或者将所述第一数据拓扑中的第二种二进制序列写入所述第一存储单元,并将所述第一数据拓扑中的第一种二进制序列写入所述第二存储单元。

28、在本公开的一种示例性实施方式中,所述多组数据拓扑包括具有两种二进制序列的第二数据拓扑,其中,所述两种二进制序列分别为全0序列和全1序列。

29、在本公开的一种示例性实施方式中,所述写入模块还用于将所述第二数据拓扑中的全0序列写入所述第一存储单元,并将所述第二数据拓扑中的全1序列写入所述第二存储单元,或者将所述第二数据拓扑中的全1序列写入所述第一存储单元,并将所述第二数据拓扑中的全0序列写入所述第二存储单元。

30、在本公开的一种示例性实施方式中,所述激活模块还用于当所述第一存储单元和所述第二存储单元中写入的二进制序列均被更新时,以预设时长为所述存储芯片的字线开启时间,分别激活所述第一存储单元或所述第二存储单元;所述比对模块还用于在完成对所述第一存储单元或所述第二存储单元的激活后,读取所述存储芯片中的全部存储单元的存储数据,将所述存储数据与对应的数据拓扑中的二进制序列进行比对,确定所述存储芯片的测试结果。

31、在本公开的一种示例性实施方式中,所述比对模块还用于读取所述存储芯片中的存储单元的存储数据,将所述存储数据与所述测试数据进行逐位比对,确定所述存储芯片中的各个存储单元是否发生读写错误以及发生读写错误的位数,以得到所述测试结果。

32、在本公开的一种示例性实施方式中,所述比对模块还用于在每次读取所述存储芯片的当前字线上的存储单元的存储数据之前,开启所述当前字线,在所述当前字线上的存储单元中,按照所述单位突发长度读取存储单元中的存储数据,并在每次完成所述单位突发长度对应的存储单元的数据读取时,关闭所述当前字线,直至完成所述当前字线上的全部存储单元的数据读取,然后读取所述存储芯片的下一字线上的存储单元的存储数据。

33、在本公开的一种示例性实施方式中,在以预设时长为所述存储芯片的字线开启时间,激活所述存储芯片中具有非相邻字线的存储单元时,所述激活模块还用于降低所述存储芯片的字线关闭电压,以增强所述存储芯片中相邻字线的存储单元之间的gidl效应。

34、在本公开的一种示例性实施方式中,在向存储芯片的存储单元中写入测试数据后,所述激活模块还用于按照预设刷新周期对所述存储芯片的存储单元进行刷新处理。

35、根据本公开的第三方面,提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上述任意一种存储芯片的测试方法。

36、根据本公开的第四方面,提供一种电子设备,包括:处理器;以及存储器,用于存储所述处理器的可执行指令;其中,所述处理器配置为经由执行所述可执行指令来执行上述任意一种存储芯片的测试方法。

37、本公开具有以下有益效果:

38、综上,根据本示例性实施方式中的存储芯片的测试方法、存储芯片的测试装置、计算机可读存储介质和电子设备,可以向存储芯片的存储单元中写入测试数据,以预设时长为存储芯片的字线开启时间,激活存储芯片中具有非相邻字线的存储单元,通过读取存储芯片中的存储单元的存储数据,将存储数据与测试数据进行比对,确定存储芯片的测试结果。其中,预设时长大于存储芯片的标准字线开启时间,且预设时长通过设置tras时序参数得到。一方面,本方案通过读取存储芯片中的存储单元的存储数据,将存储数据与测试数据进行比对,可以确定存储芯片的测试结果,完成对存储芯片的读写性能测试;另一方面,通过以预设时长为存储芯片的字线开启时间,激活存储芯片中具有非相邻字线的存储单元,可以实现非相邻字线的存储单元的长时间激活,可以增加行泄露产生的几率,使得行泄露的问题能够尽快显现,因而可以提高存储芯片的测试效率。

39、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182095.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表