非易失性存储器装置和设置其兼容性的方法与流程

- 国知局

- 2024-07-31 19:38:43

在此描述的本公开的实施例涉及一种半导体存储器装置,并且更具体地,涉及一种提供输入/输出兼容性的非易失性存储器装置及用于设置其兼容性的方法。

背景技术:

1、近年来,各种移动装置或电子装置(诸如,智能电话、台式计算机、膝上型计算机、平板pc和可穿戴装置)已经被广泛使用。这些电子装置通常包括用于存储数据的存储装置。具体地,根据提高电子装置的容量和速度的趋势,已经作出许多努力来提高存储装置的容量和速度。

2、作为非易失性存储器的闪存装置用作从移动装置到计算机系统的各种领域中的存储设备。随着技术的发展和对性能改进的需求,闪存装置的数据输入/输出速度迅速提高。具体地,垂直堆叠nand闪存(v-nand闪存)具有随着世代进步而迅速提高输入/输出速度的趋势。

3、负责nand闪存的输入/输出的输入/输出电路已经应用了数据信号dq和选通信号dqs的延迟被预设的匹配(matched)型结构。然而,随着输入/输出速度提高,输入/输出电路可被要求采用适合于高速输入/输出的不匹配(unmatched)型结构。不匹配输入/输出电路中的数据信号dq和选通信号dqs的对齐可通过在启动序列期间执行的训练来实现。

4、当不匹配输入/输出电路被使用时,数据信号dq可通过最短的路径到达采样器(或锁存器)。因此,通过不匹配输入/输出电路将数据信号dq的抖动最小化并且应用能够立即补偿符号间干扰isi的滤波器是可行的。因此,不匹配输入/输出电路适合于高速输入/输出操作。

5、随着闪存装置中的输入/输出速度提高,不匹配输入/输出电路可以是必要的。然而,即使输入/输出电路以适合于高速操作的不匹配类型来实现,它也可需要能够被使用传统协议的主机或存储器控制器使用。对能够提供这样的兼容性的闪存装置的需求正在迅速增加。

技术实现思路

1、本公开的实施例提供具有输入/输出兼容性的非易失性存储器装置及用于设置其兼容性的方法。

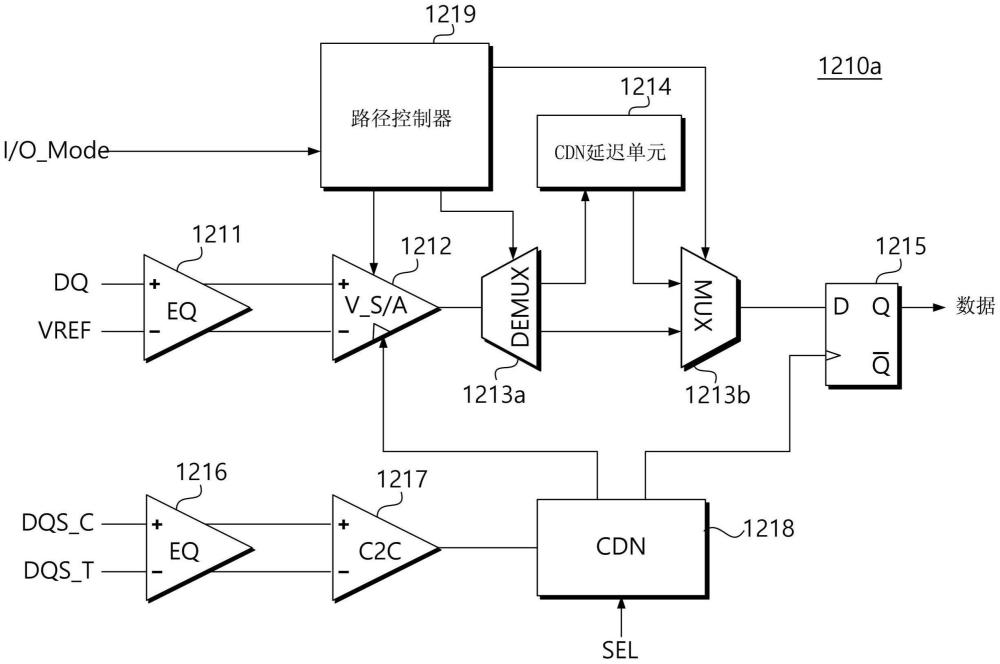

2、根据发明构思的实施例,一种被配置为从外部源接收数据信号和数据选通信号的非易失性存储器装置可包括:可变采样器,被配置为响应于控制信号,在放大器模式或采样器模式下对数据信号进行处理;选择电路,被配置为响应于控制信号,经由延迟单元将从可变采样器输出的数据信号发送到触发器,或者经由将延迟单元旁路的路径将从可变采样器输出的数据信号发送到触发器;转换器,被配置为对数据选通信号进行放大;时钟分配网络,被配置为响应于控制信号,将由转换器放大的数据选通信号发送到可变采样器,或者将放大后的数据选通信号延迟预定时间并且将放大后的数据选通信号发送到触发器;以及路径控制器,被配置为根据输入/输出模式生成控制信号。

3、根据发明构思的另一实施例,一种非易失性存储器装置可包括:兼容输入/输出电路,被配置为通过根据输入/输出模式将数据信号的路径和数据选通信号的路径设置为匹配模式或不匹配模式来使数据信号的延迟和数据选通信号对齐,使得采样的数据信号从兼容输入/输出电路被输出;以及存储器核,包括存储器单元,存储器单元用于存储从兼容输入/输出电路输出的采样的数据信号,其中,在不匹配模式下,数据信号和数据选通信号通过训练操作被对齐。

4、根据发明构思的实施例,一种设置非易失性存储器装置的兼容性的方法可包括:从所述非易失性存储器装置外部的源接收数据信号和数据选通信号的输入/输出模式;根据接收的输入/输出模式,将所述非易失性存储器装置的输入/输出电路中的数据信号和数据选通信号的路径设置为匹配类型或不匹配类型;以及当输入/输出电路被设置为不匹配类型时,执行训练操作以使数据信号与数据选通信号对齐。

技术特征:1.一种非易失性存储器装置,所述非易失性存储器装置被配置为从外部源接收数据信号和数据选通信号,所述非易失性存储器装置包括:

2.根据权利要求1所述的非易失性存储器装置,其中,路径控制器被配置为:当输入/输出模式为匹配模式时,生成与可变采样器在放大器模式下进行操作并且选择电路经由延迟单元将数据信号发送到触发器对应的控制信号。

3.根据权利要求2所述的非易失性存储器装置,其中,路径控制器被配置为:当输入/输出模式为匹配模式时,生成与时钟分配网络将放大后的数据选通信号发送到触发器对应的控制信号。

4.根据权利要求3所述的非易失性存储器装置,其中,延迟单元被配置为:基于放大后的数据选通信号被配置为由时钟分配网络延迟的预定时间来延迟数据信号。

5.根据权利要求1所述的非易失性存储器装置,其中,路径控制器被配置为:当输入/输出模式为不匹配模式时,生成与可变采样器在采样器模式下进行操作并且选择电路经由将延迟单元旁路的路径发送数据信号对应的控制信号。

6.根据权利要求5所述的非易失性存储器装置,其中,路径控制器被配置为:当输入/输出模式为不匹配模式时,生成与时钟分配网络将放大后的数据选通信号发送到可变采样器对应的控制信号。

7.根据权利要求1至6中任一项所述的非易失性存储器装置,其中,选择电路包括:

8.根据权利要求1至6中任一项所述的非易失性存储器装置,其中,可变采样器包括双尾锁存器或强臂锁存器。

9.根据权利要求1至6中任一项所述的非易失性存储器装置,还包括:

10.一种非易失性存储器装置,包括:

11.根据权利要求10所述的非易失性存储器装置,其中,兼容输入/输出电路包括:

12.根据权利要求11所述的非易失性存储器装置,其中,可变采样器被配置为:响应于控制信号,在匹配模式下在放大器模式下进行操作,并且在不匹配模式下在采样器模式下进行操作。

13.根据权利要求12所述的非易失性存储器装置,其中,可变采样器被配置为:在匹配模式下与c2c转换器同步。

14.根据权利要求11所述的非易失性存储器装置,其中,延迟单元被配置为:在匹配模式下,根据在时钟分配网络中发生的预定时间延迟的延迟量来延迟数据信号。

15.根据权利要求11所述的非易失性存储器装置,还包括:

16.根据权利要求15所述的非易失性存储器装置,其中,第一均衡器或第二均衡器包括判决反馈均衡器。

17.根据权利要求10至16中任一项所述的非易失性存储器装置,其中,兼容输入/输出电路被配置为在被设置为不匹配模式之后执行训练操作,并且其中,训练操作包括数据信号的训练或者数据选通信号的训练。

18.根据权利要求10至16中任一项所述的非易失性存储器装置,还包括:

19.根据权利要求18所述的非易失性存储器装置,其中,内部训练单元包括:振荡器,被配置为生成用于训练操作的时钟信号。

20.一种设置非易失性存储器装置的兼容性的方法,包括:

技术总结提供非易失性存储器装置和设置其兼容性的方法。所述非易失性存储器装置可包括:可变采样器,被配置为响应于控制信号,在放大器模式或采样器模式下对数据信号进行处理;选择电路,被配置为响应于控制信号,经由延迟单元将从可变采样器输出的数据信号发送到触发器,或者经由将延迟单元旁路的路径将从可变采样器输出的数据信号发送到触发器;转换器,被配置为对数据选通信号进行放大;时钟分配网络,被配置为响应于控制信号,将由转换器放大的数据选通信号发送到可变采样器,或者将放大后的数据选通信号延迟预定时间并且将放大后的数据选通信号发送到触发器;以及路径控制器,被配置为根据输入/输出模式生成控制信号。技术研发人员:尹镐俊,朴胜振,李斗馥,李斘勋,林伯镇,崔荣暾,崔桢焕受保护的技术使用者:三星电子株式会社技术研发日:技术公布日:2024/2/19本文地址:https://www.jishuxx.com/zhuanli/20240731/183383.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

存储卡测试装置的制作方法

下一篇

返回列表