内存引脚状态的检测方法及装置与流程

- 国知局

- 2024-07-31 19:42:27

本技术实施例涉及计算机领域,具体而言,涉及一种内存引脚状态的检测方法及装置。

背景技术:

1、内存信号种类繁多且重要,一旦信号时序或信号质量不佳,就会对整个系统造成严重影响,所以开机前需要通过bios(basic input/output system,基本输入/输出系统)的mrc(memory reference code,内存参考代码)进行内存训练(memory training),用于初始化内存控制器并对内存信号进行校准以优化读/写时序和电压以获得最佳表现。mrc的目标是以尽可能高效的方式启动内存,快速找到时序和电压的“最佳点”,以便内存启动并运行,并使计算机系统可以继续引导该内存。

2、mrc在初始化过程中,cpu(central processing unit,中央处理器)通过控制各个信号线,发出不同的命令给到内存做初始化动作。以ddr5(double data rate 5,第五代双倍数据率内存)为例,ddr5内存当前一共有288个引脚,定义了不同信号,其中数据相关dq信号占比62.5%,接到主板内存插槽中后,由于该信号引脚众多,占比最高,是最容易出现接触不良,断路的部件之一。然而,在目前的内存训练过程中,在一系列串行动作的后期才会开始进行dq信号引脚的检测。

3、由此可见,相关技术中的内存引脚状态的检测方法存在dq信号引脚的检测时间长的问题。

技术实现思路

1、本技术实施例提供了一种内存引脚状态的检测方法及装置,以至少解决相关技术中的内存引脚状态的检测方法存在dq信号引脚的检测时间长的问题。

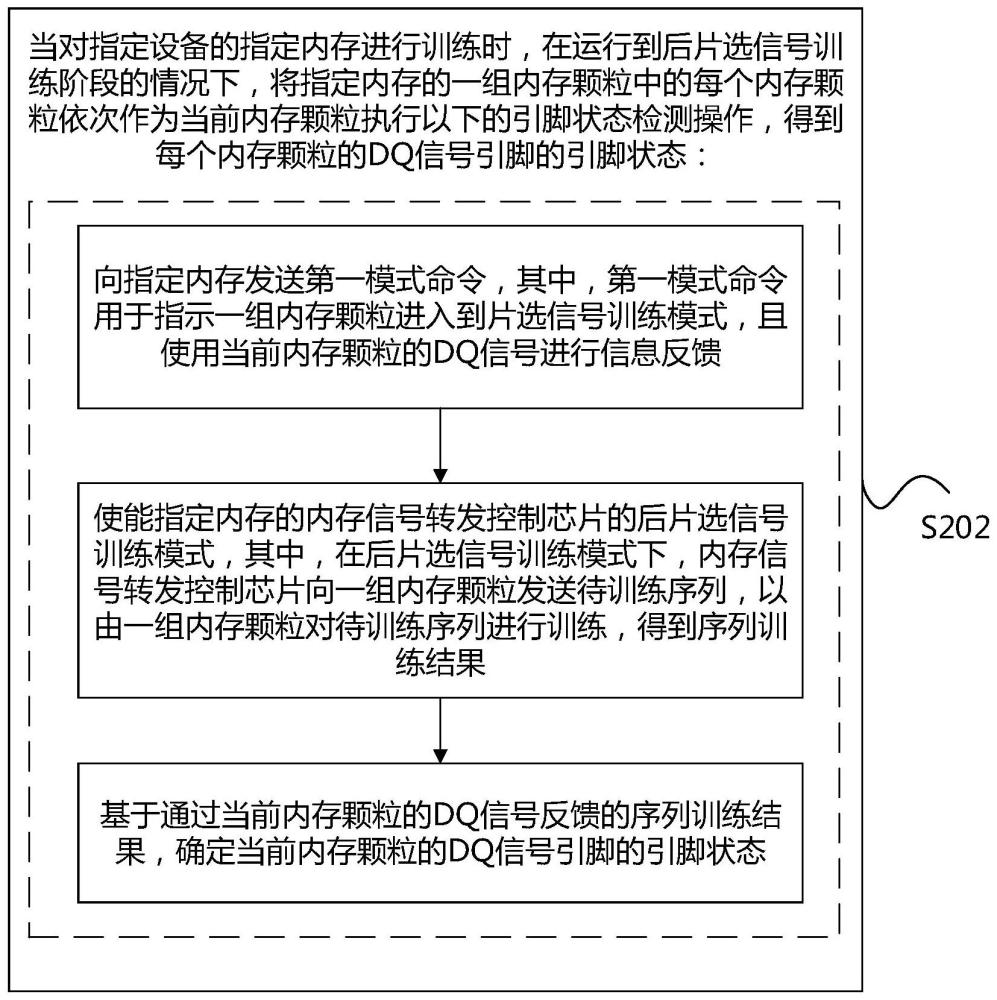

2、根据本技术的一个实施例,提供了一种内存引脚状态的检测方法,包括:当对指定设备的指定内存进行训练时,在运行到后片选信号训练阶段的情况下,将所述指定内存的一组内存颗粒中的每个内存颗粒依次作为当前内存颗粒执行以下的引脚状态检测操作,得到所述每个内存颗粒的dq信号引脚的引脚状态:向所述指定内存发送第一模式命令,其中,所述第一模式命令用于指示所述一组内存颗粒进入到片选信号训练模式,且使用所述当前内存颗粒的dq信号进行信息反馈;使能所述指定内存的内存信号转发控制芯片的后片选信号训练模式,其中,在所述后片选信号训练模式下,所述内存信号转发控制芯片向所述一组内存颗粒发送待训练序列,以由所述一组内存颗粒对所述待训练序列进行训练,得到序列训练结果;基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态。

3、在一个示例性实施例中,所述基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态,包括:在使能所述内存信号转发控制芯片的所述后片选信号训练模式之后的指定时间段内检测到所述当前内存颗粒的所述dq信号的信号值由默认值转变为指定值的情况下,确定所述当前内存颗粒的所述dq信号引脚处于正常状态;在使能所述内存信号转发控制芯片的所述后片选信号训练模式之后的指定时间段内检测到所述当前内存颗粒的所述dq信号的信号值保持默认值的情况下,确定所述当前内存颗粒的所述dq信号引脚处于异常状态。

4、在一个示例性实施例中,在所述向所述指定内存发送第一模式命令之前,所述方法还包括:使能所述内存信号转发控制芯片的地址信号直通模式,其中,所述第一模式命令是在所述地址信号直通模式下,由所述内存信号转发控制芯片向所述一组内存颗粒发送的;在所述向所述指定内存发送第一模式命令之后,所述方法还包括:关闭所述内存信号转发控制芯片的所述地址信号直通模式。

5、在一个示例性实施例中,在所述基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态之后,所述方法还包括:关闭所述内存信号转发控制芯片的所述后片选信号训练模式;向所述指定内存发送第二模式命令,其中,所述第二模式命令用于指示所述一组内存颗粒退出所述片选信号训练模式。

6、在一个示例性实施例中,在所述向所述指定内存发送第二模式命令之前,所述方法还包括:使能所述内存信号转发控制芯片的地址信号直通模式,其中,所述第二模式命令是在所述地址信号直通模式下,由所述内存信号转发控制芯片向所述一组内存颗粒发送的;在所述向所述指定内存发送第二模式命令之后,所述方法还包括:关闭所述内存信号转发控制芯片的所述地址信号直通模式。

7、在一个示例性实施例中,所述指定内存的训练过程包含多个训练阶段;在所述将所述指定内存的一组内存颗粒中的每个内存颗粒依次作为当前内存颗粒执行以下的引脚状态检测操作之后,所述方法还包括:根据所述每个内存颗粒的所述dq信号引脚的引脚状态,从所述一组内存颗粒中选取出所述dq信号引脚处于正常状态的内存颗粒,得到更新的所述一组内存颗粒;使用更新的所述一组内存颗粒,执行所述多个训练阶段中位于所述后片选信号训练阶段之后的各个训练阶段的训练步骤;其中,所述多个训练阶段包含位于所述后片选信号训练阶段之后的读dq/dqs训练阶段,在所述读dq/dqs训练阶段,仅执行读dqs训练的步骤。

8、在一个示例性实施例中,所述当前内存颗粒包含多个所述dq信号引脚;在所述当前内存颗粒的所述dq信号引脚的所述dq信号的信号值为默认值时,表示未通过所述当前内存颗粒的所述dq信号引脚的所述dq信号的反馈信息,在所述当前内存颗粒的所述dq信号引脚的所述dq信号的信号值由默认值转变为指定值时,表示通过所述当前内存颗粒的所述dq信号引脚的所述dq信号的反馈信息;所述向所述指定内存发送第一模式命令,包括:向所述指定内存发送所述第一模式命令,其中,所述第一模式命令用于指示所述一组内存颗粒进入到片选信号训练模式,且使用所述当前内存颗粒的多个所述dq信号引脚中的指定dq信号引脚的所述dq信号进行信息反馈;所述基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态,包括:基于所述当前内存颗粒的所述指定dq信号引脚的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的多个所述dq信号引脚的引脚状态;或者,

9、所述向所述指定内存发送第一模式命令,包括:向所述指定内存发送所述第一模式命令,其中,所述第一模式命令用于指示所述一组内存颗粒进入到片选信号训练模式,且使用所述当前内存颗粒的多个所述dq信号引脚的所述dq信号进行信息反馈;所述基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态,包括:基于所述当前内存颗粒的多个所述dq信号引脚的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的多个所述dq信号引脚的引脚状态,其中,通过所述当前内存颗粒的多个所述dq信号引脚的所述dq信号所反馈的信息为对所述当前内存颗粒的多个所述dq信号引脚的所述dq信号进行和运算之后所得到的结果。

10、根据本技术的另一个实施例,提供了一种内存引脚状态的检测装置,包括:第一执行单元,用于当对指定设备的指定内存进行训练时,在运行到后片选信号训练阶段的情况下,将所述指定内存的一组内存颗粒中的每个内存颗粒依次作为当前内存颗粒执行以下的引脚状态检测操作,得到所述每个内存颗粒的dq信号引脚的引脚状态:向所述指定内存发送第一模式命令,其中,所述第一模式命令用于指示所述一组内存颗粒进入到片选信号训练模式,且使用所述当前内存颗粒的dq信号进行信息反馈;使能所述指定内存的内存信号转发控制芯片的后片选信号训练模式,其中,在所述后片选信号训练模式下,所述内存信号转发控制芯片向所述一组内存颗粒发送待训练序列,以由所述一组内存颗粒对所述待训练序列进行训练,得到序列训练结果;基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态。

11、在一个示例性实施例中,所述第一执行单元包括:第一确定模块,用于在使能所述内存信号转发控制芯片的所述后片选信号训练模式之后的指定时间段内检测到所述当前内存颗粒的所述dq信号的信号值由默认值转变为指定值的情况下,确定所述当前内存颗粒的所述dq信号引脚处于正常状态;第二确定模块,用于在使能所述内存信号转发控制芯片的所述后片选信号训练模式之后的指定时间段内检测到所述当前内存颗粒的所述dq信号的信号值保持默认值的情况下,确定所述当前内存颗粒的所述dq信号引脚处于异常状态。

12、在一个示例性实施例中,所述装置还包括:第一使能单元,用于在所述向所述指定内存发送第一模式命令之前,使能所述内存信号转发控制芯片的地址信号直通模式,其中,所述第一模式命令是在所述地址信号直通模式下,由所述内存信号转发控制芯片向所述一组内存颗粒发送的;所述装置还包括:第一关闭单元,用于在所述向所述指定内存发送第一模式命令之后,关闭所述内存信号转发控制芯片的所述地址信号直通模式。

13、在一个示例性实施例中,所述装置还包括:第二关闭单元,用于在所述基于所述当前内存颗粒的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的所述dq信号引脚的引脚状态之后,关闭所述内存信号转发控制芯片的所述后片选信号训练模式;发送单元,用于向所述指定内存发送第二模式命令,其中,所述第二模式命令用于指示所述一组内存颗粒退出所述片选信号训练模式。

14、在一个示例性实施例中,所述装置还包括:第二使能单元,用于在所述向所述指定内存发送第二模式命令之前,使能所述内存信号转发控制芯片的地址信号直通模式,其中,所述第二模式命令是在所述地址信号直通模式下,由所述内存信号转发控制芯片向所述一组内存颗粒发送的;所述装置还包括:第三关闭单元,用于在所述向所述指定内存发送第二模式命令之后,关闭所述内存信号转发控制芯片的所述地址信号直通模式。

15、在一个示例性实施例中,所述指定内存的训练过程包含多个训练阶段;所述装置还包括:选取单元,用于在所述将所述指定内存的一组内存颗粒中的每个内存颗粒依次作为当前内存颗粒执行以下的引脚状态检测操作之后,根据所述每个内存颗粒的所述dq信号引脚的引脚状态,从所述一组内存颗粒中选取出所述dq信号引脚处于正常状态的内存颗粒,得到更新的所述一组内存颗粒;第二执行单元,用于使用更新的所述一组内存颗粒,执行所述多个训练阶段中位于所述后片选信号训练阶段之后的各个训练阶段的训练步骤;其中,所述多个训练阶段包含位于所述后片选信号训练阶段之后的读dq/dqs训练阶段,在所述读dq/dqs训练阶段,仅执行读dqs训练的步骤。

16、在一个示例性实施例中,所述当前内存颗粒包含多个所述dq信号引脚;在所述当前内存颗粒的所述dq信号引脚的所述dq信号的信号值为默认值时,表示未通过所述当前内存颗粒的所述dq信号引脚的所述dq信号的反馈信息,在所述当前内存颗粒的所述dq信号引脚的所述dq信号的信号值由默认值转变为指定值时,表示通过所述当前内存颗粒的所述dq信号引脚的所述dq信号的反馈信息;所述第一执行单元包括:第一发送模块,用于向所述指定内存发送所述第一模式命令,其中,所述第一模式命令用于指示所述一组内存颗粒进入到片选信号训练模式,且使用所述当前内存颗粒的多个所述dq信号引脚中的指定dq信号引脚的所述dq信号进行信息反馈;所述第一执行单元包括:第三确定模块,用于基于所述当前内存颗粒的所述指定dq信号引脚的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的多个所述dq信号引脚的引脚状态;或者,

17、所述第一执行单元包括:第二发送模块,用于向所述指定内存发送所述第一模式命令,其中,所述第一模式命令用于指示所述一组内存颗粒进入到片选信号训练模式,且使用所述当前内存颗粒的多个所述dq信号引脚的所述dq信号进行信息反馈;所述第一执行单元包括:第四确定模块,用于基于所述当前内存颗粒的多个所述dq信号引脚的所述dq信号反馈的所述序列训练结果,确定所述当前内存颗粒的多个所述dq信号引脚的引脚状态,其中,通过所述当前内存颗粒的多个所述dq信号引脚的所述dq信号所反馈的信息为对所述当前内存颗粒的多个所述dq信号引脚的所述dq信号进行和运算之后所得到的结果。

18、根据本技术的又一个实施例,还提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

19、根据本技术的又一个实施例,还提供了一种电子设备,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

20、通过本技术,在进行内存训练的过程中,将原本一系列内存训练的串行步骤中对dq信号进行检测的过程前置到后片选信号训练阶段,通过预设指定内存颗粒的指定dq信号进行信息反馈,在后片选信号训练模式下,通过指定内存颗粒的指定dq信号反馈的序列训练结果,确定指定内存颗粒的dq信号引脚的引脚状态,由于提前了一系列内存训练的串行步骤中对dq信号引脚的检测,因此,可以解决相关技术中的内存引脚状态的检测方法存在dq信号引脚的检测时间长的问题,达到缩短dq信号引脚的检测时长的效果。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183610.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表