芯片测试电路及存储器的制作方法

- 国知局

- 2024-07-31 19:44:14

本技术涉及存储器技术,尤其涉及一种芯片测试电路及存储器。

背景技术:

1、伴随存储器技术的发展,存储器被广泛应用在多种领域,比如,动态随机存取存储器(dynamic random access memory,简称dram)的使用非常广泛。

2、实际应用中,为了保证存储器的正常工作,通常需要对存储器进行信号测试。比如,为了改善片选(chip select,简称cs)信号引脚的时间裕度,进行片选测试(cstraining),也称cs训练。因此,需要提供一种方案来实现cs测试。

技术实现思路

1、本技术的实施例提供一种芯片测试电路及存储器。

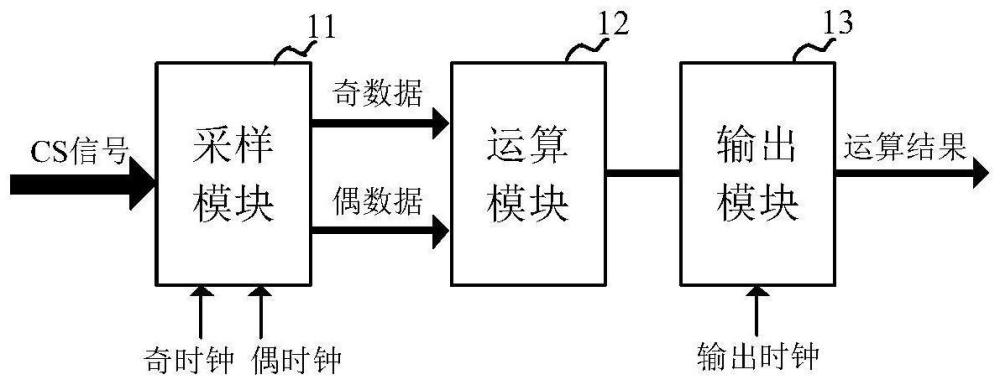

2、根据一些实施例,本技术第一方面提供一种芯片测试电路,包括:采样模块,用于基于采样时钟对连续的多个片选信号进行采样,片选信号的每一数据位的保持时长等于系统时钟的周期,采样时钟包含相位相反的奇时钟和偶时钟,奇时钟和偶时钟的周期等于系统时钟的周期的两倍,记基于奇时钟采样得到的数据为奇数据,记基于偶时钟采样得到的数据为偶数据;运算模块,与采样模块连接,用于基于奇数据和偶数据进行对比运算,获得运算结果;输出模块,与运算模块连接,用于在输出时钟处于第一状态时,实时获取运算结果,以及用于在输出时钟处于第二状态时,锁存当前的运算结果以及停止获取新的运算结果并输出锁存的运算结果,第一状态和第二状态互为反相,输出时钟的周期为单个片选信号的长度,输出时钟的上升沿与最先采样到片选信号的采样时钟的上升沿对齐。

3、在一些实施例中,每个片选信号包括四个数据位。

4、在一些实施例中,运算模块包括:第一延迟单元、第二延迟单元、第一运算单元和第二运算单元;第一延迟单元,与采样模块连接,用于将奇数据按照预定的时间间隔依次延时输出,得到第一延迟奇数据、第二延迟奇数据、第三延迟奇数据和第四延迟奇数据;第二延迟单元,与采样模块连接,用于将偶数据按照时间间隔依次延时输出,得到第一延迟偶数据、第二延迟偶数据、第三延迟偶数据和第四延迟偶数据;第一运算单元的输入端与第一延迟单元和第二延迟单元连接,第一运算单元用于接收第一延迟偶数据、第二延迟奇数据、第三延迟偶数据和第四延迟奇数据,并对比第一延迟偶数据和第二延迟奇数据,以及对比第三延迟偶数据和第四延迟奇数据;第一运算单元的输出端与输出模块连接;第二运算单元的输入端与第一延迟单元和第二延迟单元连接,第二运算单元用于接收第一延迟奇数据、第二延迟偶数据、第三延迟奇数据和第四延迟偶数据,并对比第一延迟奇数据和第二延迟偶数据,以及对比第三延迟奇数据和第四延迟偶数据;第二运算单元的输出端与输出模块连接。

5、在一些实施例中,第一运算单元包括:第一非门和第二非门、第一与非门和第二与非门、以及第一或非门;第一非门的输入端接收第一延迟偶数据,第一非门的输出端与第一与非门的第一输入端连接;第一与非门的第二输入端接收第二延迟奇数据,第一与非门的输出端与第一或非门的第一输入端连接;第二非门的输入端接收第三延迟偶数据,第二非门的输出端与第二与非门的第一输入端连接;第二与非门的第二输入端接收第四延迟奇数据,第二与非门的输出端与第一或非门的第二输入端连接;第一或非门的输出端与输出模块连接;第二运算单元包括:第三非门和第四非门、第三与非门和第四与非门、以及第二或非门;第三非门的输入端接收第一延迟奇数据,第三非门的输出端与第三与非门的第一输入端连接;第三与非门的第二输入端接收第二延迟偶数据,第三与非门的输出端与第二或非门的第一输入端连接;第四非门的输入端接收第三延迟奇数据,第四非门的输出端与第四与非门的第一输入端连接;第四与非门的第二输入端接收第四延迟偶数据,第四与非门的输出端与第二或非门的第二输入端连接;第二或非门的输出端与输出模块连接。

6、在一些实施例中,第一延迟单元包括:多个串联的第一延迟子单元;首个第一延迟子单元的输入端与采样模块连接,用于接收基于奇数据生成的第一延迟奇数据;每个第一延迟子单元的输入端与前一第一延迟子单元的输出端连接,每个第一延迟子单元用于将接收的数据经过时间间隔后输出;第二延迟单元包括:多个串联的第二延迟子单元;首个第二延迟子单元的输入端与采样模块连接,用于接收基于偶数据生成的第一延迟偶数据;每个第二延迟子单元的输入端与前一第二延迟子单元的输出端连接,每个第二延迟子单元用于将接收的数据经过时间间隔后输出。

7、在一些实施例中,每个第一延迟子单元包括第一触发器和第五非门,第一触发器的输入端作为第一延迟子单元的输入端,第一触发器的输出端与第五非门的输入端连接,第五非门的输出端作为第一延迟子单元的输出端;其中,第奇数个第一触发器的时钟端连接奇时钟的反相信号,第偶数个第一触发器的时钟端连接奇时钟;每个第二延迟子单元包括第二触发器和第六非门,第二触发器的输入端作为第二延迟子单元的输入端,第二触发器的反相输出端与第六非门的输入端连接,第六非门的输出端作为第二延迟子单元的输出端;其中,第奇数个第二触发器的时钟端连接偶时钟的反相信号,第偶数个第二触发器的时钟端连接偶时钟。

8、在一些实施例中,运算模块还包括:第一使能单元,与采样模块和第一延迟单元连接,用于响应于使能信号,将采样模块采样的奇数据传输至第一延迟单元的输入端并作为第一延迟奇数据;第二使能单元,与采样模块和第二延迟单元连接,用于响应于使能信号,将采样模块采样的偶数据传输至第二延迟单元的输入端并作为第一延迟偶数据。

9、在一些实施例中,输出时钟包括相位相反的第一输出时钟和第二输出时钟;在同一时刻下,第一输出时钟或第二输出时钟有效;其中任一输出时钟有效表征该输出时钟对应的采样时钟最先采样到片选信号。

10、在一些实施例中,输出模块包括:第一输出单元和第二输出单元,第一输出单元和第二输出单元的输出端连接;第一输出单元的输入端与第一运算单元连接,用于响应于第一输出时钟有效,在第一输出时钟处于第一状态时,实时获取第一运算单元输出的运算结果;以及,在第一输出时钟处于第二状态时,锁存当前的运算结果以及停止获取新的运算结果并输出锁存的运算结果;第二输出单元的输入端与第二运算单元连接,用于响应于第二输出时钟有效,在第二输出时钟处于第一状态时,实时获取第二运算单元输出的运算结果;以及,在第二输出时钟处于第二状态时,锁存当前的运算结果以及停止获取新的运算结果并输出锁存的运算结果。

11、在一些实施例中,第一输出单元包括:第一传输单元、第一锁存单元以及第二传输单元;其中,第一传输单元,与第一运算单元连接,用于在第一输出时钟处于第一状态时,将第一运算单元的运算结果的反相信号传输至第一锁存单元,以及,在第一输出时钟处于第二状态时,停止传输;第一锁存单元,用于在第一输出时钟处于第一状态时,将运算结果的反相信号传输至第二传输单元,以及,在第一输出时钟处于第二状态时,锁存当前的运算结果;第二传输单元,与第一锁存单元连接,用于在第一输出时钟处于第一状态时,停止输出,以及,在第一输出时钟处于第二状态时,输出第一锁存单元锁存的运算结果;第二输出单元包括:第三传输单元、第二锁存单元以及第四传输单元;其中,第三传输单元,与第二运算单元连接,用于在第二输出时钟处于第一状态时,将第二运算单元的运算结果的反相信号传输至第二锁存单元,以及,在第二输出时钟处于第二状态时,停止传输;第二锁存单元,用于在第二输出时钟处于第一状态时,将运算结果的反相信号传输至第四传输单元,以及,在第二输出时钟处于第二状态时,锁存当前的运算结果;第四传输单元,与第二锁存单元连接,用于在第二输出时钟处于第一状态时,停止输出,以及,在第二输出时钟处于第二状态时,输出第二锁存单元锁存的运算结果。

12、在一些实施例中,第一传输单元包括第一反相器、第一开关和第二开关;第一开关的一端连接供电信号,第一开关的另一端与第一反相器的供电端连接,第一开关的控制端连接第一输出时钟;第一反相器的输入端与第一运算单元连接,第一反相器的接地端与第二开关的一端连接;第二开关的另一端接地,第二开关的控制端连接第一输出时钟的反相信号;第一锁存单元包括第九非门和第一三态非门;第九非门的输入端与第一反相器的输出端和第一三态非门的输出端连接,第九非门的输出端与第一三态非门的输入端连接;第一三态非门的控制端连接第一输出时钟;第二传输单元包括第二反相器、第三开关和第四开关;第三开关的一端连接供电信号,第三开关的另一端与第二反相器的供电端连接,第三开关的控制端连接第一输出时钟的反相信号;第二反相器的输入端与第九非门的输出端连接,第二反相器的输出端用于输出运算结果,第二反相器的接地端与第四开关的一端连接;第四开关的另一端接地,第四开关的控制端连接第一输出时钟。

13、在一些实施例中,第三传输单元包括第三反相器、第五开关和第六开关;第五开关的一端连接供电信号,第五开关的另一端与第三反相器的供电端连接,第五开关的控制端连接第二输出时钟;第三反相器的输入端与第二运算单元连接,第三反相器的接地端与第六开关的一端连接;第六开关的另一端接地,第六开关的控制端连接第二输出时钟的反相信号;第二锁存单元包括第十非门和第二三态非门;第十非门的输入端与第三反相器的输出端和第二三态非门的输出端连接,第十非门的输出端与第二三态非门的输入端连接;第二三态非门的控制端连接第二输出时钟;第四传输单元包括第四反相器、第七开关和第八开关;第七开关的一端连接供电信号,第七开关的另一端与第四反相器的供电端连接,第七开关的控制端连接第二输出时钟的反相信号;第四反相器的输入端与第十非门的输出端连接,第四反相器的输出端用于输出运算结果,第四反相器的接地端与第八开关的一端连接;第八开关的另一端接地,第八开关的控制端连接第二输出时钟。

14、在一些实施例中,时间间隔为一个系统时钟周期。

15、根据一些实施例,本技术第二方面提供一种存储器,包括:如前的芯片测试电路。

16、本技术实施例提供的芯片测试电路及存储器中,采样模块基于奇时钟和偶时钟对连续多个片选信号进行采样获得奇数据和偶数据,运算模块基于奇数据和偶数据进行对比运算获得运算结果,输出模块响应于输出时钟输出运算结果,根据运算结果可检测出片选信号是否正常。通过上述方案,实现基于时钟周期为系统时钟周期两倍的奇时钟和偶时钟对片选信号中各数据位的采集、运算并输出运算结果,从而能够在保证采样准确可靠的同时,获得基于完整片选信号得到的运算结果并输出该运算结果,实现准确可靠的片选信号测试。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183766.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表