半导体装置的制作方法

- 国知局

- 2024-07-31 20:03:13

本发明的实施方式涉及半导体装置。

背景技术:

1、已知有能够将数据非易失性地存储的各种半导体存储装置等半导体装置。近年来的半导体装置中,正在推进使布线间隔变窄的技术。

技术实现思路

1、实施方式提供能够抑制布线的拖尾现象的半导体装置。

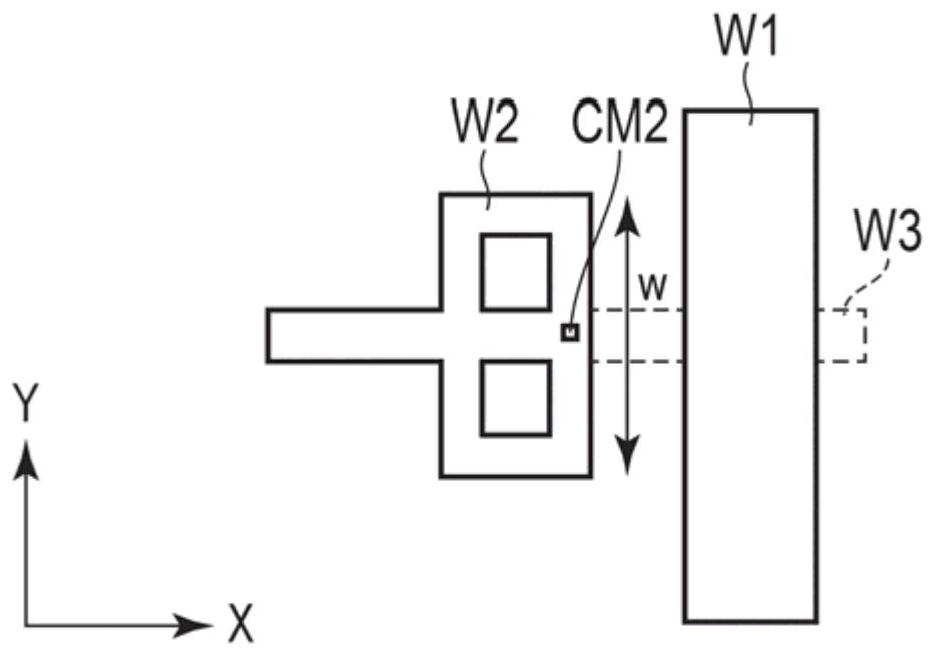

2、实施方式的半导体装置具备第1布线和第2布线。第2布线相对于第1布线隔开规定的布线间隔而配置,端部形成1个以上的环。

技术特征:1.一种半导体装置,其中,

2.根据权利要求1所述的半导体装置,其中,所述第二布线的所述端部形成为两个矩形环。

3.根据权利要求1所述的半导体装置,其中,所述矩形环中的一个矩形环具有长度为500nm或更大长度的各边。

4.根据权利要求1所述的半导体装置,其中,所述第二布线的所述宽度为200nm或更小,所述矩形环中的一个矩形环具有长度为500nm或更大长度的各边。

5.根据权利要求1所述的半导体装置,其中,所述规定距离实质上等于所述第二布线的宽度。

6.根据权利要求1所述的半导体装置,其中,所述矩形环的所述边中只有两个边面对所述第一布线并且平行于所述第一方向。

7.根据权利要求1所述的半导体装置,其中,所述第二布线的所述宽度在所述环中保持恒定。

8.根据权利要求1所述的半导体装置,其中,所述第一布线和所述第二布线通过反应性离子蚀刻形成。

9.根据权利要求1所述的半导体装置,其中,所述第三布线通过镶嵌工艺形成。

10.根据权利要求1所述的半导体装置,其中,所述第一布线和所述第二布线均为铝布线。

11.根据权利要求1所述的半导体装置,其中,所述第三布线是铜布线。

12.根据权利要求1所述的半导体装置,其中,所述第一布线和所述第二布线中的一个是电源线。

13.根据权利要求1所述的半导体装置,其中,高电压被施加到所述第一布线和所述第二布线中的一个。

14.根据权利要求1所述的半导体装置,其中,所述第一布线和所述第二布线中的一个是信号线。

15.根据权利要求1所述的半导体装置,其中,所述第一布线具有在所述第二方向上的宽度,所述第二布线具有在所述第一方向上的宽度,并且所述第一布线的所述宽度实质上等于所述第二布线的所述宽度。

16.根据权利要求1所述的半导体装置,其中,所述第一布线具有在所述第二方向上的宽度,所述第二布线具有在所述第一方向上的宽度,并且所述第一布线的所述宽度大于所述第二布线的所述宽度。

17.根据权利要求1所述的半导体装置,其中,所述第三布线平行于所述第二方向延伸。

18.根据权利要求1所述的半导体装置,进一步包括:

19.根据权利要求18所述的半导体装置,其中,所述存储器柱中的每一个存储器柱包括电荷蓄积膜、沟槽绝缘膜和半导体材料。

20.根据权利要求1所述的半导体装置,其中,所述第一布线层在所述第二布线层之上。

21.根据权利要求1所述的半导体装置,进一步包括:

22.根据权利要求21所述的半导体装置,其中,所述位线平行于所述第一方向延伸。

23.根据权利要求21所述的半导体装置,进一步包括:

24.根据权利要求23所述的半导体装置,进一步包括:

25.根据权利要求1至24中任一项所述的半导体装置,进一步包括:

26.根据权利要求1至24中任一项所述的半导体装置,其中,所述第一布线的宽度大于所述第三布线的宽度,并且所述第三布线是铜布线。

27.根据权利要求1至24中任一项所述的半导体装置,其中,与所述第二布线层的厚度相比,所述第一布线层的厚度更厚。

28.根据权利要求1至24中任一项所述的半导体装置,进一步包括:

29.根据权利要求1至24中任一项所述的半导体装置,其中,所述矩形环中的一个矩形环具有长度为600nm或更大长度的各边。

30.根据权利要求1至24中任一项所述的半导体装置,进一步包括:

31.根据权利要求1至24中任一项所述的半导体装置,其中,所述半导体装置被配置为从存储器控制器接收指令锁存使能信号和地址锁存使能信号。

32.一种存储器系统,包括:

33.根据权利要求32所述的存储器系统,其中,所述半导体装置与所述存储器控制器之间的通信使用指令锁存使能信号和地址锁存使能信号。

34.根据权利要求32所述的存储器系统,进一步包括:

35.一种半导体装置,包括:

36.根据权利要求35所述的半导体装置,其中,所述第二布线的宽度为200nm或更小。

37.根据权利要求35所述的半导体装置,其中,所述一个或多个矩形环的所述第一边具有500nm或更大的长度。

38.据权利要求35所述的半导体装置,其中,所述规定距离实质上等于所述第二布线的宽度。

39.根据权利要求35所述的半导体装置,其中,所述规定距离为200nm或更小。

40.根据权利要求35所述的半导体装置,其中,

41.根据权利要求35所述的半导体装置,其中,所述第一布线和所述第二布线通过反应性离子蚀刻形成。

42.根据权利要求35所述的半导体装置,进一步包括:

43.根据权利要求35所述的半导体装置,其中,所述第一布线层还包括第四布线和第五布线,与所述第四布线和所述第五布线之间的下部布线间隔相比,所述第四布线与所述第五布线之间的上部布线间隔更宽。

44.根据权利要求35所述的半导体装置,其中,所述第一布线和所述第二布线中的一个是信号线。

45.根据权利要求35所述的半导体装置,其中,所述第一布线的宽度实质上等于所述第二布线的宽度。

46.根据权利要求35至45中任一项所述的半导体装置,进一步包括:

47.根据权利要求35至45中任一项所述的半导体装置,进一步包括:

48.根据权利要求35至45中任一项所述的半导体装置,进一步包括:

49.根据权利要求35至45中任一项所述的半导体装置,其中,所述半导体装置接收写入使能信号。

50.一种半导体装置,包括:

51.根据权利要求50所述的半导体装置,其中,所述第二布线在与所述第一方向交叉的第二方向上具有宽度,并且所述第二布线的所述宽度为200nm或更小。

52.根据权利要求50所述的半导体装置,其中,所述矩形环的每一个边具有500nm或更大的长度。

53.根据权利要求50所述的半导体装置,其中,所述矩形环的所述第一边平行于所述第一方向。

54.根据权利要求50所述的半导体装置,其中,所述规定距离实质上等于所述第二布线的宽度。

55.根据权利要求50所述的半导体装置,其中,第二布线的宽度在所述环中保持恒定。

56.根据权利要求50所述的半导体装置,进一步包括:

57.根据权利要求50所述的半导体装置,进一步包括:

58.根据权利要求57所述的半导体装置,其中,在所述第一布线层和所述栅电极层之间设置所述第二布线层。

59.根据权利要求50所述的半导体装置,其中,所述第一布线的宽度与所述第三布线的宽度不同。

60.根据权利要求50所述的半导体装置,其中,所述第三布线在所述第一方向上延伸。

61.根据权利要求50所述的半导体装置,其中,所述第三布线在与所述第一方向交叉的第二方向上延伸。

62.根据权利要求50所述的半导体装置,进一步包括:

63.根据权利要求62所述的半导体装置,其中,

64.根据权利要求62所述的半导体装置,其中,

65.根据权利要求50所述的半导体装置,进一步包括:

66.根据权利要求65所述的半导体装置,其中,在所述第一布线层和所述栅电极层之间设置所述第二布线层。

67.根据权利要求65所述的半导体装置,其中,所述第一布线层和所述第二布线层是彼此相邻的布线层。

68.根据权利要求65所述的半导体装置,其中,所述多条第一布线中的一条第一布线的宽度与所述第三布线的宽度不同。

69.根据权利要求65所述的半导体装置,其中,所述第三布线在所述第一方向上延伸。

70.根据权利要求65所述的半导体装置,其中,所述第三布线在与所述第一方向交叉的第二方向上延伸。

71.根据权利要求50所述的半导体装置,进一步包括:

72.根据权利要求50所述的半导体装置,其中,所述第一布线和所述第二布线通过反应性离子蚀刻形成。

73.根据权利要求50所述的半导体装置,其中,

74.根据权利要求73所述的半导体装置,其中,所述矩形环的所述第一边、所述第二边、所述第三边和所述第四边具有500nm或更大的长度。

75.根据权利要求73所述的半导体装置,其中,所述第二布线的宽度和所述第二边之和为500nm或更大。

76.根据权利要求73所述的半导体装置,进一步包括:

77.根据权利要求50所述的半导体装置,进一步包括:

78.根据权利要求50所述的半导体装置,其中,所述第一布线和所述第二布线中的一个是信号线。

79.根据权利要求50所述的半导体装置,其中,所述第一布线的宽度实质上等于所述第二布线的宽度。

80.根据权利要求50所述的半导体装置,进一步包括:

81.根据权利要求80所述的半导体装置,其中,所述多个存储器柱中的每一个存储器柱包括电荷蓄积膜。

82.根据权利要求80所述的半导体装置,其中,所述多个存储器柱中的每一个存储器柱包括半导体膜和电荷蓄积膜。

83.根据权利要求50所述的半导体装置,进一步包括:

84.根据权利要求83所述的半导体装置,进一步包括:

85.根据权利要求50至84中任一项所述的半导体装置,进一步包括:

86.根据权利要求50至84中任一项所述的半导体装置,进一步包括:

87.根据权利要求50至84中任一项所述的半导体装置,其中,所述半导体装置接收写入使能信号。

88.根据权利要求50至84中任一项所述的半导体装置,其中,所述规定距离为200nm或更小。

89.根据权利要求50至84中任一项所述的半导体装置,其中,所述第二布线的宽度为200nm或更小,并且所述规定距离为200nm或更小。

90.根据权利要求50至84中任一项所述的半导体装置,其中,所述多条第一布线具有线和空间图案。

91.一种半导体装置的制造方法,包括:

92.根据权利要求91所述的半导体装置的制造方法,其中,所述第一布线层通过反应性离子蚀刻形成。

93.根据权利要求91所述的半导体装置的制造方法,其中,所述第一布线层包括铝布线。

94.一种半导体装置的制造方法,包括:

95.根据权利要求94所述的半导体装置的制造方法,其中,所述第一布线层通过反应性离子蚀刻形成。

96.一种半导体装置的制造方法,包括:

97.根据权利要求96所述的半导体装置的制造方法,其中,所述第一布线层通过反应性离子蚀刻形成。

98.根据权利要求96所述的半导体装置的制造方法,其中,所述第一布线层包括铝布线。

技术总结实施方式提供能够抑制布线的拖尾现象的半导体装置。实施方式的半导体装置具备第1布线W1和第2布线W2。第2布线W2与第1布线W1具有规定的布线间隔地配置。第2布线W2的端部形成1个以上的环。技术研发人员:梅泽多佳子受保护的技术使用者:铠侠股份有限公司技术研发日:技术公布日:2024/6/26本文地址:https://www.jishuxx.com/zhuanli/20240731/185227.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表