三维存储器件及其制造方法与流程

- 国知局

- 2024-08-02 15:45:05

本公开总体上涉及半导体,并且更具体地,涉及三维(three-dimensional,3d)存储器件及其制造方法。

背景技术:

1、随着人工智能(artificial intelligence,ai)、大数据、物联网、移动器件和通信、云储存等的不断崛起和发展,对存储容量的需求呈指数方式增长。与其他非易失性存储器相比,nand存储器具有许多优点,诸如集成度高、功耗低、编程/擦除速度快、可靠性好、成本低等,并且因此逐渐成为业界主流的半导体存储器。

2、通过改进工艺技术、电路设计、编程算法和制造工艺,平面nand存储单元被缩小到更小的尺寸。然而,随着存储单元的特征尺寸接近下限,平面工艺和制造技术变得具有挑战性和成本高昂。结果,平面存储单元的存储密度接近上限。

3、三维(3d)nand存储架构可以解决平面存储单元中的密度限制。该3d存储架构包括存储阵列和用于控制来往于存储阵列的信号的外围器件。

技术实现思路

1、在一个方面,公开了一种用于形成三维(3d)存储器件的方法。所述方法包括:形成包括核心区域、间隔体区域和外围区域的第一半导体结构,包括:在所述外围区域中在第一衬底上形成第一外围电路;在所述核心区域中在所述第一衬底上形成存储堆叠体;以及在所述间隔体区域中形成间隔体结构以分开所述存储堆叠体和所述第一外围电路;形成第二半导体结构,所述第二半导体结构包括在第二衬底上的第二外围电路;将所述第二半导体结构键合到所述第一半导体结构;以及形成补充半导体层以替换所述第一衬底的在所述核心区域中的部分。

2、在一些实施方式中,形成所述第一半导体结构还包括:在形成所述第一外围电路之后并且在形成所述存储堆叠体之前,去除所述第一衬底的在所述核心区域和所述间隔体区域中的第一部分,使得所述第一衬底的在所述外围区域和所述间隔体区域之间的剩余部分上形成异地(offsite)。

3、在一些实施方式中,形成所述第一半导体结构还包括:形成牺牲堆叠体,以覆盖所述核心区域和所述间隔体区域中的所述第一衬底并覆盖所述外围区域中的所述第一外围电路;形成电介质堆叠结构,以覆盖所述核心区域、所述间隔体区域和所述外围区域中的所述牺牲堆叠体;以及去除所述牺牲堆叠体和所述电介质堆叠结构的在所述外围区域中的部分。

4、在一些实施方式中,形成所述牺牲堆叠体包括:形成第一停止层,以覆盖所述核心区域和所述间隔体区域中的所述第一衬底,并覆盖所述外围区域中的所述第一外围电路;形成牺牲半导体层以覆盖所述第一停止层;形成第二停止层以覆盖所述第一停止层;以及形成屏障层以覆盖所述第二停止层。

5、在一些实施方式中,形成所述第一半导体结构还包括:去除所述电介质堆叠结构的在所述核心区域中的部分以形成阶梯结构,使得在所述间隔体区域中的包括转向结构的所述电介质堆叠结构的剩余部分形成所述间隔体结构。

6、在一些实施方式中,形成所述第一半导体结构还包括:在所述核心区域中形成多个沟道结构,所述多个沟道结构穿过所述电介质堆叠结构并延伸到所述牺牲堆叠体中,每个沟道结构包括功能层和半导体沟道。

7、在一些实施方式中,形成所述第一半导体结构还包括:在所述核心区域中形成多个虚设沟道结构,所述多个虚设沟道结构穿过所述电介质堆叠结构并延伸到所述牺牲堆叠体中。

8、在一些实施方式中,形成所述第一半导体结构还包括:在所述核心区域中形成至少一个缝隙,所述至少一个缝隙穿过所述电介质堆叠结构并延伸到所述牺牲堆叠体中;以及将所述电介质堆叠结构转换成所述存储堆叠体。

9、在一些实施方式中,形成所述电介质堆叠结构包括:形成堆叠在所述牺牲堆叠体上的多个电介质层对,每个电介质层对包括堆叠牺牲层和不同于所述堆叠牺牲层的堆叠电介质层。

10、在一些实施方式中,将所述电介质堆叠结构转换为所述存储堆叠体包括:经所述缝隙去除所述电介质堆叠结构中的所述多个堆叠牺牲层以形成多个沟槽;以及在每个沟槽中形成栅极结构。

11、在一些实施方式中,形成所述第一半导体结构还包括:在所述核心区域中形成多个字线接触部、多个沟道结构接触部;在所述外围区域中形成多个外围接触部;以及形成分别与对应的字线接触部、沟道结构接触部和外围接触部连接的多个第一互连接触部。

12、在一些实施方式中,形成所述第一外围电路包括:在所述外围区域中在所述第一衬底上形成包括多个高电压晶体管的高电压电路。

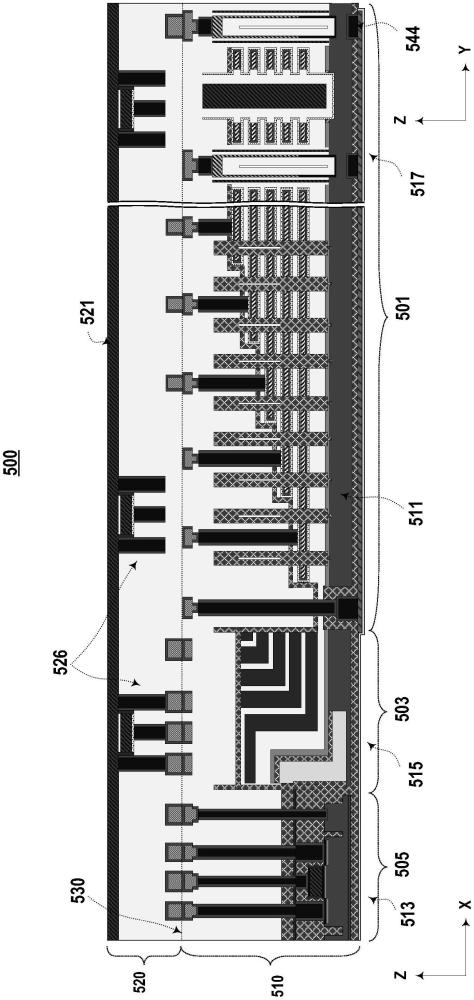

13、在一些实施方式中,形成所述第一外围电路还包括:在所述外围区域中在所述第一衬底上形成包括多个低电压晶体管的低电压电路。

14、在一些实施方式中,形成所述第二外围电路包括:在所述第二衬底上形成包括多个低低电压晶体管的低低电压电路;以及形成分别与对应的低低电压晶体管连接的多个第二互连接触部。

15、在一些实施方式中,形成所述第二外围电路还包括:在所述第二衬底上形成包括多个低电压晶体管的低电压电路。

16、在一些实施方式中,将所述第二半导体结构键合到所述第一半导体结构包括:以面对面的方式将所述第二半导体结构键合到所述第一半导体结构,以将所述第二互连接触部分别连接到对应的第二互连接触部。

17、在一些实施方式中,形成所述补充半导体层以替换所述第一衬底的在所述核心区域中的所述部分包括:去除所述第一衬底的第二部分并在所述第一停止层处停止,使得保留所述第一衬底的在所述外围区域中的第三部分;在所述第一衬底的在所述外围区域中的所述第三部分上形成保护层;去除所述牺牲半导体层的在所述核心区域中的部分,并在所述第二停止层处停止以暴露所述沟道结构的部分;去除每个沟道结构的所述功能层的部分以暴露所述半导体沟道;以及对每个沟道结构的所述半导体沟道的部分进行掺杂。

18、在一些实施方式中,去除每个沟道结构的所述功能层的所述部分包括:去除每个沟道结构的阻挡层、储存层和隧穿层的位于所述屏障层上方的部分;以及同时去除所述核心区域中的所述第二停止层以及所述外围区域中的所述保护层。

19、在一些实施方式中,形成所述补充半导体层以替换所述第一衬底的在所述核心区域中的所述部分包括:在所述核心区域中形成所述补充半导体层,以与每个沟道结构的所述半导体沟道的掺杂部分电连接;以及对所述补充半导体层的在所述核心区域中的部分执行局部热处理,而不影响所述第一衬底的在所述外围区域中的剩余部分。

20、在一些实施方式中,还包括在所述补充半导体层上形成焊盘层,包括:在所述核心区域中在所述补充半导体层上、并在所述第一衬底的在所述外围区域中的剩余部分上形成焊盘电介质层;形成嵌入所述焊盘电介质层中的多个焊盘结构;在所述焊盘电介质层上形成布线层以与所述多个焊盘结构连接;以及形成钝化层以覆盖所述布线层。

21、本公开的另一方面提供了一种三维(3d)存储器件,包括:第一半导体结构,包括核心区域、间隔体区域和外围区域,所述第一半导体结构包括:在所述核心区域中在半导体层上的存储堆叠体;在所述外围区域中在所述半导体层上的第一外围电路;以及在所述间隔体区域中的间隔体结构,以将所述存储堆叠体和所述第一外围电路分开;以及第二半导体结构,包括在衬底上的第二外围电路;其中,所述第二半导体结构连接到所述第一半导体结构。

22、在一些实施方式中,所述间隔体结构包括所述间隔体区域中的电介质堆叠结构,所述电介质堆叠结构包括多个电介质层对,每个电介质层对包括堆叠牺牲层和不同于所述堆叠牺牲层的堆叠电介质层。

23、在一些实施方式中,所述间隔体结构包括转向结构,所述转向结构包括所述多个电介质层对的在水平面内延伸的第一部分和所述多个电介质层对的在非水平面内延伸的第二部分。

24、在一些实施方式中,所述第一半导体结构还包括:在所述核心区域中的多个沟道结构,穿过所述存储堆叠体,每个沟道结构包括功能层和半导体沟道。

25、在一些实施方式中,所述第一半导体结构还包括:在所述存储堆叠体中的阶梯结构;以及在所述核心区域中的多个虚设沟道结构,穿过所述阶梯结构。

26、在一些实施方式中,所述第一半导体结构还包括:至少一个缝隙结构,穿过所述存储堆叠体并在平行方向上延伸以分开所述多个沟道结构。

27、在一些实施方式中,所述存储堆叠体包括:在垂直方向上堆叠的多个交错的堆叠电介质层和栅极结构。

28、在一些实施方式中,所述第一半导体结构还包括:在所述核心区域中的多个字线接触部、多个沟道结构接触部;在所述外围区域中的多个外围接触部;以及多个第一互连接触部,分别与对应的字线接触部、沟道结构接触部和外围接触部连接。

29、在一些实施方式中,所述第一外围电路包括:高电压电路,包括在所述外围区域中的所述半导体层上的多个高电压晶体管。

30、在一些实施方式中,所述第一外围电路还包括:低电压电路,包括在所述外围区域中的所述半导体层上的多个低电压晶体管。

31、在一些实施方式中,所述第二外围电路包括:低低电压电路,包括在所述衬底上的多个低低电压晶体管;以及多个第二互连接触部,分别与对应的低低电压晶体管连接。

32、在一些实施方式中,所述第二外围电路还包括:低电压电路,包括在所述衬底上的多个低电压晶体管。

33、在一些实施方式中,所述第二半导体结构和所述第一半导体结构以面对面的方式键合在一起,使得所述第二互连接触部和对应的第二互连接触部分别在键合界面处连接。

34、在一些实施方式中,每个沟道结构的所述功能层包括阻挡层、储存层和隧穿层;并且所述半导体沟道包括与所述半导体层接触的掺杂区域。

35、在一些实施方式中,所述器件还包括在所述半导体层上的焊盘层,所述焊盘层包括:焊盘电介质层,在所述半导体层上;多个焊盘结构,嵌入所述焊盘电介质层中;布线层,在所述焊盘电介质层上,以与所述多个焊盘结构连接;以及钝化层,用于覆盖所述布线层。

36、在一些实施方式中,所述半导体层还包括:在所述外围区域中的初始半导体层;以及在所述核心区域和所述间隔体区域中的补充半导体层;其中,所述初始半导体层通过间隔体层与所述补充半导体层隔离。

37、本公开的另一方面提供了一种存储系统,包括:存储器件,被配置为存储数据,并且包括:包括核心区域、间隔体区域和外围区域的第一半导体结构,所述第一半导体结构包括:存储堆叠体,包括在所述核心区域中在半导体层上的存储单元阵列;第一外围电路,在所述外围区域中在所述半导体层上;以及间隔体结构,在所述间隔体区域中,以将所述存储堆叠体和所述第一外围电路分开;以及第二半导体结构,包括在衬底上的第二外围电路,其中,所述第二半导体结构与所述第一半导体结构在键合界面处键合;以及存储器控制器,耦合到所述存储器件并被配置为通过所述第一外围电路和所述第二外围电路控制所述存储单元阵列。

38、根据本公开的说明书、权利要求书和附图,本领域技术人员可以理解本公开的其他方面。

本文地址:https://www.jishuxx.com/zhuanli/20240801/247669.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表