半导体器件的制备方法与流程

- 国知局

- 2024-07-31 18:46:24

本发明涉及半导体,尤其涉及一种半导体器件的制备方法。

背景技术:

1、现有的半导体制造技术较难在晶圆上形成完全隔离的绝缘结构,通常需要使用绝缘衬底上硅工艺来实现,可以有效改善因器件特征尺寸减小所产生的衬底效应,还可以通过先形成沟槽隔离结构,然后在衬底中形成各类掺杂区以及器件结构来实现。而由于沟槽隔离结构一般为深沟槽隔离,不仅制程较为复杂,还需要考虑到器件结构与沟槽隔离结构的间距相匹配,以及需要考虑到阱区的扩散范围与阱区和沟槽隔离结构间的距离,因此在先形成沟槽隔离结构后,使得后续工艺制程(形成各类掺杂区以及器件结构)难度增加,工艺复杂。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制备方法,易于实现,适用于不同技术节点的制程,且能够提高器件的可靠性。

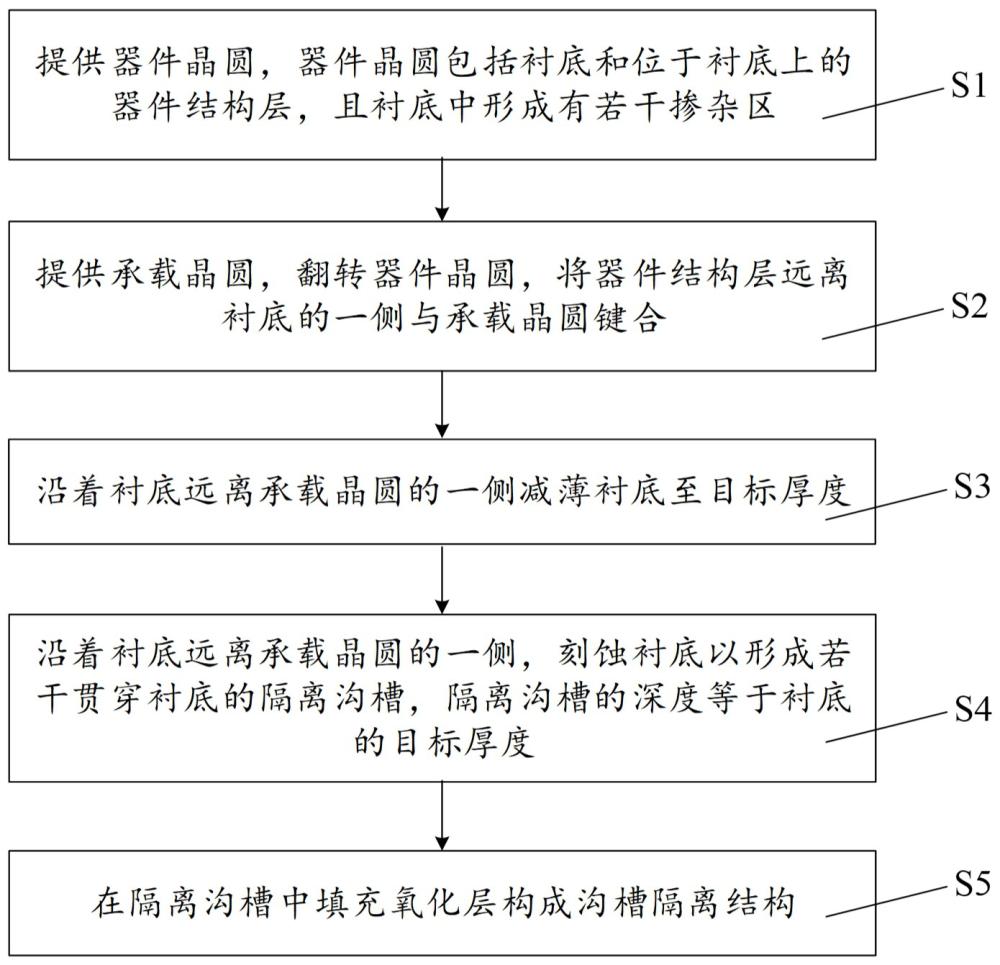

2、为了达到上述目的,本发明提供了一种半导体器件的制备方法,包括:

3、提供器件晶圆,所述器件晶圆包括衬底和位于所述衬底上的器件结构层,且所述衬底中形成有若干掺杂区;

4、提供承载晶圆,翻转所述器件晶圆,将所述器件结构层远离所述衬底的一侧与所述承载晶圆键合;

5、沿着所述衬底远离所述承载晶圆的一侧减薄所述衬底至目标厚度;

6、沿着所述衬底远离所述承载晶圆的一侧,刻蚀所述衬底以形成若干贯穿所述衬底的隔离沟槽,所述隔离沟槽的深度等于所述衬底的目标厚度;以及,

7、在所述隔离沟槽中填充氧化层构成沟槽隔离结构。

8、可选的,提供所述器件晶圆时,所述衬底和所述器件结构层之间形成有刻蚀停止层,刻蚀所述衬底形成所述隔离沟槽的步骤包括:

9、形成图形化的光刻胶层覆盖所述衬底远离所述承载晶圆的一侧;

10、以所述图形化的光刻胶层为掩模刻蚀所述衬底且刻蚀停于所述刻蚀停止层的表面,以形成若干贯穿所述衬底的隔离沟槽;以及,

11、去除所述图形化的光刻胶层。

12、可选的,刻蚀所述衬底形成所述隔离沟槽的工艺进程包括若干次循环执行的沉积工艺和刻蚀工艺,通过调节所述沉积工艺的沉积量和所述刻蚀工艺的刻蚀量的比例来控制所述隔离沟槽的深度与所述隔离沟槽的侧壁形貌。

13、可选的,所述沉积工艺的沉积量和所述刻蚀工艺的刻蚀量的比例为1:10~10:1。

14、可选的,所述沉积工艺的工艺气体包括c4f8,所述刻蚀工艺的工艺气体包括sf6。

15、可选的,所述隔离沟槽的深宽比大于10。

16、可选的,在所述衬底中,所述隔离沟槽与所述掺杂区错位布置。

17、可选的,采用高深宽比填充工艺在所述隔离沟槽中填充所述氧化层。

18、可选的,在填充所述氧化层后,所述氧化层延伸覆盖所述衬底远离所述承载晶圆的一侧且所述氧化层的表面不平;执行研磨工艺,研磨去除所述衬底远离所述承载晶圆的一侧部分厚度的所述氧化层使得剩余的所述氧化层的表面齐平。

19、可选的,在执行研磨工艺后,所述衬底远离所述承载晶圆的一侧剩余的氧化层的厚度为1000埃~8000埃。

20、在本发明提供的半导体器件的制备方法中,提供器件晶圆,器件晶圆包括衬底和位于衬底上的器件结构层,且衬底中形成有若干掺杂区;提供承载晶圆,翻转器件晶圆,将器件结构层远离衬底的一侧与承载晶圆键合;沿着衬底远离承载晶圆的一侧减薄衬底至目标厚度;沿着衬底远离承载晶圆的一侧,刻蚀衬底以形成若干贯穿衬底的隔离沟槽,隔离沟槽的深度等于衬底的目标厚度;在隔离沟槽中填充氧化层构成沟槽隔离结构。本发明意想不到的技术效果是在形成沟槽隔离结构之前,器件结构和掺杂区已经形成,相较于常规工艺先形成沟槽隔离结构后形成掺杂区和器件结构,在形成掺杂区和器件结构时需要考虑各个掺杂区的扩散范围和沟槽隔离结构与掺杂区及器件结构的间距相匹配,制备难度大,本申请在形成隔离沟槽时,由于器件结构和掺杂区已经形成,只需要根据器件结构和掺杂区的位置设置隔离沟槽,制备难度低,更易于实现,且适用于不同技术节点的制程;并且通过控制减薄衬底至目标厚度,就能够实现控制隔离沟槽的深度,实现深槽隔离以提高器件的隔离效果;以及相较于绝缘衬底上硅的方式,本申请无需额外的离子注入工艺就能够实现全隔离器件,或者相较于绝缘硅岛的方式,本申请在降低工艺复杂程度的同时,能够确保器件在高速工作时无结电容以及热效应产生,能够提高器件的可靠性。

技术特征:1.一种半导体器件的制备方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的制备方法,其特征在于,提供所述器件晶圆时,所述衬底和所述器件结构层之间形成有刻蚀停止层,刻蚀所述衬底形成所述隔离沟槽的步骤包括:

3.如权利要求1或2所述的半导体器件的制备方法,其特征在于,刻蚀所述衬底形成所述隔离沟槽的工艺进程包括若干次循环执行的沉积工艺和刻蚀工艺,通过调节所述沉积工艺的沉积量和所述刻蚀工艺的刻蚀量的比例来控制所述隔离沟槽的深度与所述隔离沟槽的侧壁形貌。

4.如权利要求3所述的半导体器件的制备方法,其特征在于,所述沉积工艺的沉积量和所述刻蚀工艺的刻蚀量的比例为1:10~10:1。

5.如权利要求3所述的半导体器件的制备方法,其特征在于,所述沉积工艺的工艺气体包括c4f8,所述刻蚀工艺的工艺气体包括sf6。

6.如权利要求3所述的半导体器件的制备方法,其特征在于,所述隔离沟槽的深宽比大于10。

7.如权利要求1所述的半导体器件的制备方法,其特征在于,在所述衬底中,所述隔离沟槽与所述掺杂区错位布置。

8.如权利要求1所述的半导体器件的制备方法,其特征在于,采用高深宽比填充工艺在所述隔离沟槽中填充所述氧化层。

9.如权利要求1所述的半导体器件的制备方法,其特征在于,在填充所述氧化层后,所述氧化层延伸覆盖所述衬底远离所述承载晶圆的一侧且所述氧化层的表面不平;执行研磨工艺,研磨去除所述衬底远离所述承载晶圆的一侧部分厚度的所述氧化层使得剩余的所述氧化层的表面齐平。

10.如权利要求9所述的半导体器件的制备方法,其特征在于,在执行研磨工艺后,所述衬底远离所述承载晶圆的一侧剩余的氧化层的厚度为1000埃~8000埃。

技术总结本发明提供了一种半导体器件的制备方法,包括:提供器件晶圆,器件晶圆包括衬底和位于衬底上的器件结构层,且衬底中形成有若干掺杂区;提供承载晶圆,翻转器件晶圆,将器件结构层远离衬底的一侧与承载晶圆键合;沿着衬底远离承载晶圆的一侧减薄衬底至目标厚度;沿着衬底远离承载晶圆的一侧,刻蚀衬底以形成若干贯穿衬底的隔离沟槽,隔离沟槽的深度等于衬底的目标厚度;在隔离沟槽中填充氧化层构成沟槽隔离结构。本发明易于实现,适用于不同技术节点的制程,且能够提高器件的可靠性。技术研发人员:姚悦,蒲甜松,柏佩文,李庆民受保护的技术使用者:合肥晶合集成电路股份有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/180397.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表