半导体器件的制作方法与流程

- 国知局

- 2024-07-31 18:45:09

本申请涉及半导体器件及集成电路,尤其涉及一种半导体器件的制作方法。

背景技术:

1、金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effecttransistor,mosfet,本申请中简称为“mos”)器件是应用于模拟电路与数字电路的电子器件。其中,沟槽型mos(trench mos)器件由于具有更低的导通电阻和栅漏电荷密度,从而具有更低的导通和开关损耗,以及更快的开关速度,其通常被作为功率器件(又被称为“电子电力器件”)被广泛应用于消费电子产品、新能源汽车、服务器以及控制设备等领域。通常,为了获取更好的器件性能,可在集成有沟槽型器件的晶圆上设置用于隔离的终端环(terminal ring)结构。

2、参考图1,其示出了相关技术中提供的终端结构的剖面示意图,如图1所示,衬底110中形成有第一沟槽101和第二沟槽102,衬底110和沟槽表面形成有第一氧化物层121,第一沟槽101和第二沟槽102中填充有多晶硅层131、132,第一沟槽101中的第一氧化物层121和多晶硅层131构成第一终端环(guard ring),第一沟槽102中的第一氧化物层121和多晶硅层132构成第二终端环,第一终端环和第二终端环上方形成有第二氧化物层122,第一氧化物层121和第二氧化物层122上形成有层间介电(inter-layer dielectric,ild)层123,层间介电层123和第二终端环中形成有第一接触孔(contact,ct)151,接触孔151的底部与多晶硅层132接触,其顶部与金属引出层153接触,第一终端环和第二终端之间形成有第二接触孔152,第二接触孔152的顶部与金属引出层153的底部接触。

3、在设置有终端结构的半导体器件的制作过程中,在形成多晶硅层后需要进行回刻蚀,如图1所示,由于多晶硅层131、132的顶部与周围的台阶差过大,因此在刻蚀后容易形成多晶硅残留(如图1中虚线所示),残留缺陷容易导致击穿或源极、漏极短路,从而降低了器件产品的可靠性和良率。

技术实现思路

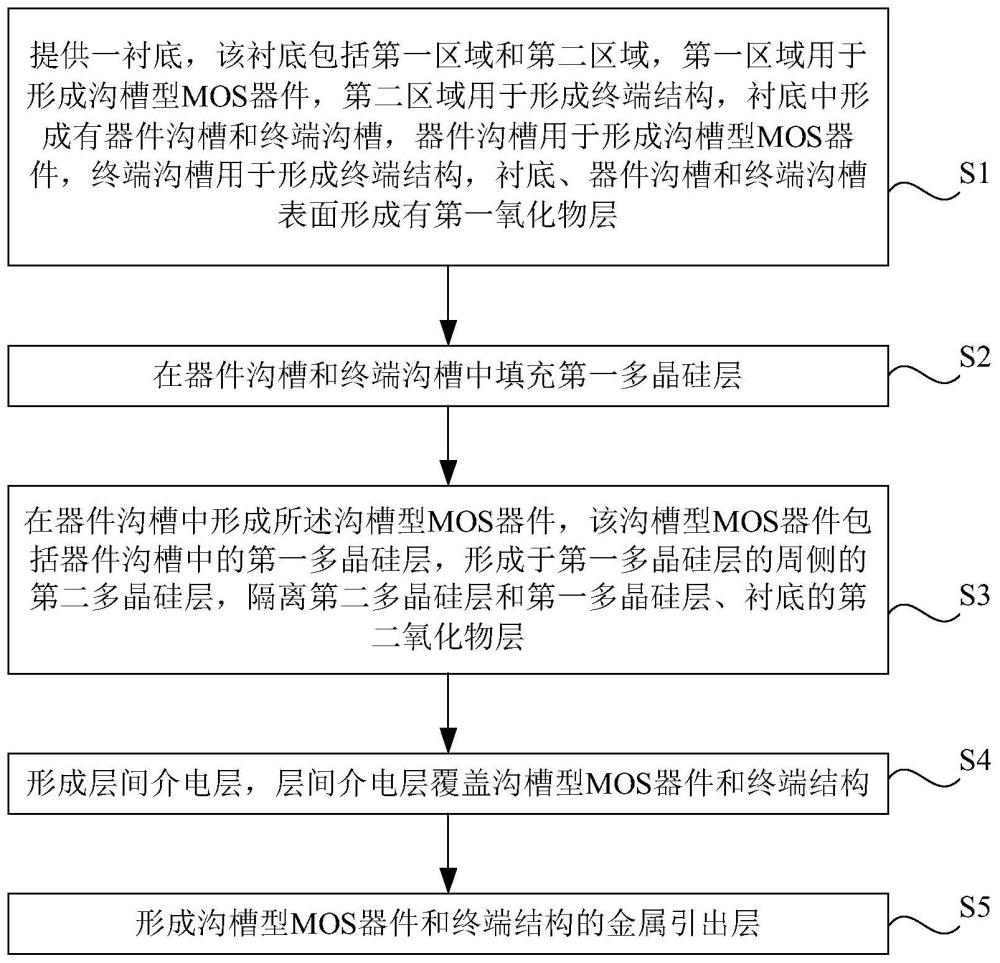

1、本申请提供了一种半导体器件的制作方法,可以解决相关技术中提供的设置有终端结构的沟槽型mos器件在制作过程中容易在终端结构的顶部形成多晶硅残留的问题,该方法包括:

2、提供一衬底,所述衬底包括第一区域和第二区域,所述第一区域用于形成沟槽型mos器件,所述第二区域用于形成终端结构,所述衬底中形成有器件沟槽和终端沟槽,所述器件沟槽用于形成沟槽型mos器件,所述终端沟槽用于形成终端结构,所述衬底、所述器件沟槽和所述终端沟槽表面形成有第一氧化物层;

3、在所述器件沟槽和所述终端沟槽中填充第一多晶硅层;

4、在所述器件沟槽中形成所述沟槽型mos器件,所述沟槽型mos器件包括所述器件沟槽中的第一多晶硅层,形成于第一多晶硅层的周侧的第二多晶硅层,隔离所述第二多晶硅层和第一多晶硅层、衬底的第二氧化物层;

5、形成层间介电层,所述层间介电层覆盖所述沟槽型mos器件和所述终端结构;

6、形成所述沟槽型mos器件和所述终端结构的金属引出层。

7、在一些实施例中,所述在在所述器件沟槽中形成所述沟槽型mos器件,包括:

8、依次通过涂布光阻、曝光和显影在所述第二区域覆盖光阻,暴露出所述第一区域;

9、进行刻蚀,使所述器件沟槽中第一多晶硅层的顶部低于所述第一氧化物层的顶部;

10、进行刻蚀,去除所述第一区域中除器件沟槽外其他区域的第一氧化物层,使所述器件沟槽内第一氧化物层的顶部低于第一多晶硅层的顶部;

11、去除光阻;

12、形成第二氧化物层;

13、形成第二多晶硅层;

14、进行刻蚀,直至所述第一区域中除器件沟槽外其他区域的第二多晶硅层被去除。

15、在一些实施例中,在经过刻蚀后,所述器件沟槽中第一多晶硅层的顶部低于所述衬底的上表面的距离值小于2000埃。

16、在一些实施例中,所述终端结构包括第一终端环和第二终端环,所述终端沟槽包括第一沟槽和第二沟槽,所述第一沟槽和所述第二沟槽相邻,所述第一沟槽用于形成所述第一终端环,所述第二沟槽用于形成所述第二终端环;

17、所述形成所述沟槽型mos器件和所述终端结构的金属引出层,包括:

18、在所述层间介电层中形成第一通孔、第二通孔、第三通孔和第四通孔,所述第一通孔位于所述第一沟槽和所述第二沟槽之间,所述第二通孔位于所述第二沟槽中,所述第三通孔位于所述器件沟槽中,所述第四通孔位于所述器件沟槽的一侧;

19、在所述第一通孔、第二通孔、第三通孔和第四通孔中填充金属层,所述第一通孔中的金属层形成第一接触孔,所述第二通孔中的金属层形成第二接触孔,所述第三通孔中的金属层形成第三接触孔,所述第四通孔中的金属层形成第四接触孔,所述第二接触孔与所述第二沟槽内的第一多晶硅层接触,所述第四接触孔与器件沟槽内的第一多晶硅层接触,所述第一接触孔和所述第二接触孔分别与衬底接触;

20、在所述层间介电层上形成金属引出层,所述金属引出层的底部分别与所述第一接触孔的顶部、所述第二接触孔的顶部接触。

21、在一些实施例中,当所述半导体器件工作时,所述第一终端环用于接地,所述第二终端环用于接高电位。

22、本申请技术方案,至少包括如下优点:

23、通过在包含终端结构的沟槽型mos器件的制作过程中,在形成沟槽型mos器件层时,将终端结构所在区域进行隔离,从而避免了由于对多晶硅进行刻蚀造成其与表面氧化物层之间的台阶差所导致的多晶硅残留的问题,在一定程度上提高了器件产品的可靠性和良率。

技术特征:1.一种半导体器件的制作方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述在在所述器件沟槽中形成所述沟槽型mos器件,包括:

3.根据权利要求2所述的方法,其特征在于,在经过刻蚀后,所述器件沟槽中第一多晶硅层的顶部低于所述衬底的上表面的距离值小于2000埃。

4.根据权利要求1至3任一所述的方法,其特征在于,所述终端结构包括第一终端环和第二终端环,所述终端沟槽包括第一沟槽和第二沟槽,所述第一沟槽和所述第二沟槽相邻,所述第一沟槽用于形成所述第一终端环,所述第二沟槽用于形成所述第二终端环;

5.根据权利要求4所述的方法,其特征在于,当所述半导体器件工作时,所述第一终端环用于接地,所述第二终端环用于接高电位。

技术总结本申请公开了一种半导体器件的制作方法,包括:提供一衬底,该衬底包括第一区域和第二区域,第一区域用于形成沟槽型MOS器件,第二区域用于形成终端结构,衬底中形成有器件沟槽和终端沟槽,器件沟槽用于形成沟槽型MOS器件,终端沟槽用于形成终端结构,衬底、器件沟槽和终端沟槽表面形成有第一氧化物层;在器件沟槽和终端沟槽中填充第一多晶硅层;在器件沟槽中形成沟槽型MOS器件,沟槽型MOS器件包括器件沟槽中的第一多晶硅层,形成于第一多晶硅层的周侧的第二多晶硅层,隔离第二多晶硅层和第一多晶硅层、衬底的第二氧化物层;形成层间介电层,层间介电层覆盖沟槽型MOS器件和终端结构;形成沟槽型MOS器件和终端结构的金属引出层。技术研发人员:陈思彤,赵纪栋,王立乾,潘嘉受保护的技术使用者:华虹半导体(无锡)有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/180294.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

隔膜及电池的制作方法

下一篇

返回列表