DRAM电路的制作方法

- 国知局

- 2024-07-31 19:58:15

背景技术:

1、本发明涉及动态随机存取存储器(dram)电路。

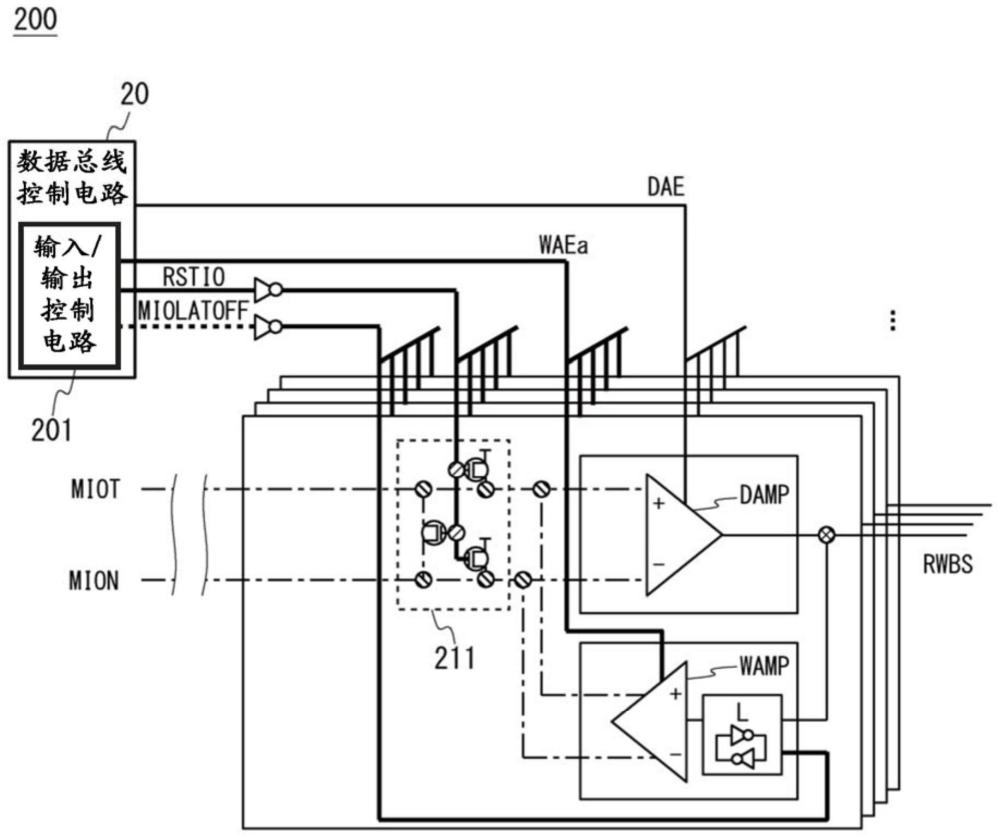

2、安装有dram电路的半导体芯片包括被布线为使得纵向穿过半导体芯片的一对主输入/输出线。一对主输入/输出线也被称为mio或一对差分i/o总线。在从dram电路读出数据的情况下,一对位线之间的微小差分电位被感测放大器放大,并且差分电位被传输到一对主输入/输出线。在将数据写入dram电路的情况下,写入放大器使一对主输入/输出线之间的电位差具有全振幅。然后,一对位线的数据被强制重写。

3、下面列出公开的技术。

4、[专利文献1]日本特开2003-151275号公报

5、[非专利文献1]由科学论坛公司(science forum corporation)的takao nakano和yoichi akasaka编辑的“ulsidram技术(ulsi dram technology)”。

6、一对主输入/输出线在读取周期的结束和写入周期的结束后被预充电(例如,参见专利文献1和非专利文献1)。因此,在读取周期的结束和写入周期的结束后,一对主输入/输出线总是被复位,并且下一个周期总是从相同的状态开始。

技术实现思路

1、近年来,作为在人工智能(ai)和移动设备中使用的高速缓存存储器,已经要求使用定制dram来代替静态随机存取存储器(sram)。

2、在用于此类用途的存储器中,行地址通过随机访问频繁地切换。因此,仅使用同一行地址多次顺序地操作列地址选通(cas)信号的频率低,使得由于顺序cas操作导致的功率降低的影响小。此外,在dram电路中需要多位高速操作,这导致可归因于数据传送的大功率损耗。

3、本发明的其它目的和新颖特征将从本说明书和附图的描述中显而易见。

4、根据本公开的一个实施例,提供有主输入/输出线对和复位电路的dram电路。主输入/输出线对的电位被保持在从写入周期的结束到写入周期之后的第一写入周期的开始的时段中,或者从写入周期的结束到写入周期之后的第一读取周期的开始的时段中。复位电路在第一读取周期的开始时复位主输入/输出线对的状态。

5、根据一个实施例,可以降低dram电路中的电流消耗。

技术特征:1.一种动态随机存取存储器(dram)电路,提供有主输入/输出线对和复位电路,

2.根据权利要求1所述的dram电路,

3.根据权利要求1所述的dram电路,包括:

4.根据权利要求1所述的dram电路,还包括:

5.根据权利要求1所述的dram电路,包括:

技术总结降低DRAM电路中的电流消耗。DRAM电路是提供有主输入/输出线对和复位电路的动态随机存取存储器(DRAM)电路。主输入/输出线对的电位被保持在从写入周期的结束到写入周期之后的第一写入周期的开始的时段中,或者从写入周期的结束到写入周期之后的第一读取周期的开始的时段中。复位电路在第一读取周期的开始时复位主输入/输出线对的状态。技术研发人员:福士哲夫,高桥弘行,松重宗明受保护的技术使用者:瑞萨电子株式会社技术研发日:技术公布日:2024/5/27本文地址:https://www.jishuxx.com/zhuanli/20240731/184821.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。