半导体装置的制作方法

- 国知局

- 2024-07-31 20:14:32

本发明的一个方式涉及一种半导体装置。尤其是,本发明的一个方式涉及一种包括存储装置的半导体装置。尤其是,本发明的一个方式涉及一种包括非易失性存储装置的半导体装置。注意,本发明的一个方式不局限于上述。本说明书等所公开的发明的一个方式的涉及一种物体、方法、驱动方法或制造方法。另外,本发明的一个方式涉及一种工序(process)、机器(machine)、产品(manufacture)或者组合物(composition ofmatter)。因此,具体而言,作为本说明书等所公开的本发明的一个方式的的一个例子,可以举出半导体装置、显示装置、发光装置、蓄电装置、光学装置、摄像装置、照明装置、运算装置、控制装置、存储装置、输入装置、输出装置、输入输出装置、信号处理装置、电子计算机、电子设备、它们的驱动方法或它们的制造方法。

背景技术:

1、cpu(central processing unit:中央处理器)、mpu(micro processing unit:微处理单元)或mcu(micro controller unit:微控制单元)等通过逐次进行对应于容纳在程序存储器中的程序(数据)的处理而进行一系列处理。从外围电路接收该处理所需的数据或通过该处理得到的数据或者将该处理所需的数据或通过该处理得到的数据传送到外围电路。根据使用者的希望使用各种外围电路。作为外围电路,例如可以举出dram(dynamicrandom access memory:动态随机存取存储器)接口、pci(peripheral componentinterface:外围设备接口)、dma(direct memory access:直接存储器访问)、网络接口、音频接口等。

2、另外,已知使用氧化物半导体的晶体管的泄漏电流在非导通状态下极低。例如,专利文献1已公开了应用使用氧化物半导体的晶体管的泄漏电流小的特性的低功耗cpu等。另外,例如专利文献2已公开了可以利用使用氧化物半导体的晶体管的泄漏电流低的特性实现存储内容的长期保持的存储装置等。

3、另外,专利文献3公开了一种包括包含有机el的发光器件的像素数多且清晰度高的显示装置。

4、[先行技术文献]

5、[专利文献]

6、[专利文献1]日本专利申请公开第2012-257187号公报

7、[专利文献2]日本专利申请公开第2011-151383号公报

8、[专利文献3]国际专利申请公开第2019/220278号

技术实现思路

1、发明所要解决的技术问题

2、在cpu的处理中,在将数据传送到特定外围电路或从特定外围电路接收数据时,不贡献于处理的其他外围电路处于静止状态。于是,通过进行停止向不贡献于处理的其他外围电路供电的电源门控,可以实现功耗的下降。然而,为了利用外围电路需要进行各种设定,且需要将设定数据容纳在设置在该外围电路中的设置寄存器中。因此,在外围电路从电源门控恢复时,需要将该设定数据再容纳在设置寄存器中。这种工作导致在进行电源门控时的能量的损失,所以即使进行电源门控功耗的下降效果也减少。

3、本发明的一个方式的目的之一是提供一种低功耗的半导体装置。此外,本发明的一个方式的目的之一是提供一种提高工作速度的半导体装置。此外,本发明的一个方式的目的之一是提供一种实现小型化的半导体装置。此外,本发明的一个方式的目的之一是提供一种可靠性高的半导体装置。此外,本发明的一个方式的目的之一是提供一种新颖半导体装置。

4、解决技术问题的手段

5、本发明是鉴于上述目的而实施的,在半导体装置中,由非易失性寄存器(包括在电源门控状态下也继续储存数据的存储电路的寄存器)构成cpu的寄存器及外围电路的设置寄存器,并且该半导体装置具有按每个块(按每个cpu、外围电路)分别进行电源门控的功能。各块通过在进行电源门控时也在非易失性寄存器继续储存数据而可以在从电源门控恢复后从设定该寄存器的数据的状态再次开始处理。该半导体装置具有根据半导体装置的处理对不贡献于该处理的块进行电源门控的功能。通过采用这种结构,可以降低贡献于半导体装置的实际上的处理的块以外的功耗,由此可以提供能够降低工作时的功耗的半导体装置。

6、(1)

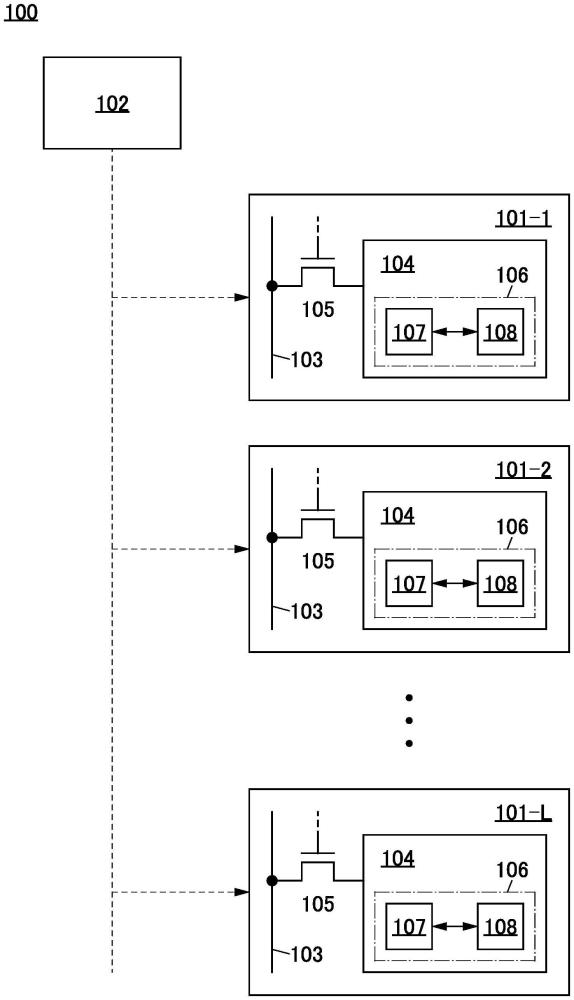

7、本发明的一个方式是一种半导体装置,包括:第一组件;第二组件;以及指令部,其中,第一组件包括具有在被供电的状态下储存第一设定信息的功能的第一存储电路以及具有在不被供电的状态下储存第一设定信息的功能的第二存储电路,第二组件包括具有在被供电的状态下储存第二设定信息的功能的第三存储电路以及具有在不被供电的状态下储存第二设定信息的功能的第四存储电路,指令部具有控制是否对第一组件和第二组件的每一个供电的功能,第一组件具有将第一存储电路所储存的第一设定信息写入到第二存储电路而处于不被供电的状态的功能以及使第一存储电路储存从第二存储电路读出的第一设定信息而处于被供电的状态的功能,第二组件具有将第三存储电路所储存的第二设定信息写入到第四存储电路而处于不被供电的状态的功能以及使第三存储电路储存从第四存储电路读出的第二设定信息而处于被供电的状态的功能,并且,第二存储电路及第四存储电路都包括在形成沟道的半导体层中包含金属氧化物的晶体管。

8、(2)

9、另外,在上述(1)中,第二存储电路及第四存储电路都可以包括第一晶体管及电容元件,第一晶体管的源极和漏极中的一个可以与电容元件的一个电极电连接,第一晶体管可以具有在不被供电的状态下处于非导通状态的功能,电容元件可以具有在第一晶体管处于非导通状态时保持电容元件的一个电极的电荷的功能,并且第一晶体管可以在形成沟道的半导体层中包含金属氧化物。

10、(3)

11、另外,在上述(1)中,第二存储电路及第四存储电路都可以包括第一晶体管及第二晶体管,第一晶体管的源极和漏极中的一个可以与第二晶体管的栅极电连接,第一晶体管可以具有在不被供电的状态下处于非导通状态的功能,第二晶体管可以具有在第一晶体管处于非导通状态时保持第二晶体管的栅极的电荷的功能,并且第一晶体管可以在形成沟道的半导体层中包含金属氧化物。

12、(4)

13、本发明的一个方式是一种半导体装置,包括:处理器核心;接口;以及指令部,其中,处理器核心包括具有在被供电的状态下储存第一设定信息的功能的第一寄存器以及具有在不被供电的状态下储存第一设定信息的功能的第一存储器,接口包括具有在被供电的状态下储存第二设定信息的功能的第二寄存器以及具有在不被供电的状态下储存第二设定信息的功能的第二存储器,指令部具有控制是否对处理器核心和接口的每一个供电的功能,处理器核心具有将第一寄存器所储存的第一设定信息写入到第一存储器而处于不被供电的状态的功能以及使第一寄存器储存从第一存储器读出的第一设定信息而处于被供电的状态的功能,接口具有将第二寄存器所储存的第二设定信息写入到第二存储器而处于不被供电的状态的功能以及使第二寄存器储存从第二存储器读出的第二设定信息而处于被供电的状态的功能,并且,第一存储器及第二存储器都包括在形成沟道的半导体层中包含金属氧化物的晶体管。

14、(5)

15、另外,在上述(4)中,第一存储器及第二存储器都可以包括第一晶体管及电容元件,第一晶体管的源极和漏极中的一个可以与电容元件的一个电极电连接,第一晶体管可以具有在不被供电的状态下处于非导通状态的功能,电容元件可以具有在第一晶体管处于非导通状态时保持电容元件的一个电极的电荷的功能,并且第一晶体管可以在形成沟道的半导体层中包含金属氧化物。

16、(6)

17、另外,在上述(4)中,第一存储器及第二存储器都可以包括第一晶体管及第二晶体管,第一晶体管的源极和漏极中的一个可以与第二晶体管的栅极电连接,第一晶体管可以具有在不被供电的状态下处于非导通状态的功能,第二晶体管可以具有在第一晶体管处于非导通状态时保持第二晶体管的栅极的电荷的功能,并且第一晶体管可以在形成沟道的半导体层中包含金属氧化物。

18、发明效果

19、本发明的一个方式可以提供一种低功耗的半导体装置。此外,本发明的一个方式可以提供一种提高工作速度的半导体装置。此外,本发明的一个方式可以提供一种实现小型化的半导体装置。此外,本发明的一个方式可以提供一种可靠性高的半导体装置。此外,本发明的一个方式可以提供一种新颖半导体装置。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185520.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。