芯片外驱动装置及其驱动能力增强方法与流程

- 国知局

- 2024-07-31 20:14:35

本发明涉及一种驱动装置,尤其涉及一种芯片外驱动装置及其驱动能力增强方法。

背景技术:

1、随着内存ddr4到ddr5的产品世代推进,内存的操作速度亦越加提升。在高速传输下,传输通道效应(channel effect)将造成传送信号上的振幅衰减,此信号衰退现象,随着信号操作频率的上升越显严重,致使数据信号于传输时因此失真。

技术实现思路

1、本发明提供一种芯片外驱动装置的驱动能力增强方法,可改善高速传输下信号失真的情形,提高芯片外驱动装置的输出信号质量。

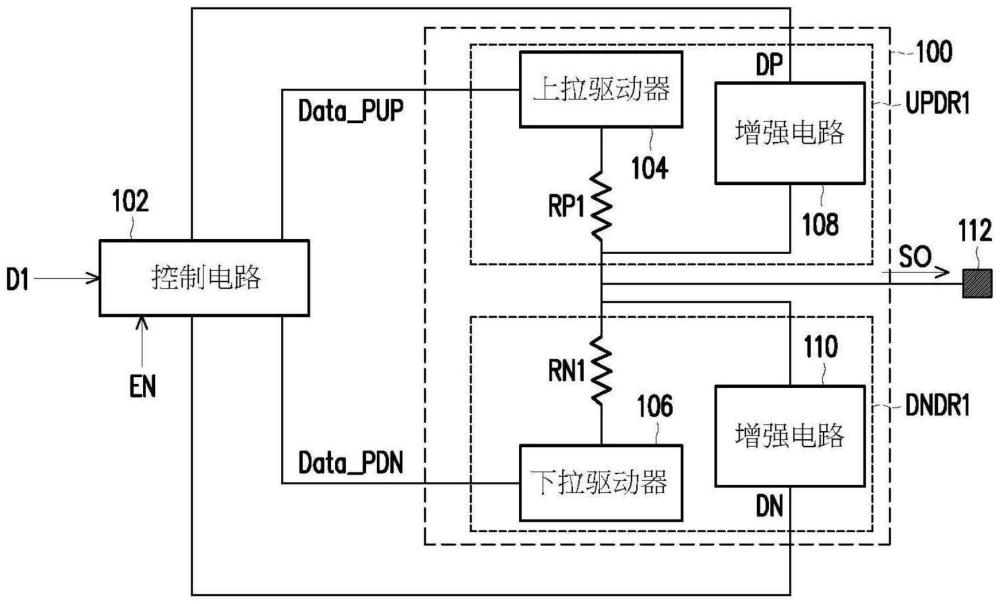

2、本发明的芯片外驱动装置包括驱动器电路以及控制电路。驱动器电路包括至少一上拉驱动器、至少一第一电阻、第一增强电路。第一电阻耦接于上拉驱动器与输入输出垫之间。第一增强电路耦接第一电阻。控制电路耦接上拉驱动器以及第一增强电路,检测输入数据信号的上升缘与下降缘,依据输入数据信号的上升缘与下降缘控制第一增强电路对输入输出垫提供第一增强信号。

3、在本发明的一实施例中,上述的第一增强电路连接于第一电阻的第一端、第一电阻的第二端或第一电阻的第一端与第二端间的位置。

4、在本发明的一实施例中,上述的驱动器电路还包括第一切换电路。第一切换电路耦接于第一增强电路与第一电阻之间,受控于控制电路而将第一增强电路切换连接于第一电阻的第一端、第一电阻的第二端或第一电阻的第一端与第二端间的位置。

5、在本发明的一实施例中,上述的第一切换电路包括多个第一开关,其分别耦接于第一增强电路与第一电阻上的对应连接位置之间,第一开关的导通状态受控于控制电路。

6、在本发明的一实施例中,上述的驱动器电路还包括下拉驱动器、至少一第二电阻以及第二增强电路。下拉驱动器耦接控制电路。第二电阻耦接于下拉驱动器与输入输出垫之间。第二增强电路耦接控制电路以及第二电阻,控制电路依据输入数据信号的上升缘与下降缘控制第二增强电路对输入输出垫提供第二增强信号。

7、在本发明的一实施例中,上述的第二增强电路连接于第二电阻的第一端、第二电阻的第二端或第二电阻的第一端与第二端间的位置。

8、在本发明的一实施例中,上述的驱动器电路还包括第二切换电路。第二切换电路耦接于第二增强电路与第二电阻之间,受控于该控制电路而将该第二增强电路连接于该第二电阻的第一端、该第二电阻的第二端或该第二电阻的第一端与第二端间的位置。

9、在本发明的一实施例中,上述的第二切换电路包括多个第二开关,分别耦接于第二增强电路与第二电阻上的对应连接位置之间,第二开关的导通状态受控于控制电路。

10、在本发明的一实施例中,上述的控制电路还依据使能信号于芯片外驱动装置处于增强模式时控制第二增强电路提供第二增强信号,并于芯片外驱动装置处于一般模式时控制第二增强电路不提供第二增强信号。

11、在本发明的一实施例中,上述的第二增强电路包括n型晶体管,其耦接于第一电阻与接地电压之间,n型晶体管的控制端耦接控制电路,n型晶体管受控于控制电路而于输入数据信号出现下降缘时被导通。

12、在本发明的一实施例中,上述的控制电路还依据使能信号于芯片外驱动装置处于增强模式时控制第一增强电路提供第一增强信号,并于芯片外驱动装置处于一般模式时控制第一增强电路不提供第一增强信号。

13、在本发明的一实施例中,上述的第一增强电路包括p型晶体管,其耦接于电源电压与第一电阻之间,p型晶体管的控制端耦接控制电路,p型晶体管受控于控制电路而于输入数据信号出现上升缘时被导通。

14、本发明还提供一种芯片外驱动装置的驱动能力增强方法,芯片外驱动装置包括至少一上拉驱动器、至少一第一电阻、第一增强电路、第二增强电路、下拉驱动器以及至少一第二电阻,第一电阻耦接于上拉驱动器与输入输出垫之间,第二电阻耦接于下拉驱动器与输入输出垫之间,第一增强电路耦接第一电阻,第二增强电路耦接第二电阻,芯片外驱动装置的驱动能力增强方法包括下列步骤。检测输入数据信号的上升缘与下降缘。依据输入数据信号的上升缘与下降缘控制第一增强电路与第二增强电路对输入输出垫提供第一增强信号与第二增强信号,以增强上拉驱动器与下拉驱动器的驱动信号的强度。

15、在本发明的一实施例中,上述的第一增强电路连接于第一电阻的第一端、第一电阻的第二端或第一电阻的第一端与第二端间的位置,第二增强电路连接于第二电阻的第一端、第二电阻的第二端或第二电阻的第一端与第二端间的位置。

16、在本发明的一实施例中,上述的芯片外驱动装置的驱动能力增强方法包括,依据使能信号于芯片外驱动装置处于增强模式时控制第一增强电路与第二增强电路提供第一增强信号与第二增强信号,并于芯片外驱动装置处于一般模式时控制第一增强电路与第二增强电路不提供第一增强信号与第二增强信号。

17、基于上述,本发明实施例的芯片外驱动装置可检测输入数据信号的上升缘与下降缘,并依据输入数据信号的上升缘与下降缘控制第一增强电路与第二增强电路对输入输出垫提供第一增强信号与第二增强信号,以提高输出信号的迁移率(slew rate)与输出振福(output swing),增强上拉驱动器与下拉驱动器的驱动信号的强度,提高芯片外驱动装置的驱动能力,而可改善高速传输下输出信号失真的情形,提高芯片外驱动装置的输出信号质量。

18、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

技术特征:1.一种芯片外驱动装置,其特征在于,包括:

2.根据权利要求1所述的芯片外驱动装置,其特征在于,所述第一增强电路连接于所述第一电阻的第一端、所述第一电阻的第二端或所述第一电阻的第一端与第二端间的位置。

3.根据权利要求2所述的芯片外驱动装置,其特征在于,所述驱动器电路还包括:

4.根据权利要求3所述的芯片外驱动装置,其特征在于,所述第一切换电路包括多个第一开关,分别耦接于所述第一增强电路与所述第一电阻上的对应连接位置之间,所述多个第一开关的导通状态受控于所述控制电路。

5.根据权利要求4所述的芯片外驱动装置,其特征在于,所述驱动器电路还包括:

6.根据权利要求5所述的芯片外驱动装置,其特征在于,所述第二增强电路连接于所述第二电阻的第一端、所述第二电阻的第二端或所述第二电阻的第一端与第二端间的位置。

7.根据权利要求6所述的芯片外驱动装置,其特征在于,所述驱动器电路还包括:

8.根据权利要求7所述的芯片外驱动装置,其特征在于,所述第二切换电路包括多个第二开关,分别耦接于所述第二增强电路与所述第二电阻上的对应连接位置之间,所述多个第二开关的导通状态受控于所述控制电路。

9.根据权利要求5所述的芯片外驱动装置,其特征在于,所述控制电路还依据使能信号于所述芯片外驱动装置处于所述增强模式时控制所述第二增强电路提供所述第二增强信号,并于所述芯片外驱动装置处于一般模式时控制所述第二增强电路不提供所述第二增强信号。

10.根据权利要求5所述的芯片外驱动装置,其特征在于,所述第二增强电路包括:

11.根据权利要求1所述的芯片外驱动装置,其特征在于,所述控制电路还依据使能信号于所述芯片外驱动装置处于增强模式时控制所述第一增强电路提供所述第一增强信号,并于所述芯片外驱动装置处于一般模式时控制所述第一增强电路不提供所述第一增强信号。

12.根据权利要求1所述的芯片外驱动装置,其特征在于,所述第一增强电路包括:

13.一种芯片外驱动装置的驱动能力增强方法,其特征在于,所述芯片外驱动装置包括至少一上拉驱动器、至少一第一电阻、第一增强电路、第二增强电路、下拉驱动器以及至少一第二电阻,所述第一电阻耦接于所述上拉驱动器与输入输出垫之间,所述第二电阻耦接于所述下拉驱动器与所述输入输出垫之间,所述第一增强电路耦接所述第一电阻,所述第二增强电路耦接所述第二电阻,所述芯片外驱动装置的驱动能力增强方法包括:

14.根据权利要求13所述的芯片外驱动装置的驱动能力增强方法,其特征在于,所述第一增强电路连接于所述第一电阻的第一端、所述第一电阻的第二端或所述第一电阻的第一端与第二端间的位置,所述第二增强电路连接于所述第二电阻的第一端、所述第二电阻的第二端或所述第二电阻的第一端与第二端间的位置。

15.根据权利要求13所述的芯片外驱动装置的驱动能力增强方法,其特征在于,包括:

技术总结本发明提供一种芯片外驱动装置及其驱动能力增强方法。检测输入数据信号的上升缘与下降缘。依据输入数据信号的上升缘与下降缘控制第一增强电路与第二增强电路对输入输出垫提供第一增强信号与第二增强信号。技术研发人员:吴昌庭受保护的技术使用者:南亚科技股份有限公司技术研发日:技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240731/185524.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表